利用改进的预置电流方法设计锁相环频率合成器

2012-09-28李跃华

熊 勇,李跃华

(南京理工大学电子工程与光电技术学院,南京210094)

1 引 言

在毫米波频率步进雷达中,频率合成器是雷达系统的频率源,它的好坏直接影响着雷达系统的作用距离、距离分辨率、测距精度,是雷达系统的关键部件之一[1]。频率合成器的性能指标有杂散性能、相噪性能以及跳频速度等,其中跳频时间是频率合成器的主要性能指标之一,它的大小影响着频率步进雷达的有效工作时间,因此快速跳频频率合成器能够提高频率步进雷达的性能。

目前提高锁相式频率合成器跳频速度的方法有适当增大环路带宽法、自适应锁相环技术、预置电压法[2]等。本设计分析了预置电流方法频率合成器跳频稳定性差的原因,提出了增加可控开关改进的方法,并定性分析了预置电流大小的理论值和实际值的误差,得出电荷泵电流曲线波动大的原因,利用ADS软件优化、验证,减小了波动,提高了跳频的稳定性和速度。

2 预置电流法快速锁定锁相环特点

电荷泵锁相环是由鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LPF)和压控振荡器(VCO)构成的。本设计研究的是由二阶低通滤波器构成的三阶电荷泵锁相环,三阶电荷泵锁相环的锁定时间 Tlock是关于环路带宽 ωc的函数,环路带宽越大锁定的时间越短,反之越长。环路带宽不仅影响到锁定时间同时还会影响锁相环的噪声性能,小的环路带宽能够改善带内噪声,但是以增加锁定时间为代价;大的环路带宽能够改善锁定时间,但是以恶化带内噪声为代价[3],传统的设计需要折衷选择环路带宽。

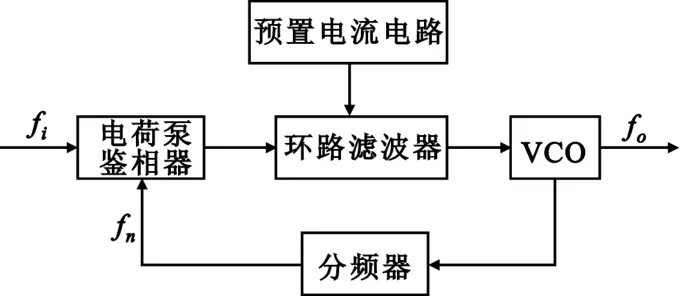

设计中采用的改进方法的基础是文献[4]中提出的预置电流方法快速锁定锁相环,其原理框图如图1所示。

图1 预置电流法快速锁定锁相环框图Fig.1 Preset-current fast-locking PLL block diagram

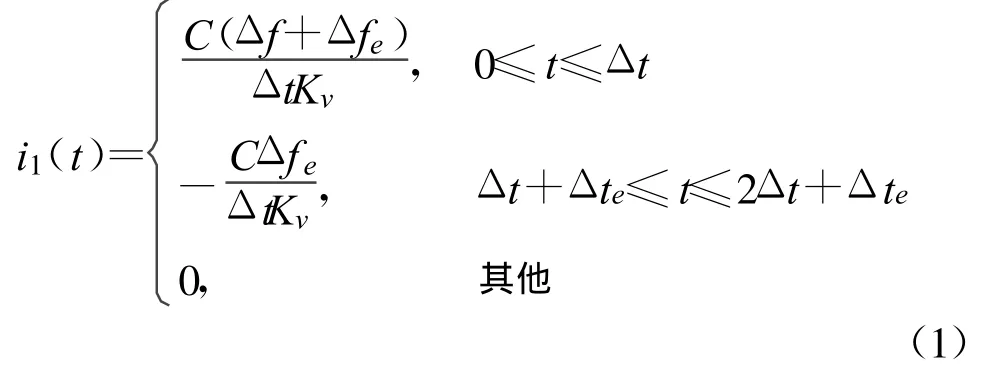

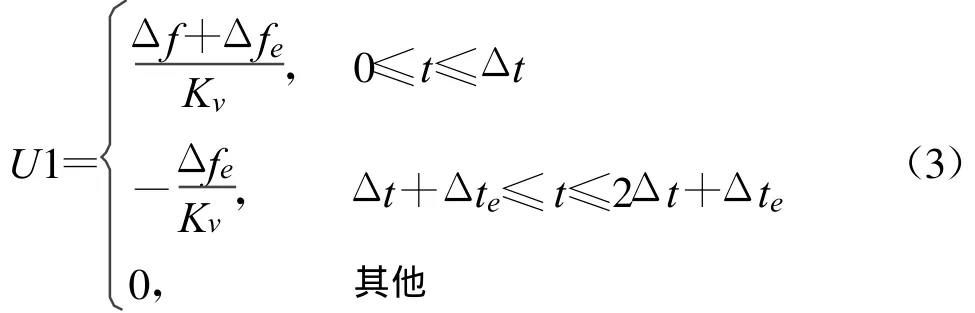

预置电流法快速锁定锁相环是在传统电荷泵锁相环电路基础上外接特定的预置电流电路(Presetcurrent circuit)来工作的。当频率发生跳变时,预置电流电路对二阶环路滤波器中的两个电容充电,预置电流的大小和作用时间是受控的。文献[4]中给出了三阶电荷泵锁相环中电容的预置电流计算式为

式中,KV是VCO的灵敏度,Δf和 Δfe分别是跳频的频差和超出锁定频率的频率值,Δt为预置电流作用时间。预置电流主要由正负电流组成,分别是对电容充电和放电,目的都在于改变电容上的电压值。电容上电流与电压的关系为

由式(1)和式(2)可以计算出环路滤波器两个电容上的等效正负电压相等,为

由式(3)可知,正电压使VCO输出频率增大Δf+Δfe,超出锁定频率Δfe的值;负电压使VCO输出频率降低Δfe,使VCO输出频率回到目标频率。

预置电流锁相环的环路滤波器上的电压主要由预置电流电路提供,与环路带宽的关系大大减小,所以这种方法能减小环路带宽对锁定时间的影响,能够在同等环路带宽条件下比传统锁相环更快锁定。对于同一个跳频频率合成器,每次步进频率是不变的,因此每次频率跳变时预置电流的大小是不变的,预置电流电路也不变,这在很大程度上方便了电路的设计。

3 预置电流法锁相环频率合成器

3.1 预置电流方法频率合成器设计

设定零时刻锁相环是锁定的,设计一个步进频率为Δf=4MHz,环路带宽取50 kHz的传统锁相环频率合成器,电荷泵电流Kd=1 mA,N=377,Kv=46MHz/V,环路滤波器的参数为:C1=506.5 pF,C2=2.664 nF,R1=3.055 kΨ。利用ADS进行仿真,在误差容限为500 Hz精度下,单步进跳频时间为43.53 μ s。

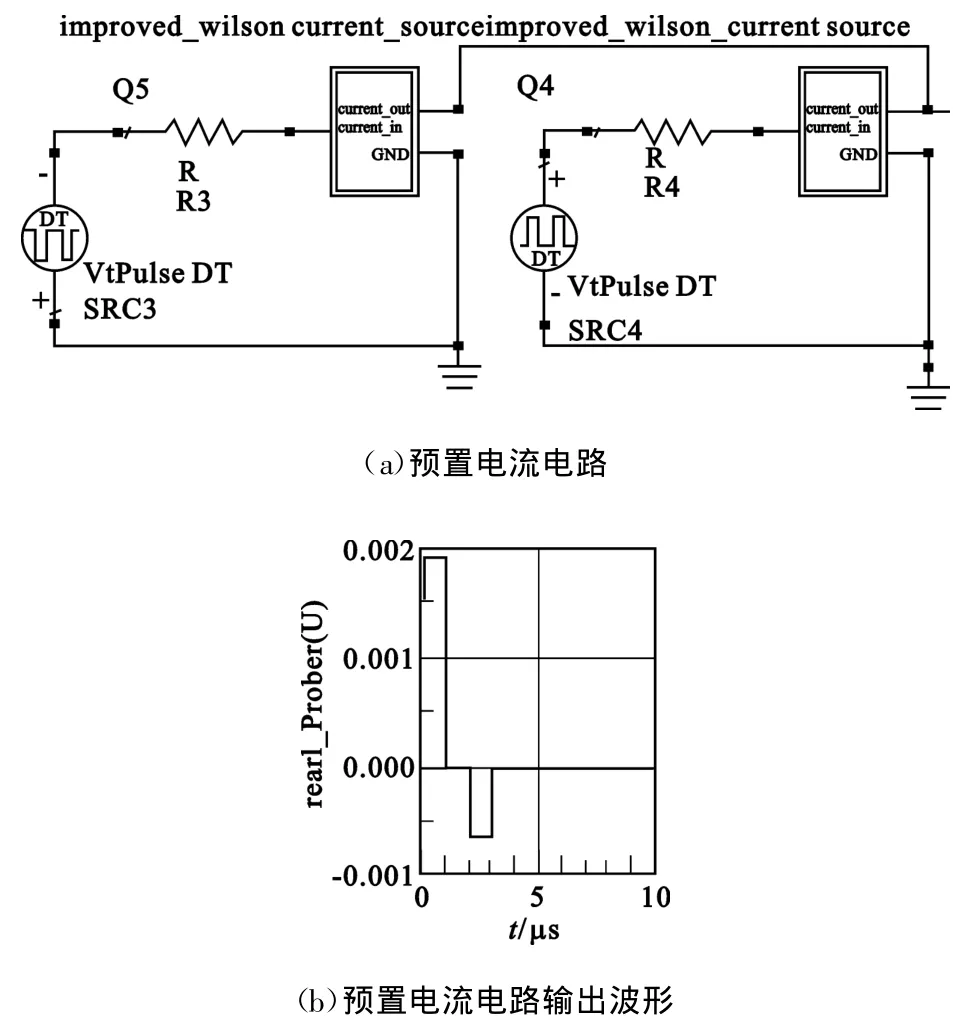

以上述传统锁相环为基础,采用脉冲电压源控制威尔逊电流源[5]的方法设计预置电流,在预置电流的时间内给电流源电路提供脉冲电压,其余时间电压为零,正负电流源分开设计。脉冲电压源采用ADS中的VtPulseDT时域电压源,为了模拟设计中电流源电路的传输延迟,将延时加在电压源上,粗略的设置电压源延时为100 ns,设置脉冲电压源脉冲周期与跳频周期相同,起始时间比跳频周期延时100 ns。

图2 预置电流电路和波形Fig.2 Preset-current circuit and waveform

将传统锁相环的参数代入式(1),并设定Δt=Δte=1 μ s,Δfe=Δf/4,即正负电流分别作用1 μ s,电压源的脉宽就为1 μ s,正负电流间隔1 μ s,计算预置电流大小。在ADS中设计图2预置电流电路,其中长方形模块为模块化的威尔逊电流源,计算图2中两个电阻,使输出得到正负目标脉冲电流。

将图2预置电流电路接入传统三阶锁相环频率合成器环路滤波器的电容上,并对电路进行包络仿真,误差容限为500 Hz,单步进跳频时间为29.95 μ s,比传统锁相环相锁定速度提高了13.58 μ s。

3.2 预置电流方法频率合成器稳定性分析

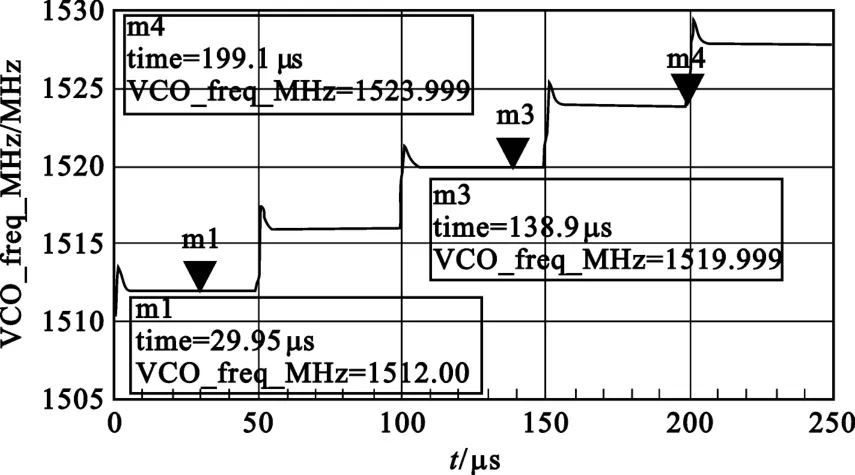

对预置电流法频率合成器进行连续步进跳频仿真,设置跳频周期为50 μ s,仿真结果如图3所示。

图3 预置电流方法连续步进跳频Fig.3 Continuous step frequency hopping with preset-current method

由图3可知,随着跳频次数的增加,跳频时间变得不稳定,到第四次跳频结束后49.1 μ s时仍未完全锁定。

分析式(1)可知,理论上预置电流完成后,预置电流电路应当与锁相环电路完全断开,但实际两者是始终连接的,环路滤波器的电容充电完成后会通过预置电流电路进行反向放电,形成泄漏电流,使电容上的电压下降,锁相环路为了保持输出相位的稳定会通过电荷泵对电容进行充电,这样持续充放电的动态过程影响了锁相环工作的稳定性,从而影响了跳频时间,这会随着跳频次数的增加而越来越严重,如图3所示。

设电容通过预置电流电路进行放电的回路阻抗是Z,那么第一次跳频完成后电容上的电压为Δf/Kv,而随着跳频次数的增加电容电压不断的提高,第N次跳频后由电容和预置电流电路形成的回路中瞬态泄漏电流i可近似表示为

图3和式(4)表明泄漏电流的影响不能忽略。

4 改进的预置电流方法频率合成器

4.1 改进预置电流电路的频率合成器设计

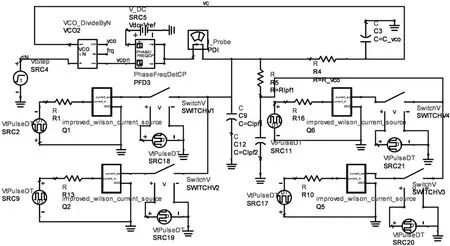

为了减小泄露电流对锁定时间的影响,在预置电流电路部分增加可控开关电路。采用ADS中的SwitchV压控开关。设置开关断开阻抗为1.0×10300MΨ,导通阻抗为0.000 1 Ψ,开关通断时间由ADS中VtPulseDT时域电压源控制,设置使开关导通时间和预置电流时间同步,如图4所示。

图4 改进的预置电流方法频率合成器电路Fig.4 Circuit with the method of improved preset-current frequency synthesizer

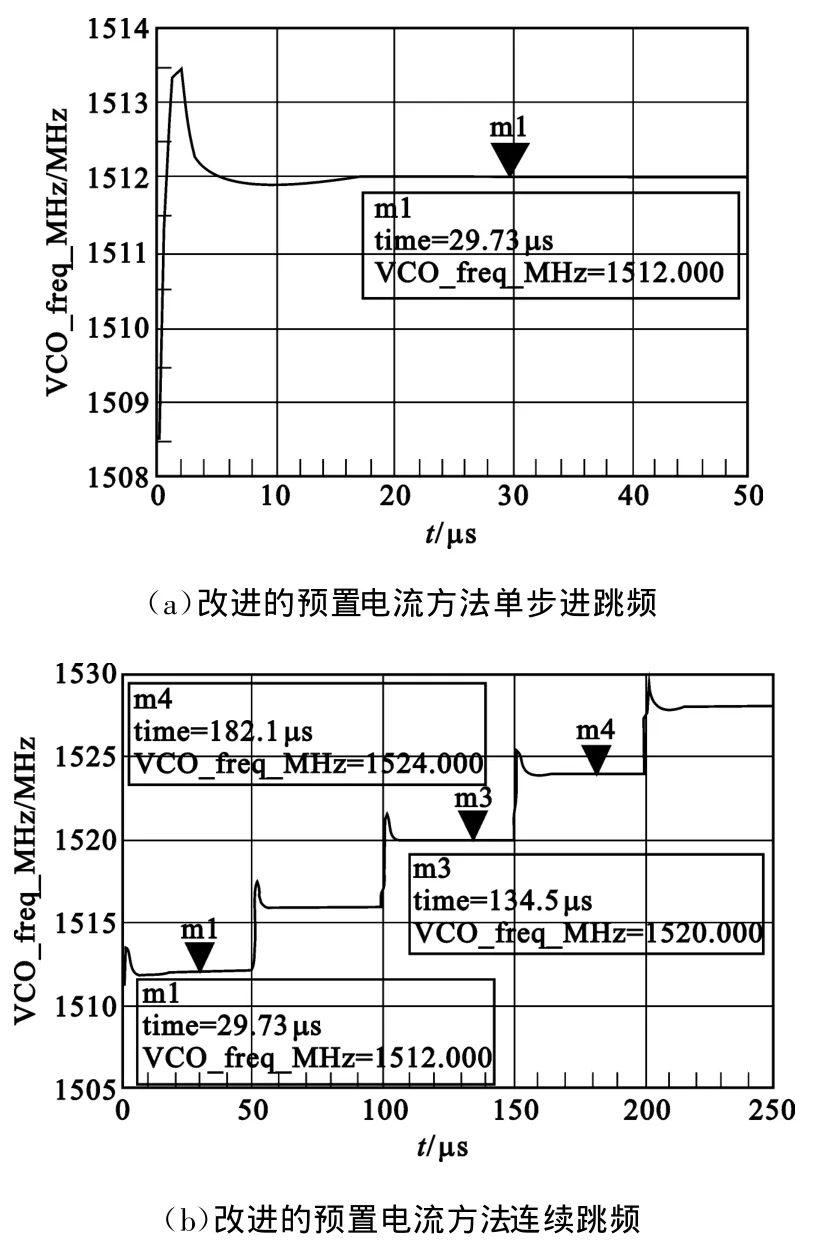

对图4电路仿真,得到误差容限为500Hz单步进跳频时间为29.73 μ s,如图5(a)所示,连续跳频时间如图5(b)所示。

图5 改进的预置电流方法跳频时间Fig.5 Improved preset-current frequency hopping time

图3的不稳定现象在图5(b)中得到改善,表明锁相稳定性得到提高,锁相时间缩短。

4.2 优化预置电流电路中电流大小

预置电流接入电路会在接入点被分流,对电容充电的实际电流不等于式(1)中预置电流大小,使电容上的电压不等于预期电压,VCO输出频率与目标频率有误差,所以锁相环的电荷泵会根据“多放少充”的原理对电路进行调节。图5(a)中预置电流作用3 μ s后VCO 的输出频率有一段高于1.512 GHz,表明VCO输入端电压偏大,即电容上总的正电流相对偏大,或负电流偏小。图5(a)对应的CP充放电波形为图6(a),图6(a)中3 μ s后电荷泵对电容放电形成负电流,以释放之前正电流充进的多余电荷量,使图5(a)中高于1.512 GHz部分的频率下降。因此可以通过保持预置正电流不变,调节两个预置负电流的大小,使负电流适当的增大来减小图6(a)中负电流的波动。调节时要确保环路滤波器两电容之间的电压差基本保持平衡,优化几次后CP的负电流波动部分得到减小,如图6(b)所示。

图6 优化前后CP电流图Fig.6 CP current before and after optimization

对预置电流值优化后的图4电路进行单步跳频和连续跳频仿真,如图 7所示,图 5(a)中15 μ s内的波动得到改善,缩短了跳频时间。

图7 优化前后跳频时间图Fig.7 Frequency hopping time before and after optimization

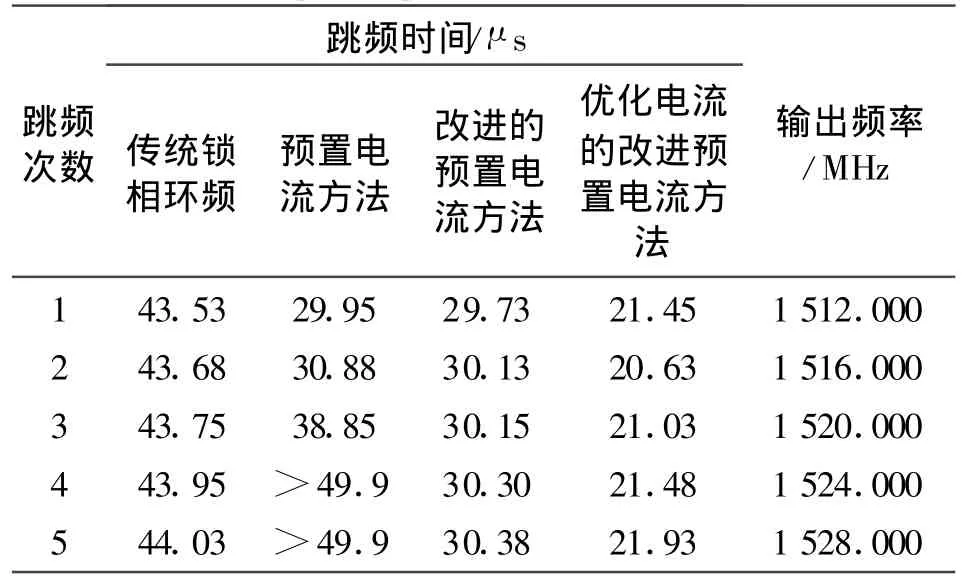

分别对各方法设计的频综进行连续5次步进跳频时间仿真,跳频周期为50 μ s,频率误差容限为500 Hz,综合结果如表1所示。

表1 各方法连续5次跳频时间及输出频率Table 1 5 Times continuous frequency hopping time and output frequency of all kinds method

由表1可知,预置电流方法的设计与传统方法的设计相比能够提高跳频速度,但由于泄漏电流的影响造成连续跳频锁定带内的锁定时间不稳定,电流优化后的改进设计显著提高了跳频稳定性和跳频速度。

5 总 结

本设计利用ADS对改进的预置电流方法频率合成器进行建模仿真,验证了改进方法的可行性。改进的方法与原方法相比,跳频稳定性和跳频速度方面的性能有了很大的提高,并且设计简单,只增加了可控开关,具有很好的工程应用前景。这种方法对于更高阶的锁相环频率合成器是否有很好的普遍适用性,这将是进一步研究的课题。

[1]蒋金水.毫米波高分辨率雷达关键技术研究[D].南京:南京理工大学,2001.JIANG Jin-shui.Study on Key Techniques of Millimeter Wave High-Range-Resolution Radar[D].Nanjing:Nanjing University of Science and Technology,2001.(in Chinese)

[2]吕波,孙江平,袁乃昌.改善锁相环跳频时间的方法研究[C]//中国电子学会微波分会、全国微波毫米波会议论文集.北京:电子工业出版社,2007,690-691.LV Bo,SUN Jiang-pin,YUAN Nai-chang.Study on Method of PLL Frequency Hopping Improving[C]//Proceedings of Micro-Wave Society Chinese Institute of Electronics and China Microwave Millimeterwave.Beijing:Publishing House of Electronics Industry,2007:690-691.(in Chinese)

[3]Roche J,Rahajandraibe W,Zaid L,et al.A Low-Noise Fast-Settling Phase Locked Loop with Loop Bandwidth Enhancement[C]//Proceedings of Circuits and Systems andTAISA Conference.Montreal,Canada:IEEE,2008:166-167.

[4]Hakkinen J,Kostamovaara J.Speeding Up an Integer-N PLL by Controlling the Loop Filter Charge[J].IEEEAnalog and Digital Signal Processing,2003,50(7):349-350.

[5]Gray P R,Hurst P J.模拟集成电路的分析与设计[M].张晓林,译.北京:高等教育出版社,2005:258-261.Gray P R,Hurst P J.Analysis and Design of Analog Integrated Circuits[M].Translated by ZHANG Xiao-lin.Beijing:Higher Education Press,2005:258-261.(in Chinese)