SDRAM在大视场TDICCD空间相机中的应用

2012-09-19金龙旭李国宁

李 进 金龙旭 李国宁 张 宇

①(中国科学院长春光学精密机械与物理研究所 长春 130033)

②(中国科学院研究生院 北京 100039)

1 引言

随着基于时间延迟积分(TDI)电荷耦合器件(CCD)成像技术的空间相机在视场和分辨率指标要求上的不断提高,导致 CCD图像数据量急剧增加[1]。为了对图像实时传输、压缩以及存储等处理需要高速大容量的存储器作为图像的缓存。现有SRAM,BRAM等存储器无法满足要求,需要开发适应空间环境的高速大容量图像缓存器。同步动态RAM(SDRAM)作为存储介质具有容量大、速度快、体积小、价格低等优点,使它成为各个领域电子系统数据缓存的首选存储介质。然而SDRAM的控制逻辑比较复杂,对时序要求也十分严格,同时还要考虑读写与刷新操作的冲突,需要设计控制器对其状态进行控制。

目前,国内外很多学者在不同的应用系统中对SDRAM控制器的设计进行了大量的研究,提出了很多 SDRM 控制策略[2]。然而这些应用场合的SDRAM控制器仅能适应于自身的工作特点。对于大视场空间相机而言,CCD输出图像数据格式不同于一般数据且各片CCD行频各不相同。另外,还要受单粒子翻转现象影响导致数据差错。通用SDRAM控制器难以满足空间相机的应用。因此,在大视场空间相机中,针对其工作特点需要进行设计专门SDRAM控制器。

本文在参考国内外相关技术的基础上,根据背景项目需求,提出了基于行使能驱动和基于仲裁策略的SDRAM控制器。重点研究了(6,8)纠错算法和RS(143,127)+RS(142,126)码纠错算法,两种纠错算法突破了传统SDRAM控制器中纠错算法为零的现状,大大提高了数据缓存的可靠性。本文提出的创新性技术已经在XX-X空间多光谱相机样机的成像系统上获得了应用,应用表明,可以有效地解决大视场TDICCD空间相机中的图像缓存要求。

2 图像缓存系统总体结构

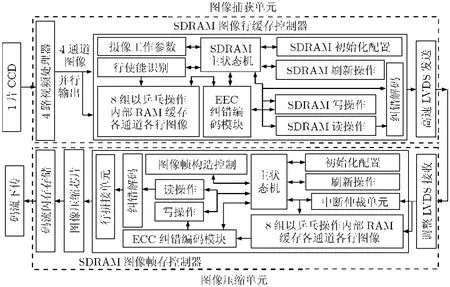

为了说明 SDRAM 在大视场遥感相机中的应用,以笔者设计的XX-X空间多光谱相机原理样机的处理1片CCD的图像缓存系统为例,系统总体结构如图1所示。在轨道高度为500 km下,CCD像元转移速率为 5.5 MHz,高速低压差分信号(LVDS)发送器并行工作时钟为55 MHz。因此需要SDRAM作为缓存。图像压缩时需要构造一帧图像,且压缩工作时钟为50 MHz。因此也需要SDRAM作为缓存。压缩码流存储和下传时,闪存读写时钟为 30 MHz,压缩码流发送器并行工作时钟为 100 MHz,因此也需要SDRAM作为缓存。可见SDRAM能否正常高效率的工作成为整个相机能否正常工作的瓶颈。

图1 图像缓存系统

CCD图像格式是以行为单位实时输出的。每行包括有效像素和消隐像素。有效像素由3000个图像数据和42个辅助数据组成。在轨工作时为了进行异速匹配消隐像素数需要进行调整,导致各片 CCD行频各不相同,但同片CCD的4通道数据行频始终相同。图像捕获单元中需要缓存4通道一行数据后输入到高速LVDS发送单元中。为了保证实时性,考虑上述特点并结合SDRAM读写特点,本文提出一种基于行使能驱动和分次存储的 SDRAM 控制器。如图1中所示SDRAM图像行缓存控制器。控制器主要包括:行使能识别、内部RAM,ECC纠错编解码等模块。各通道行使能信号有效后各通道数据先以乒乓操作的方式存入内部RAM中,然后在刷新操作的驱动下分6次读取(每次读取507个数据)RAM中的数据进行ECC编码后存入SDRAM中。为了提高数据读取的可靠性,考虑SDRAM缓存数据量相对小,但缓存输出时钟频率较高,本文采用(6,8)码纠错算法进行ECC编码。

图像压缩单元中,1片压缩芯片负责处理2片CCD图像,每片压缩芯片需要2片SDRAM缓存128行图像。2片CCD的8个通道行频不同,每行的有效像素数据是不同时到达的,本文采用仲裁策略SDRAM控制器。如图1中所示SDRAM图像帧缓存控制器。其中,中断仲裁单元包括通道中断表建立和仲裁单元。该单元主要完成负责检测不同通道的行使能信号,根据先后到的通道,把其序号存入中断表中。然后根据中断表采用分次存储和行激活仲裁处理策略将数据写入SDRAM中。本文根据该单元中SDRAM缓存数据量相对大,但缓存输出时钟频率较低,采用RS码纠错算法进行ECC编码。

3 关键技术

3.1 (6,8)码纠错算法

空间环境的辐射可能导致存储器翻转,即单粒子翻转导致差错。SDRAM缓存一行图像数据后某比特出现单粒子翻转现象时,如果没有纠错编码,将导致图像发生差错。为了提高数据单粒子翻转纠错能力,权衡纠错码算法计算速度,本文提出一种(6,8)码的SDRAM纠错算法。

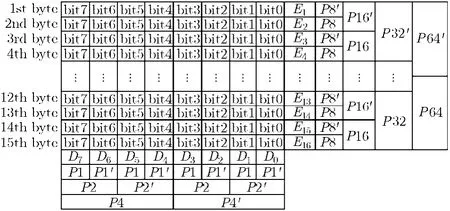

(6,8)码纠错方法是采用小步长数据范围进行纠错编码策略。本文采用每16像素数据为一组进行纠错编码。12 bit的CCD图像数据添“0”成为16 bit,将16 bit分为高字节和低字节分别进行纠错编码。这样可以把16 byte数据看成16×8的矩阵,矩阵的每个元素表示一个比特位。矩阵进行编码后分别生成6 bit的列校验信息和8 bit的行校验信息,本文称为(6,8)纠错码。(6,8)码的生成规则如图2所示。

图2 (6,8)纠错校验码生成方法

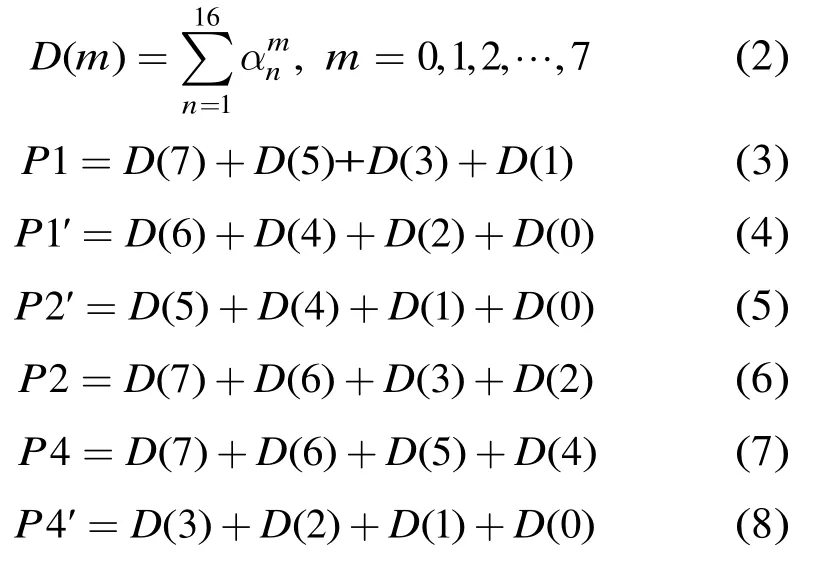

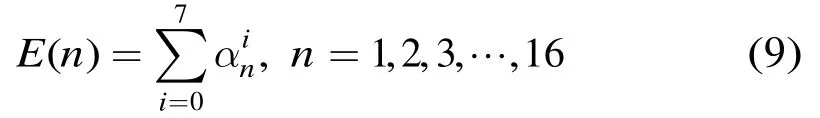

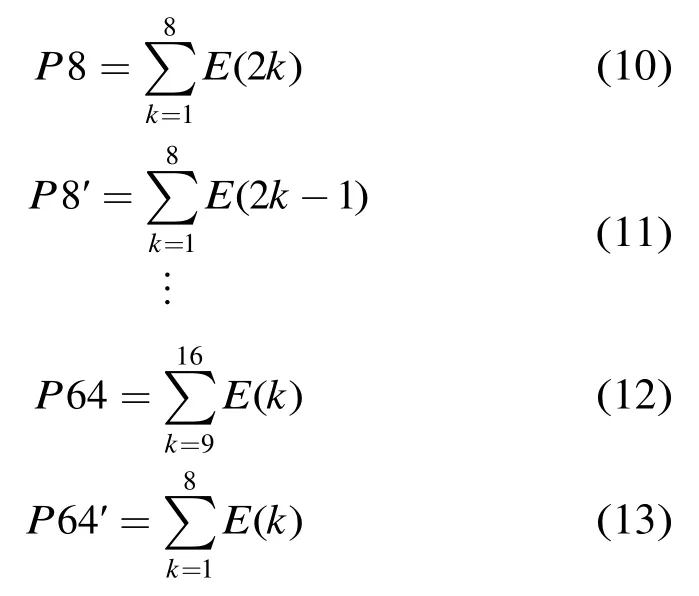

图中P1,P1',P2,P2',P4,P4'为列校验码,P8,P8',P16,P16',P32,P32',P64,P64'为行校验码。(6,8)编码算法思想为:设待输入编码器的第n字节S为

列校验码P和P'的生成计算方法为

行校验码P和P'的生成计算方法为

其中“+”表示“位异或”操作。

下面说明纠错算法如何检测错误并进行纠正。每向 SDRAM 写入 16个像素数据(以低字节为例)时,生成14 bit校验码,写入507个像素数据则生成56 byte的校验码,称为写校验码。保存到Block RAM中。当从SDRAM读取数据时,每读取16个像素数据对其进行(6,8)编码,生成14 bit校验码,称为读校验码。将从Block RAM中读出的14 bit写校验码与读校验码按位异或操作。结果会出现 3种情况:(1)全为“0”,则数据不存在错误;(2)存在 7 bit为“1”,则存在一个比特错误,且可以纠正;(3)只存在1 bit为1,则生成的校验码出错,数据本身无错;(4)其他情况则出现多个错误,不可纠正。通常空间环境会使SDRAM的某比特发生翻转,而校验码没有保存其中,因此通常会出现(1)和(2)两种情况。当出现情况(2)时,由于发生单粒子翻转的数据位在数据组中的字节偏移量为P64,P32,P16,P8。发生单粒子翻转的数据位在所处的字节中的位偏移量为P4,P2,P1。因此,根据字节的偏移量和字节中的位偏移量就可以确定数据中发生的翻转位,然后对其进行纠正。

3.2 基于RS码的纠错算法

本文提出的(6,8)纠错算法对于缓存小数据场合时,计算速度快、实现简单、纠错能力强。对于缓存大数据场合时(6,8)纠错算法生成的校验码占用内存较大,如缓存3000×128的图像时生成84 kB的校验码。本文针对缓存大数据场合提出一种基于RS(143,127)和 RS(142,126)码的 SDRAM 纠错算法。

通常RS码[3]定义为:在有限域GF(q)(q≠2)上,码长n=q-1的本原BCH码。其码元符号与生成多项式的根都是GF(q)上的元素。具有以下特性:

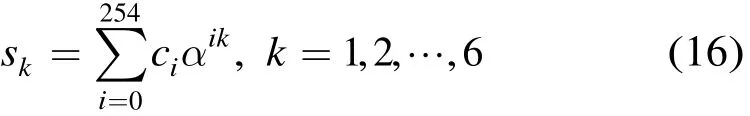

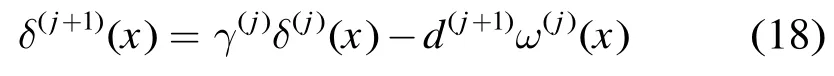

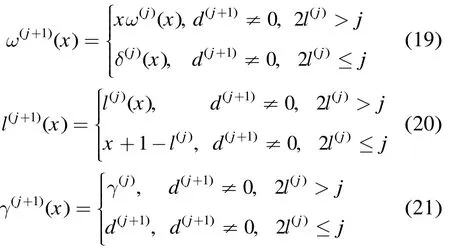

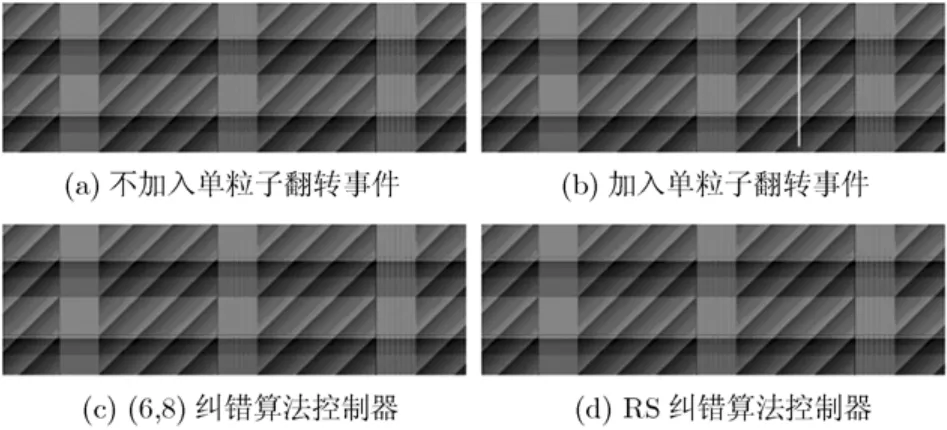

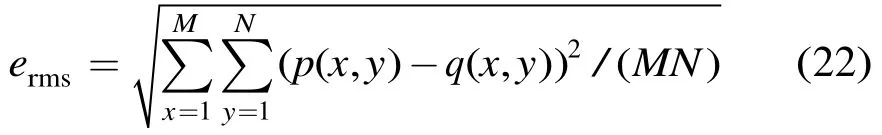

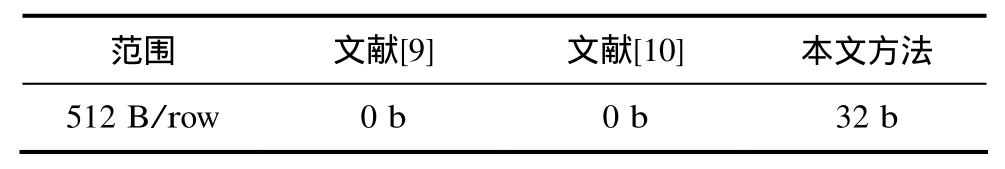

式中m为符号比特数;n为RS码长;k为信息长度;t为可纠错码元数;dmin最小码距离。此RS码是1个可在n码字上纠正t码字或更少错误的RS码。根据SDRAM(以MT48LCM16A2为例)特点及缓存图像大小要求,将SDRAM每列缓存的数据分为4块,每块的高低字节分别独立编码,前3块每块为127 B,剩余126 B作为1块。为了使纠错能力与(6,8)纠错算法相同。所以设计t1=8,待编码元k1=127,总长n1=143的RS(143,127)码,以及t2=8,待编码元k2=126,总长n2=142的RS(142,126)码。由于 27-1 RS(255,239)编码算法思想为:根据有限域性质[4]求得 GF(28)上本原多项式F(x),由F(x)求出GF(28)域的全部元素编码表。由编码表得出生成多项式为 设待输入编码器的码字多项式为D(x)(共k位),产生的校验元为R(x)(共n-k=16),则编码后码多项式C(x)可表示为C(x)=xn-kD(x)+R(x),求出R(x)便完成了编码。由于码多项式C(x)是g(x)的倍式,易得R(x)=xn-kD(x)modg(x)。 RS译码算法的整体结构图参考文献[5],这里不再赘述。RS(255,239)译码算法思想如下: (1)由输入译码器的R(x)求伴随式S(x)。设R(x),伴随矩阵S=RHT,其中,H为校验矩阵。得到伴随式系数 若采用式(16)计算任意sk要进行254次加法和255×(255-1)/2=32385次乘法,计算量较大。本文采用一种改进办法即将式(16)转换为 则乘法运算减为254次。 (2)由伴随式求错误位置多项式σ(x)和错误值多项式ω(x)。目前比较成熟的方法有:BM算法[6],Euclid算法[7]和PGZ算法[8]。PGZ算法无快速递归法,不易于硬件实现。Euclid算法需要保存大量的中间量,占用大量存储空间。BM算法是迭代算法,极大地加快了求σ(x)的速度,且易于用FPGA实现。权衡考虑速度和资源问题,本文采用BM算法并对其进行改进。 在BM算法中要用到有限域元素求逆运算,会大大增加逻辑资源用量,并使系统速度受限。所以对该算法进行改进。具体改进如下: 循环迭代:定义 以上循环迭代经过 2t(t=3)次迭代后得到σ(2t)(x)和ω(2t)(x),即为所求的σ(x)和ω(x)。改进的 BM 算法中没有用到有限域求逆运算,这样就能简洁快速地完成求解运算,能减少大量的时钟周期。 (3)通过计算σ(x)在 GF(28)中所有元素的值从而找出错误位置多项式的根,即依次将αi(0 ≤i≤254)代入σ(x)。若σ(αi)=0,则第i位出现误码,α255-i为错误位置。将错误位置α255-i和错误估值多项式ω(x)代入Forney[8]公式求出错误值ei。算出错误位置和错误值之后,错误值与对应错误位置的码元异或便可得到纠错之后的码元。 为了测试SDRAM控制器工作性能使用了主研发的地面检测设备,实验系统如图3所示。服务器向图像模拟源注入各种测试图像,图像模拟源对图像进行调整后发送至图像缓存系统。图像缓存系统为图1所示的系统,图像缓存系统对测试图像进行缓存后发送至地面相机检测设备中,地面相机检测设备进行观察图像,并进行缓存性能分析。另外,为了测试和仿真SDRAM控制器中相应模块性能,本文采用Verilog HDL设计整个SDRAM控制器和SDRAM 控制器的寄存器传输级(RTL)模型。仿真试验在 Xilinx ISE 8.2i软件平台上并调用ModelSim SE 6.1f 完成。 图3 实验系统结构 为了验证SDRAM控制器整体工作性能,图像模拟源向图像缓存系统发送自校测试图形,并加入单粒子翻转事件,测试自校图形经编码、SDRAM缓存,然后读取 SDRAM 图像、纠错译码后通过Camera Link传到PC机上,得到如图4(c)和4(d)所示,测试自校图形不加入和加入单粒子翻转事件,不经过缓存直接传到PC机上得到如图4(a)和4(b)所示。 图4 系统实验结果 取20组如图4所示的图像,并对各组图像的数码值进行比较。计算方法借鉴数学上衡量保真度的均方根误差公式: 其中p(x,y)为图4(a)数码值,q(x,y)为图4(c)和4(d)数码值,M为CCD像元数,N为扫描行数。由式(22)算得20组图像的均方根误差erms均等于0,可见SDRAM控制器可以稳定可靠的工作。 本文在SDRAM控制器中引入了提出的两种纠错算法,与目前现有SDRAM控制器纠错能力比较如表1所示。可见。本文提出的两种纠错算法可以大幅度地提高SDRAM环存储数据的可靠性。 表1 纠错能力比较 本文提出的两种控制器在Xilinx生产的Virtex-2 Pro平台的XC2VP40下进行综合得到:(1)(6,8)算法控制器 LUT占用率为:5122/38784(13%),BRAM占用率为27/192(14%); (2)RS码算法控制器LUT占用率为:8116/38784(20%),BRAM占用率为 46/192(23%)。另外,笔者针对本文提出的两种控制器进行了实际的读写强度测试,得出在SDRAM最大工作频率为133 MHz下,控制器工作频率能够达到131 MHz。在轨道平均高度下,正常工作时,设行频为f,处理通道数为n,每通道像元数为p,A/D转换位数为k,则SDRAM控制器存储数据吞吐率s为 其中k=12,p=3000,f=7.06 kHz,对于行使能驱动控制器n=4,求得s=127.08 MBps,对于仲裁SDRAM控制器由于受压缩芯片输入速率限制,只需缓存2通道的数据,即n=2,求得s=63.54 MBps。当不受限制时该控制器平均可以处理 4.4通道数据,即数据吞吐率可达到 139.788 MBps。与其他SDRAM控制器实际最大工作频率和数据吞吐率比较如表2所示。 表2 SDRAM控制器工作性能比较 本文提出的基于行使能驱动和基于仲裁策略的SDRAM控制器,提高了单行CCD图像缓存操作效率,解决了由于行频可变性导致图像缓存复杂的问题。提出的(6,8)纠错算法和RS码纠错算法突破了传统SDRAM控制器中纠错算法为零的现状,不仅计算速度快,而且不影响SDRAM操作速度,提高了SDRAM缓存数据的可靠性。结果表明,两种控制器工作频率能够达131 MHz,正常工作时,行使能驱动控制器存取速度达到127.08 MBps,仲裁策略控制器存取速度达到139.788 MBps,两种纠错算法在507 B/row内可以纠正32 b错误。基本满足空间相机中的稳定可靠、高效率的缓存图像要求。为空间相机的图像缓存提供了一种很好的解决方案。 [1]王磊,吴家骥,白静.基于整型可逆时域交叠变换的遥感图像压缩[J].光子学报,2010,39(12): 2251-2256.Wang Lei,Wu Jia-ji,and Bai Jing.Remote sensing image compression based on reversible integer time domain lapped transform[J].Acta Photonica Sinica,2010,39(12):2251-2256. [2]赵强,罗嵘,王蕙,等.用于HDTV视频解码器的高性能SDRAM控制器[J].电子与信息学报,2007,29(6): 1332-1337.Zhao Qiang,Luo Rong,Wang Hui,et al..High performance SDRAM controller design for HDTV video decoder[J].Journal of Electronics&Information Technology,2007,29(6):1332-1337. [3]Xiao Y,Luo C,and Yang C.The comparative analysis of LDPC and RS code[C].IEEE Conference on Consumer Electronics,Communications and Networks(CECNET),Xianning,China,April 2011: 4510-4513. [4]于湘珍,刘军,王秋娟.RS码在汉信码中的纠错性能分析及仿真[J].南京理工大学学报(自然科学版),2011,35(1):42-46.Yu Xiang-zhen,Liu Jun,and Wang Qiu-juan.Analysis and simulation on error correcting performance of RS code in chinese sensible code[J].Journal of Nanjing University of Science and Technology(Natural Science),2011,35(1):42-46. [5]Lee H.High speed VLSI architecture for Reed Solomon decoder[J].IEEE Transactions on Very Large Scale Integration(VLSI)System,2003,11(2): 288-294. [6]Berlekamp E R.Algebraic Coding Theory[M].New York:McGraw Hill,1968: 118-125. [7]Baek J H and Sunwoo M H.New degree computation-less modified Euclid algorithm and architecture for Reed Solomon decoder[J].IEEE Transactions on Very Large Scale Integration(VLSI)System,2006,14(8): 915-920. [8]刘悦,刘明业,尚振宏.RS(255,223)码的编译码软件实现[J].计算机应用与软件,2006,23(11): 47-49.Liu Yue,Liu Ming-ye,and Shang Zhen-hong.A software implementation of encoding and decoding for RS (255,223)[J].Computer Applications and Software,2006,23(11):47-49. [9]马灵,杨俊峰,宋克柱,等.地震数据采集中基于FPGA的多DDR SDRAM控制器设计[J].中国科学技术大学学报,2010,40(9): 939-945.Ma Ling,Yang Jun-feng,Song Ke-zhu,et al..A design of multiple DDR SDRAM controllers based on FPGA in a seismic data acquisition system[J].Journal of University of Science and Technology of China,2010,40(9): 939-945. [10]司孝平.基于SDRAM的FPGA实时图像采集系统的设计[J].西南大学学报,2011,33(1): 128-132.Si Xiao-ping.Design of an SDRAM-based FPGA real-time image acquisition system[J].Journal of Southwest University(Natural Science Edition),2011,33(1): 128-132. [11]刘正,黄战华,刘书桂.基于 SDRAM 的高分辨力高速图像缓存[J].光学仪器,2006,28(6): 49-53.Liu Zheng,Huang Zhan-hua,and Liu Shu-gui.Highresolution high-speed image buffering using SDRAM[J].Optical Instruments,2006,28(6): 49-53.

3.3 SDRAM纠错译码算法

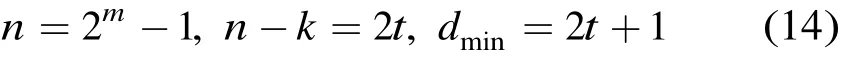

4 测试实验与结果

4.1 实验方案

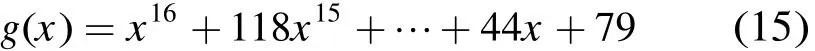

4.2 SDRAM缓存实验验证

5 结论