基于FPGA的DDS杂散分析及抑制方法

2012-09-19郑明辉

张 成,郑明辉

(江苏科技大学 电子信息学院,江苏 镇江 212003)

DDS(直接数字合成技术)是一种新型的数字频率合成技术,它具有频率分辨率高、频率切换快、频率切换时相位连续、稳定度高、可编程、全数字化、易集成等突出优点[1],因而得到广泛的应用。而FPGA器件具有高性能、高集成度的特点,使用FPGA可以设计开发出性能优良的DDS系统,成为DDS实现的常用方法。

但是,由于DDS数字化实现的固有特点,决定了其输出信号频谱杂散较大。如何抑制DDS输出频谱中的杂散就成为了研究的热点。文中总结了杂散噪声的来源,深入分析了幅度量化杂散并提出了使用FPGA实现抑制幅度量化杂散的有效方法。

1 DDS的基本原理与实现方法

1.1 DDS基本原理

DDS(Direct Digital Synthesizer)技术是一种把一系列数字量形式的信号通过高速数模转换器转换成模拟量形式的信号合成技术[2]。目前使用最广泛的一种DDS方式是利用高速存储器作为波形数据查找表,然后通过某种方式把存储的数据输出并通过高速DAC把数字形式的正弦波转换为模拟量输出[3]。

其中fc为参考时钟(常数),K为频率控制字,N为相位累加器位数;

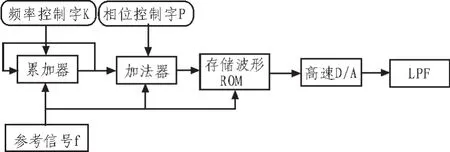

DDS的原理框图如图1所示。

图1 DDS原理框图Fig.1 DDS functional block diagram

1.2 FPGA及其特点

FPGA即现场可编程门阵列,它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点[4]。FPGA具有高集成度、高可靠性、可反复使用、配置灵活方便等特点,FPGA最大的特点是使用灵活,可以定制各种电路,并且FPGA的时钟频率可以使用分频器或锁相环修改,这给DDS信号发生器的设计带来了方便,本文即利用此特点提出了针对DDS信号发生器的幅度量化杂散的两种抑制方法。

1.3 DDS常用的实现方法(参考原理图1)

方法一:使用单片机控制频率控制字和相位控制字从而实现调频和调相,并且单片机还可以驱动显示模块作为人机界面;使用FPGA器件的高性能、高集成度的特性可以实现累加器、加法器和波形ROM并把数字形式的波形数据输出到外接的高速D/A,从而设计开发出性能优良、界面友好和便于控制的DDS系统。

方法二:方法一同时使用了单片机和FPGA,因此需要实现两者之间的通信,从而增加了复杂度并降低了系统的稳定性。因此可以只用FPGA实现简易的信号发生器,其中的频率和相位控制部分可以通过FPGA外扩按键的方法实现。

2 DDS信号发生器的优缺点分析

2.1 DDS信号发生器的优点

DDS合成信号频率切换时间短、频率分辨率高、频率切换时相位连续;可以输出宽带正交信号;输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻等优点。 在各行各业的测试应用中,信号源扮演着极为重要的作用。虽然信号源具有许多不同的类型,不同类型的信号源在功能和特性上各不相同,但是信号源中采用DDS技术在当前的测试测量行业已经逐渐称为一种主流的做法。

2.2 DDS信号发生器的缺点

DDS数字频率合成的固有特点,决定了其必然存在输出信号频谱杂散,DDS的杂散误差来源主要有以下几个方面:

2.2.1 输出频率稳定性

DDS输出频率的稳定性取决于参考时钟频率的稳定性,也就是说只要保证了参考时钟的稳定,就可以保证输出频率的稳定[2]。

2.2.2 相位截断误差

DDS的相位累加器的位数大于ROM中的寻址位数P,在寻址的时候,就只能采用相位累加器的高P位去寻址ROM中的数据,此时就会有N-P位的低位被舍去,这就造成了相位截断误差,因此,使相位累加器的位数和ROM的寻址位数相同时,就可以避免相位截断误差[2]。

2.2.3 幅度量化误差

ROM中存储值是量化值(数字值)而非模拟值,任何一个幅度值需要用无限位二进制才能精确示[5];DDS是由已抽样数字信号先经过二次抽取过程,再经过高速D/A转换及后级的 LPF重建原始信号的过程[6],其中频率控制字K对频率的调节就是基于对ROM中的数据进行的抽取,而且频率控制字K越大幅度量化误差也越大,因此幅度量化误差是数字频率合成技术固有的无法完全消除的缺点,只能通过限制频率控制字K不能太大来避免DDS出现明显失真。图2所示的是每周期抽样点数分别是6 000和12时由抽样得到的数字信号所恢复的模拟信号对比图(N代表每周期抽样点数)。

图2 抽样信号对比Fig.2 Comparison of sampling signal

从以上对比中可以得出结论:如图2中左图所示,当N的值比较大(对应频率控制字K比较小)时,DDS输出信号虽然也存在幅度量化误差,但是由于误差很小,用肉眼无法觉察出明显失真。但随着N值的减小 (对应频率控制字K增大),幅度量化误差也逐渐增大,如图2中右图所示,当N的值太小(对应频率控制字K太大)时由数字信号恢复的模拟信号会出现明显的失真,实际上随着N值的减小失真度是处在一个逐渐增大的过程,不同的频率点对应不同的失真度,实际上输出信号的失真问题主要体现在高频部分。为此文中提出以下两种改进方法:方法1的基本原理是控制频率控制字K的范围并相应地改变参考频率值,使K值范围内产生的幅度量化误差是可以接受的;方法2的基本原理是直接改变参考频率值,而累加器的递增值是固定的。

3 DDS信号发生器的抑制方法

3.1 阶梯分频法

通过以上分析,可以认为DDS的调频过程也是一个信号抽取频率逐渐变化的过程,只有当抽取频率太低(N太小)时才会发生明显失真,因此在抽取频率太低时可以提高参考时钟频率,并相应地增大一个周期内采样点数(或抽取频率)。因为参考时钟频率提高后单位时间内累加器的累加运算次数、加法器的运算次数及波形ROM内数据的抽取次数都相应的提高,如果改变时钟频率的同时降低频率控制字的大小,这样ROM内波形数据的抽取频率降低,既保证了输出信号频率连续,也有效解决了波形失真问题,对解决高频信号的失真问题有明显效果。

此方法适用于基于FPGA实现的DDS信号发生器。FPGA具有时钟频率高和方便可调的特点,在输出信号的低频段需要对时钟频率分频后可以作为DDS的参考频率,而在高频段可以很容易的通过降低分频系数来提高参考时钟频率,同时限定K值不能太大。具体做法是设定最大的频率控制字Km(保证信号不会产生明显失真),当K≥Km时,把外接时钟信号的分频系数及频率控制字K同时降为原来的n分之一即可,n的值根据实际情况而定,并且分频系数和K值可以降低多次,直到时钟频率作为DDS的参考频率为止,因此称为阶梯分频法。这样可以避免高频段的信号失真并且还可以提高输出信号的频率范围。

其中参考时钟频率fc会随K发生变化,不再是常数。

3.2 直接分频法

阶梯分频法仅能实现信号无明显失真,但在不同频率点上信号的失真度仍然是不同的,为了实现输出信号在不同的频率点上有相同的失真度,可以直接改变参考时钟的频率而让累加器的累加值为常数1,这样输出信号的每个周期都有相同数量的采样点数或量化值,失真情况也就是确定的了。

此方法也适用于基于FPGA实现的DDS信号发生器。此方法可以定义新的频率控制字M,M实际上是用来控制参考信号的分频系数。因为FPGA外接时钟信号频率可达几百MHZ,假定ROM为10位也就是1 024个量化值,那么DDS输出最高频率可达几百kHz,仍然可以满足低频信号发生器的输出频率范围的要求,而假如外接时钟信号先经过倍频后再分频,那么DDS输出信号的频率范围还可以进一步扩大,因此此方法特别适合外接时钟频率较大的情况,并且此方法可以保证高频信号也不会发生明显的失真。

其中fosc为晶振频率,K为分频系数。

4 MTALAB频谱仿真

MATLAB语言具有高效、可视化及推理能力强等特点,是工程界流行最广的科学计算语言[7],使用MATLAB可以方便的对数字信号进行仿真,MATLAB仿真是验证新理论、新方法的有效手段之一,以下是对本文提出的两种抑制DDS杂散方法的频谱仿真。

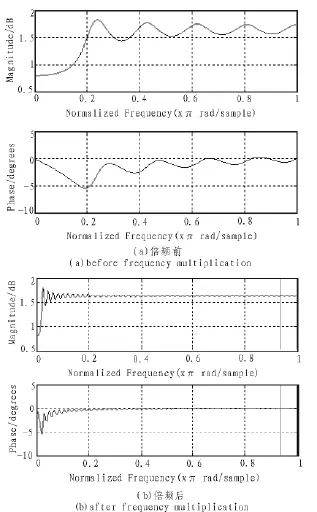

图3表示的是采用阶梯分频法的DDS信号发生器在参考时钟频率倍频前后的频谱变化情况,可以看出当输出高频信号时,倍频前幅度谱与相位谱存在明显失真,倍频后幅度谱及相位谱的失真度明显降低。

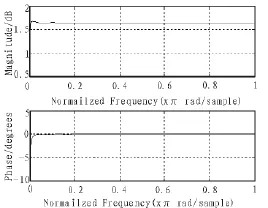

图4所示的是采用直接分频法的DDS信号发生器的幅度谱与相位谱,在不同的频率点,输出信号具有相同的频率谱和相位谱,并且频谱失真度很小或近于理想,其微弱的失真甚至可以忽略不计。

图3 阶梯分频法仿真结果Fig.3 Simulation results of ladder frequency method

图4 直接分频法仿真结果Fig.4 Simulation results of direct frequency method

5 结束语

文中介绍了DDS的基本原理与实现方法,从DDS数字化实现的固有特点出发,深入分析了幅度量化杂散带来的误差,提出了基于FPGA实现的两种幅度量化杂散的抑制方法,通过MATLAB仿真可以验证,改进方法较好的抑制了幅度量化杂散,减小了误差。

[1]夏金环.DDS工作原理及性能分析[J].中国科技论文在线,2006(5):1-4.

XIA Jin-huan.The analysis of the principle and performance of the DDS device[J].Science Papers Online of China,2006(5):1-4.

[2]刘兰坤,潘明海.DDS的杂散分析及降低杂散的方法[J].电子器件,2007(2):4.

LIU Lan-kun,PAN Ming-hai.DDS spurious analysis and improvement methods[J].Chinese Journal of Electron Devices,2007(2):4.

[3]戴逸民.频率合成与锁相技术[M].合肥:中国科学技术大学出版社,1995.

[4]徐志军,徐光辉.CPLD/FPGA的开发与应用[M].北京,电子工业出版社,2002.

[5]张丽芝,王森章.DDS波形发生器幅度量化误差的分析及其抑制[J].微处理机,2006(4):1-2.

ZHANG Li-zhi,WANG Sen-zhang.Amplitude quantization spurious analysis and improvement of DDS[J].Microprocessor,2006(4):1-2.

[6]田新广,张尔扬,罗伦,等.DDS的幅度量化杂散分析[J].无线电工程,1999(4):57-60.

TIAN Xin-guang,ZHANG Er-yang,LUO Lun,et al.Amplitude quantization spurious analysis of DDS[J].Radio Engineering,1999(4):57-60.

[7]陈怀琛,吴大正,高西全.Matlab及在电子信息课程中的应用[M].北京:电子工业出版社,2002.