半导体芯片中等离子损伤的解决方案

2012-09-19程秀兰

周 乾,程秀兰

(上海交通大学微电子学院,上海 200240)

1 引言

本课题的来源是由于在工作中有一款新产品需要采用0.18μm工艺进行制造,由于该产品附有OTP(一次可编程)存储器,套用标准的0.18μm工艺流程会引起数据保持力不足的现象。为了改善这一现象,将接触孔蚀刻阻挡层由原来的UVSIN400A+SION200A改为SIN400A。这一改动使得OTP数据保持力得到提高,但却恶化了PID。PID是重要的工艺可靠性参数,表征芯片中等离子对芯片的损伤。当芯片的关键尺寸减小到0.18μm后,栅氧化层变得更薄,对工艺缺陷的忍受力变得更低,对等离子体的损伤也变得更加敏感。PID的恶化是由于接触孔蚀刻阻挡层的改变,所以新的SIN的抗等离子体损伤能力不佳是引起PID恶化的主要原因。如何改善PID性能,使产品能够成功量产便成为我们工作中的一项重要挑战。在如何改善PID性能的研究中,我们将主要的工作聚焦在接触孔蚀刻之后的工艺即后段工艺中。研究表明在后段工艺中,通孔蚀刻及钝化层的高密度等离子体淀积会产生较严重的等离子体损伤,这两步工艺成为改善PID的切入点。首先我们了解到通孔蚀刻中产生了大量的等离子体对芯片进行物理轰击,以得到所需要的图形。在蚀刻中关闭磁场将有助于减小等离子体对芯片表面的损伤,从而改善PID的性能。另外钝化层的高密度等离子体淀积会产生较严重的等离子体损伤,由于溅射蚀刻时也会有大量的等离子体,减小溅射蚀刻功率也是改善PID的一个途径。在实验中,关闭了通孔过蚀刻时的磁场以及减小钝化层的高密度等离子体淀积时的溅射蚀刻功率,使最后的PID得到了改善,达到了产品要求。

2 现象描述

在芯片制造工艺中,通常我们都会对芯片进行PID测试,以衡量等离子体对芯片的损伤程度。首先简要说明一下PID的原理、对器件的影响以及测试方法。

PID即plasma induced damage(由等离子体引起的损伤)。在半导体制造中,任何用到等离子体的工艺都将使得MOS的性能退化,例如离子注入、光阻的灰化、氧化物的干蚀刻、高密度等离子体淀积等。由图1可知,当等离子体不断在栅氧化物上积累,产生较大的电势差,最终形成F-N隧穿电流,损伤栅氧化物。

图1 等离子体造成器件失效的原理图

PID会对器件造成很多不利的影响:

(1)增加栅氧化物的漏电流;

(2)晶体管阈值电压的退化;

(3)减小栅氧化物的生命周期;

(4)增加热电子效应;

(5)增加由器件产生的噪音;

(6)器件的不匹配以及时序的不可预知。

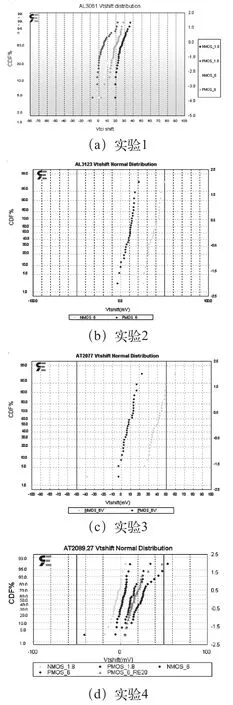

半导体制造中,在硅片的切割道上会放上一些测试图形来监控各项不同的工艺是否出于一个正常范围。对于PID的测试,如图2所示,通过两组测试图形进行监控。一个是正常的器件测试图形,另一个通过在器件上方加上一块面积较大的金属层作为天线,以此来收集等离子。通过具有天线的晶体管的阈值电压减去正常晶体管的阈值电压来监控PID的性能。ΔVT= Abs(VTof Antenna -VTof normal),当ΔVT<0.05V时,被认为PID性能可控。反之则需要改善。

图2 PID的测试图形

如图3所示,当接触孔蚀刻阻挡层用SIN400A时,这款芯片的PIDVT表现得很不稳定,有许多点超出0.05V这一上限,用SIN400A做阻挡层的PIDVT超标的概率较大,工艺容宽表现出较差的PID性能。而可靠性测试中对PID的要求是失效率为0。

图3 PID VT 趋势图

在表1中列出了不同工艺条件下PID的性能。比较得出当接触孔蚀刻阻挡层用SIN400A时,会表现出较差的PID性能。如图4所示,只有lot1的工艺容宽较大,而用SIN400A生产出的芯片都表现出了较差的PID性能。

表1 不同条件下的PID性能

图4 PID VT 分布图

当接触孔蚀刻阻挡层改为SIN时,PID的性能恶化。推测这是由于SIN的抗等离子损伤的性能不好,使得后段含有等离子的工艺对器件产生较大的损伤。另外由PID的原理可知,任何含有等离子体的工艺都会带来对器件的等离子体损伤。而在后段的所有工艺中通孔蚀刻以及高密度等离子体淀积需要大量的等离子体,于是我们将PID的改善聚焦于这两道关键工艺。

3 实验

3.1 通孔刻蚀工艺的改良

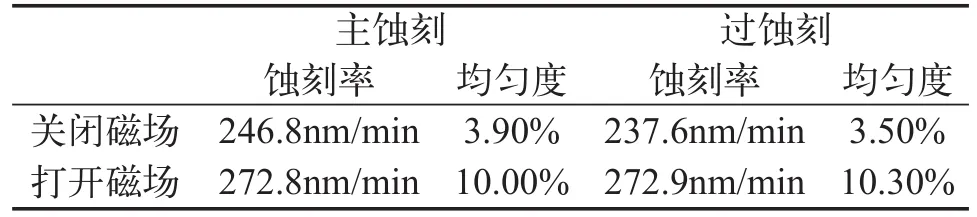

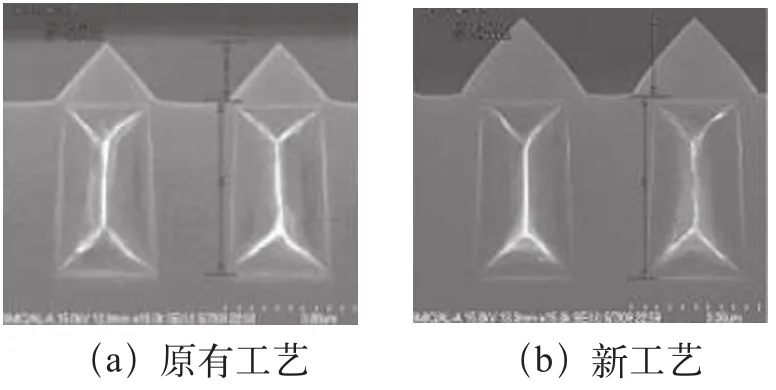

在通孔刻蚀的设备中都会有磁场存在其中,通过磁场的作用使得等离子体具有更高的能量,从而提高刻蚀的工艺能力,但是往往通过磁场加速的等离子体更加容易损伤到芯片的栅氧化层。于是想到在过蚀刻时将磁场关掉,以此来减少芯片的损伤。当开启磁场的情况下,等离子体具有更高的能量,因此它的蚀刻率会更高,而当关闭磁场时,对一片硅片进行通孔蚀刻的时间也由原来的268s增至308s,但通过切片我们可以看到改变工艺之后物理剖面是相匹配的。表2列出通孔刻蚀新旧工艺的比对,新的通孔蚀刻工艺改变了蚀刻时间并且关闭了过蚀刻的磁场,并最终使新工艺下刻蚀出的通孔与旧程式刻蚀出的通孔在物理剖面上保持相似。

图5列出了关掉过蚀刻的磁场时,工艺流程的主要改变。由于主蚀刻依然是带有磁场的,尽量减少主蚀刻的时间,然后关掉磁场增加过蚀刻的时间,最终带到与原来工艺相同的剖面。当开启磁场的情况下,等离子体具有更高的能量,因此它的蚀刻率会更高并且均匀度也变得更好,参见表3。由于一般的后段工艺中至少拥有四道通孔刻蚀,累加起来将对PID产生极大的改善。

表4为最终的通孔尺寸、通孔阻值、良率的比较,差异小于3%,与原有工艺相匹配。

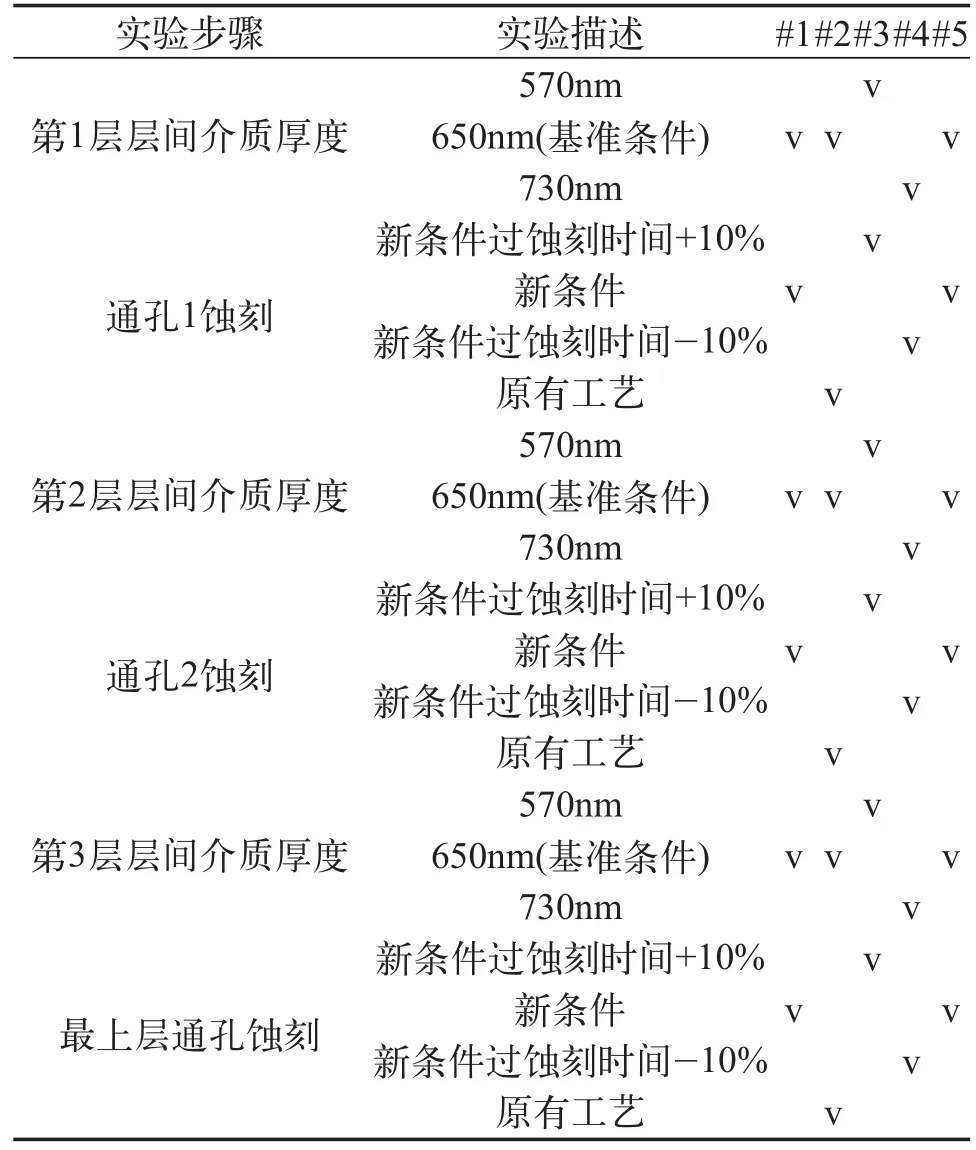

为了验证该工艺的改变是否可以适合量产的需要,设计了改变IMD厚度并结合通孔过蚀刻时间的实验,参见表5。结果证明在正常的工艺变动下,WAT(wafer acceptance test,即硅片可接受测试)中的通孔阻值与最后的良率都与原有工艺的硅片是可比的,参见表6。

表2 通孔刻蚀新旧工艺比对

图5 通孔刻蚀新旧工艺下的图形对比

表3 通孔刻蚀新旧工艺中关键工艺参数比对

表4 通孔刻蚀新旧工艺中关键数据比较

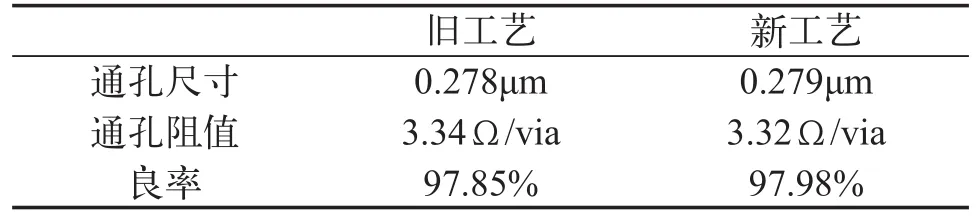

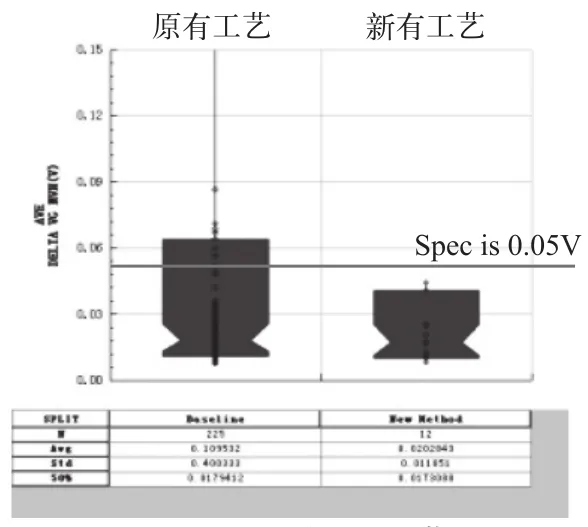

在执行了通孔蚀刻的工艺改良以后,PID得到了极大的改善。没有任何测试点大于PIDVT要求的上限0.05V,参见图6。

图6 通孔刻蚀新旧工艺下的PID结果

3.2 钝化层高密度等离子体淀积

如图7,高密度等离子体淀积使用同步淀积和刻蚀作用,用介质材料填充高深宽比的间隙并且使其无空洞形成。

表5 IMD厚度结合通孔蚀刻的实验

由于在这款芯片中最上层金属连线有3.3μm高,为达到金属间的绝缘介质可以无间隙地填充,必须采用高密度等离子体淀积的方式淀积3μm的氧化物进行隔绝。在原始工艺中通过3个淀积工艺完成钝化层氧化物的填充,每一步淀积1μm的氧化物来达到绝缘的效果。在新工艺中,保持第一步程序不变,而改变第二步与第三步的程序,这样做既可以保持原有 的隔绝性能,又可以使PID的损伤变到最小。

表6 通孔刻蚀工艺容宽的结果

图7 高密度等离子体淀积流程图

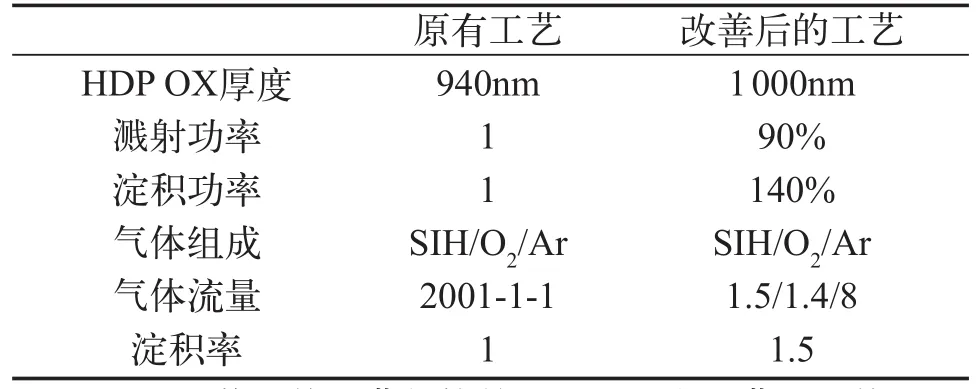

表7 钝化层高密度等离子体淀积新旧工艺比对

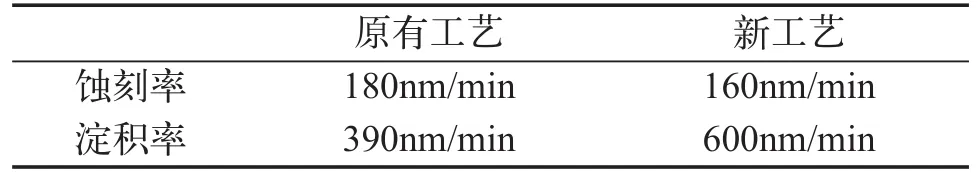

如表7所示,在新的程序中我们增加了淀积功率以及气体流量,使得淀积率得到提高,另外减小了溅射刻蚀的功率从而减小等离子体带来的对硅片表面的损伤。

表8 钝化层高密度等离子体淀积蚀刻率及淀积率比对

新的作法是先用原有的工艺淀积1μm的介质,然后用改良过的工艺进行第二步与第三步的淀积,从而改善PID性能。如图8。

图8 新旧工艺下的钝化层剖面图

最后看剖面图,优化过的工艺剖面与原有的剖面相匹配,并且在金属最小的间距中无空洞产生。通过WAT检查金属间的隔绝性能以及最后良率的比较,旧工艺良率为97.88%,新工艺良率为98.02%,金属隔绝电压同为20V,证明工艺的改变是可接受的。如图9所示,在执行了钝化层淀积工艺改良以后,PID得到了极大的改善,没有任何的测试点大于PIDVT要求的上限0.05V。

图9 钝化层高密度淀积新旧工艺下的PID结果

4 结论

半导体中的等离子损伤是芯片可靠性的一个重要考量标准,与芯片的寿命长短有着重要的相关性。本文给出了减小PID的一个新的尝试,首先通过关闭通孔过蚀刻过程中的磁场以减小在蚀刻过程中等离子体由磁场所获得的高能量,从而减少等离子体对芯片的损伤,另外减小钝化层高密度等离子体溅射刻蚀时的功率,也同样可以达到减小等离子体对芯片的损伤这一目的。最终从测试结果中可以看到PIDVT减小到了一个可控范围,从而满足了客户对芯片的可靠性要求。

[1]Michael Quirk,Julian Serda,韩郑生译.半导体制造技术[M].北京:电子工业出版社,2005.

[2]S Wolf.Process Integration,vol.2,Silicon processing for the VLSI Era[M].Sunset Beach: Lattice press,1990.

[3]T Price.Introduction to VLSI Technology[M].New York:Prentice Hall,1994.