硅通孔电镀铜填充工艺优化研究

2012-09-16李轶楠王德君魏体伟

李轶楠,蔡 坚 ,王德君 ,王 谦 ,魏体伟

(1.大连理工大学电子科学与技术学院,辽宁大连 116024;2.清华大学微电子学研究所,北京 100084;3.清华信息科学与技术国家实验室(筹),北京 100084)

集成电路的发展在过去近五十年中一直遵循着摩尔定律飞速发展,CMOS工艺已经进入了16nm节点,进一步的尺寸微缩化面临着物理的极限。为了满足电子系统产品的高性能要求,超越摩尔定律以及系统集成与系统封装成为了新的半导体发展技术路线,从技术和产品应用上得到了越来越多的重视,以硅通孔(Through Silicon Via,TSV)互连为特征的三维集成封装技术正在成为其中备受关注的新技术[1,2]。

由于铜具有高导电率、与传统多层互连技术兼容等优点,因此铜被广泛的用作硅通孔填充材料[3]。电镀工艺作为最合适的硅通孔填充技术而受到人们的普遍关注[4],硅通孔填充又分为盲孔填充和通孔填充两种方法[5]。然而,若想获得良好的铜填充却面临着种种困难与挑战,目前影响铜填充的主要问题包括:硅通孔内侧壁种子层的覆盖[6]、硅通孔内气泡的排除、电镀液质量以及电镀电流密度等,其中硅通孔内气泡的排除是非常难以解决的问题。

对于TSV中的高深宽比需求的Cu电镀填充,研究人员已经采取了多种方案进行优化,例如采用正负脉冲电流、优化电镀槽结构以及改变电流密度等[7,8,9]。尽管这些方法已经在优化铜填充问题上取得了很大的进展,但对于如何彻底消除硅通孔内气泡仍存在一些需要解决的问题,电镀过程的前处理对于电镀填充也会产生重要的影响。本文首先在实验基础上选定一种优化的电镀液,并在种子层覆盖相同条件下确定了硅通孔电镀的最佳电流密度,之后在以上各参数均相同的条件下,通过改变电镀前处理工艺,最终电镀获得了无孔洞的铜填充。

1 铜填充工艺流程

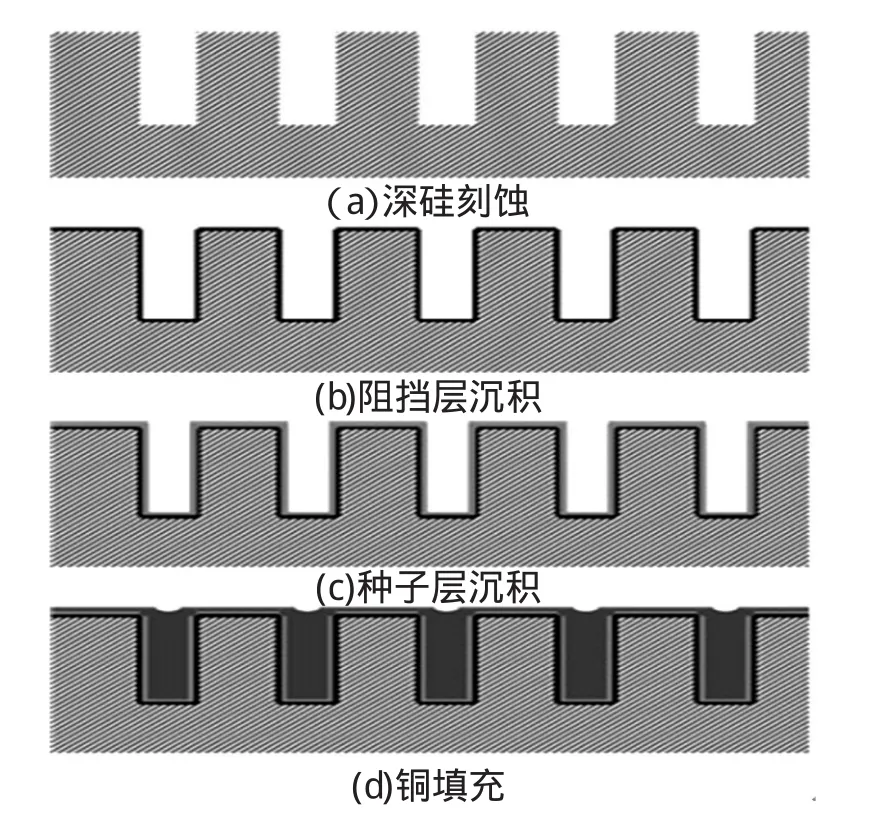

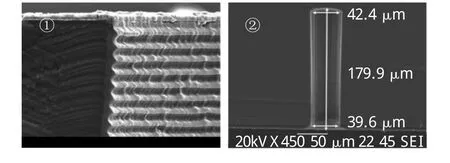

如图1所示,典型的硅通孔铜填充工艺流程包括深硅刻蚀、阻挡层与种子层沉积以及电镀铜。本论文涉及到的孔径40μm、孔深180μm的硅通孔就是基于此工艺流程制作完成。

图1 硅通孔铜电镀填充工艺流程图

1.1 硅通孔制作

在硅通孔的制作过程中,首先利用STS HRM刻蚀设备对硅片进行深硅刻蚀。由于该设备刻蚀光刻胶的速率远远低于刻蚀硅的速率,因此本文选用光刻胶作为深硅刻蚀的掩膜材料。

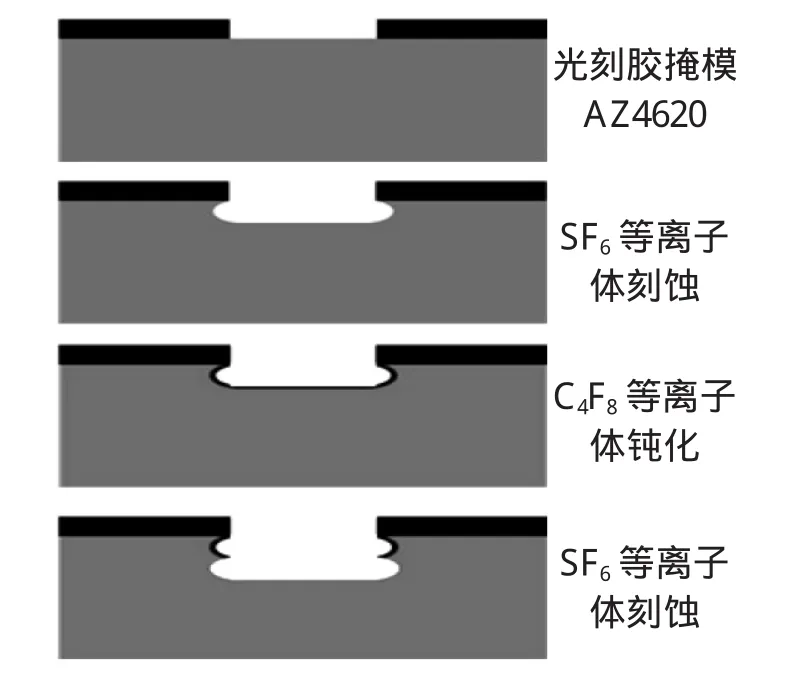

STS深硅刻蚀工艺过程中利用了Bosch刻蚀原理。如图2所示,一个标准的Bosch工艺循环包括选择性刻蚀和钝化两个步骤,其中选择性刻蚀过程利用的是SF6与O2气体,钝化过程利用的是C4F8气体[10]。

图2 硅通孔刻蚀Bosch工艺原理图

在深硅刻蚀Bosch工艺过程中,首先利用SF6等离子体刻蚀硅衬底,接着利用C4F8等离子体作为钝化物质沉积在衬底上面,在这些气体中加入O2等离子体能够有效地控制刻蚀速率与选择性。因此,在Bosch刻蚀过程中很自然的形成了贝壳状的刻蚀侧壁,在图3①中可以清晰的看到。

图3 刻蚀侧壁扫描电镜图

在深硅刻蚀过程中,光滑垂直的刻蚀侧壁有利于种子层的均匀覆盖,能够提高硅通孔电镀铜填充率。因此为了降低贝壳状刻蚀侧壁的粗糙度及获得垂直侧壁在深硅Bosch刻蚀的一个循环过程中,设置刻蚀时间为5s,钝化时间为3s,刻蚀与钝化过程不断交替进行。经过一系列的探索实验,最终确定了合适的Bosch工艺参数。具体的工艺参数如表1所示。

表1 Bosch工艺参数

接下来继续阻挡层与种子层的制作,首先采用热氧的方法在孔内侧壁上制作绝缘层SiO2,SiO2厚度为500nm。然后利用Kurt J.Lesker磁控溅射设备Lab-18在孔内侧壁上沉积阻挡层与种子层,阻挡层为200nm的TiW,种子层为500nm的铜。

1.2 孔内电镀铜填充

TSV的电镀可以有不同的技术路线与电镀体系,本论文中采用的是盲孔电镀技术路线,电镀液由上海新阳半导体材料有限公司提供,属于甲基磺酸电镀体系。

在硅通孔电镀铜填充的过程中有很多的影响因素,例如孔的密度、孔的直径以及孔的深度等[11]。但是对于具有确定硅通孔参数的铜填充,电镀过程中电流密度以及电镀前处理工艺变得尤为重要。电镀前处理工艺能够有效地去除孔内的气泡,保证了硅通孔电镀铜的填充率。

1.2.1 电流密度对铜填充的影响

在硅通孔铜填充的过程中电镀电流密度起到了至关重要的作用。本论文采用的电镀电流密度为平均电流密度ASD,单位A/dm2。本文对不同电流密度的电镀样品进行了详细分析,这些样品种子层覆盖参数相同并使用了同一款电镀液,研究发现当电流密度不断增加时,硅通孔的铜填充速率不断增加,由于铜填充的生长机理为由侧壁向中间生长。因此随电流密度增加,孔口处的电流密度快速增大导致孔口处的铜率先填充满,导致孔底部不能继续填充而形成空洞。

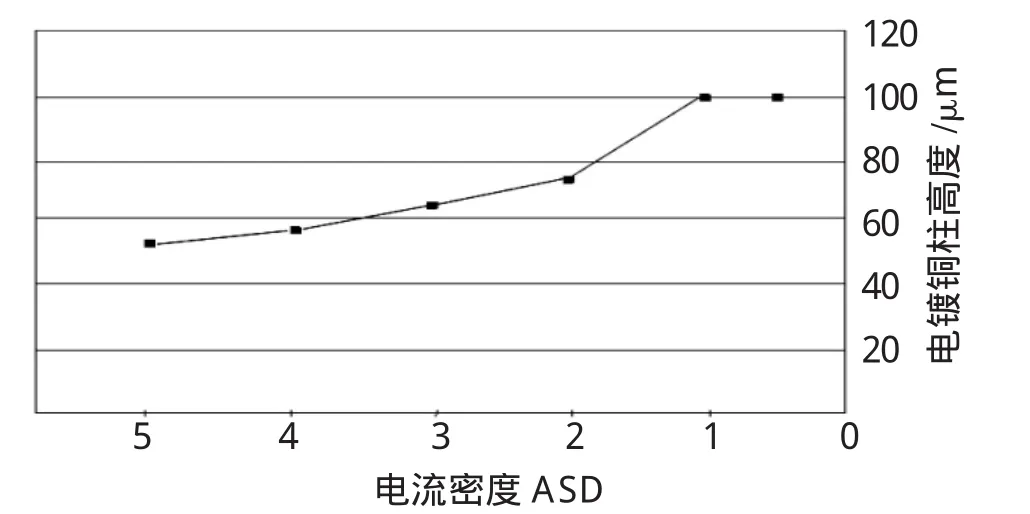

图4给出了硅通孔电镀铜柱高度随电流密度变化的曲线图,由此可得出的结论是随着电流密度的不断减小,硅通孔电镀铜柱高度不断增加,但当电流密度达到一定值并继续减小时电镀铜柱高度不再增加。因此还存在其他的原因制约着铜填充率。经过一系列对比试验,最终确定孔径40μm、孔深180μm的硅通孔优化电镀电流密度为1ASD。在后续研究其他因素时均采用该电流密度。

图4 不同电流密度下的铜填充

1.2.2 电镀前处理对铜填充的影响

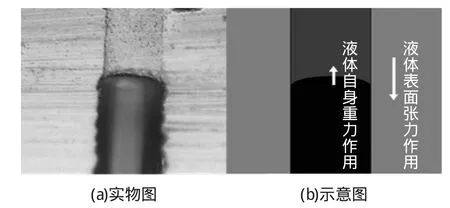

对电流密度为1ASD条件下的电镀铜填充观察发现,底部铜柱的表面向内凹陷,如图5所示。造成此现象的原因是当电镀液进入硅通孔时,孔内存在未排出的气体,液体与硅通孔侧壁张力作用大于液体自身重力作用,使得电镀液在硅通孔内液面向内凹陷。因此电镀时孔底部存在气泡的原因导致孔底部未能填充满。于是采用不同的前处理工艺进行处理以排除孔底部的气泡。

(1)超声清洗

图5 硅通孔电镀铜填充底部效果图

首先将电镀的硅片固定于阴极靶上,

然后将阴极靶垂直放入盛有去离子水的容器内,将容器放入超声设备中进行超声清洗,在超声清洗过程中不断同方向匀速旋转阴极靶,这样有利于孔内气泡的排出。超声清洗完毕后立刻将阴极靶放入电镀槽内,扩散10m in之后开始电镀。

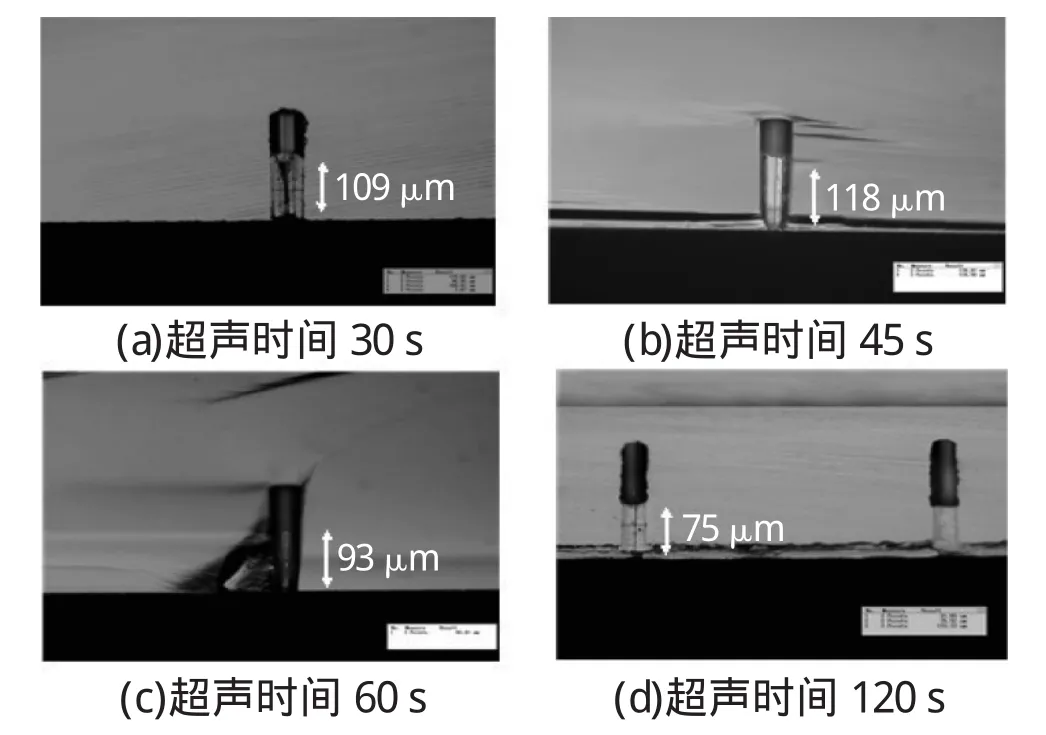

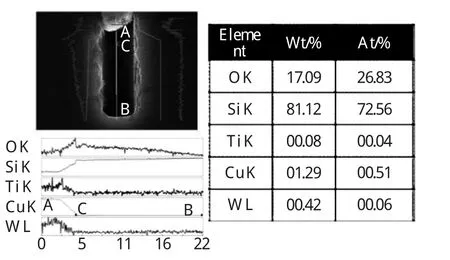

图6为不同超声时间下的铜填充效果图,与1ASD电流密度下未做任何前处理的铜填充(铜柱高度100μm)相比,超声时间为45s的电镀铜柱高度有小幅度增加,随着超声时间的继续增加电镀铜柱高度不断下降。图7为超声60s硅通孔底部的EDX分析,扫描的范围为从A点至B点,C点的Cu含量由图7内的表格可知为1.29%。如此低的Cu含量导致了C点Cu未能电镀上。由此分析可知超声清洗会对多层薄膜的结合力产生不利影响,破坏了硅通孔内底部的种子层。因此电镀前处理工艺不宜采用超声清洗。

图6 不同超声清洗时间下的铜填充效果图

(2)去离子水冲洗

图7 硅孔铜填充EDX分析图

首先将电镀的硅片固定于阴极靶上,然后利用去离子水枪对硅片表面进行冲洗,水流与硅片表面之间的夹角保持45°不变,以利于孔内气泡的排除。冲洗完毕后立刻将阴极靶放入电镀槽内,扩散10m in之后开始电镀。

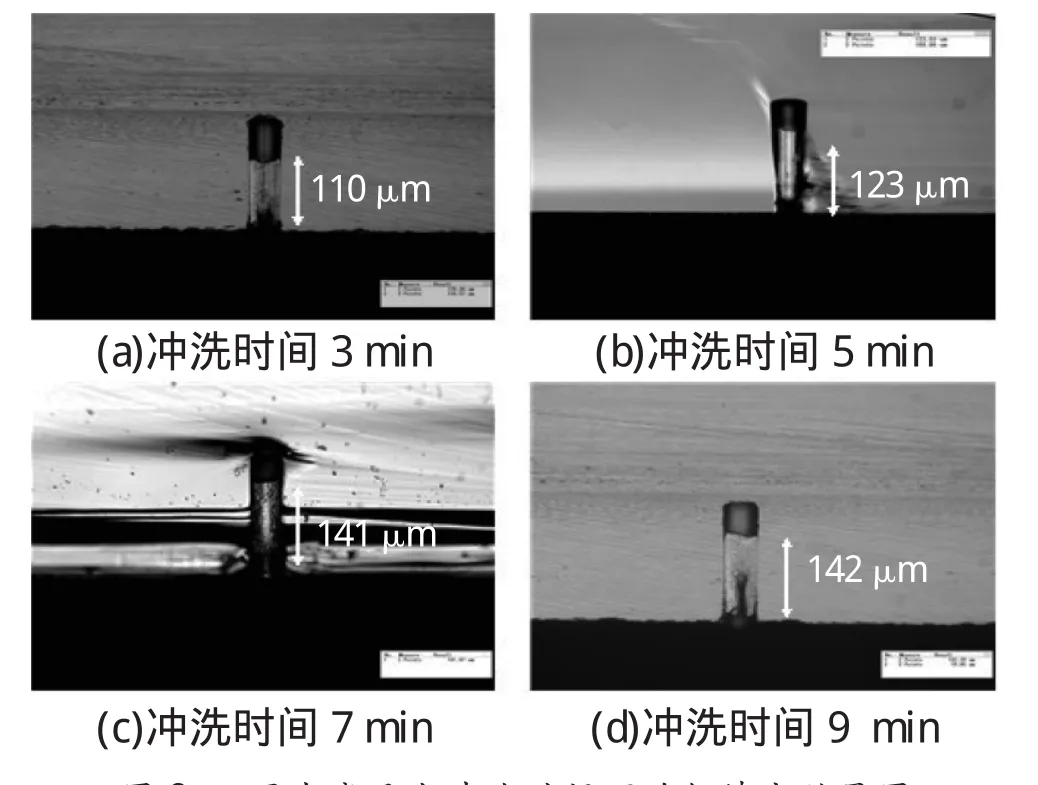

图8所示为不同去离子水冲洗时间下的铜填充效果图,与1ASD电流密度下未做任何前处理的铜填充(铜柱高度100μm)相比铜柱高度有了一定的增加。且铜柱高度随着冲洗时间的增加不断增加,当冲洗时间达到一定值后,继续增加冲洗时间电镀铜柱高度将不会被进一步提高。

图8 不同去离子水冲洗时间下的铜填充效果图

(3)真空预处理

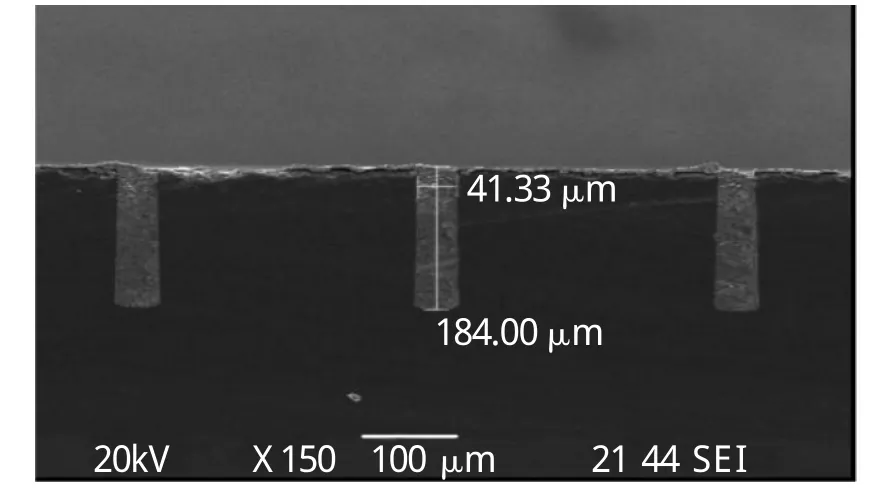

首先将电镀的硅片放入盛有电镀液的容器内,电镀液表面高于硅片表面5cm,以此保证在真空预处理的过程中硅片表面不会露出液体表面。然后将容器放入真空设备内进行真空预处理,真空预处理结束后将硅片取出立刻固定于阴极靶上,将阴极靶放入电镀槽内进行电镀。铜填充效果图如图9所示,铜填充率接近100%。由此得出结论,抽真空预处理能够有效将硅通孔内的气泡排出,使得电镀液能够填满硅通孔,进而获得良好的铜填充。

图9 真空预处理下的铜填充效果图

2 结 论

论文获得了直径为40m、孔深为180m的硅通孔制备和铜填充的优化参数,硅通孔电镀铜填充优化电流密度为1ASD。在此电流密度下,采用超声清洗与去离子水冲洗能够改善硅通孔电镀铜填充,但改善的效果有限。且超声清洗会破坏硅通孔内底部种子层,故不宜采取。利用真空预处理的方法能够有效的改善硅通孔电镀铜填充,使的铜填充率接近100%。

3 致 谢

本研究得到了国家科技重大项目(No.2009ZX02038)的支持,同时论文中部分实验得到了中科院苏州纳米研究所纳米加工平台的设备支持,作者同时感谢上海新阳半导体材料有限公司为本研究提供的电镀液及对电镀实验上的技术支持。

:

[1]R.Chanchani.3D Integration Technologies An Overview[C].Materials for Advanced Package,2009:13-17.

[2]International Technology Roadmap for Sem iconductor[EB/OL].http://www.itrs.net/Links/2009ITRS/Home2009.htm Edition,Interconnect chapter,2009:2-9.

[3]Kam to Tegueu,AlphonseMarie.Fabricationand reliability testing of copper-filled through silicon vias for three dimensional chip stacking applications[D].Doctor dissertation of the University of Alabama,2010:7-8.

[4]J.J.Sun,K.Kondo,T.Okamura,etal.High aspect ratio copper via filling used for three dimensionalchip stacking[J].J.Electrochem.Soc.2003,150(6):355-358.

[5]Rozalia Beica,Charles Sharbono,Tom Ritzdorf.Copper Electrodeposition for 3D Integration[R].Design,Test,Integration and Packaging of MEMS/MOEMS,2008:127-131.

[6]F.Inoue,T.Yokoyama,S.Tanaka,K.Yamamoto and S.Shingubara.Addition of PEG-Thiol to Cu Electroless Plating Bath for Realizing PerfectConformal Deposition in Through-Si Via Holes of 3-D Integration[R].216th The Electrochemical Society Meeting,Austria,October.2009:31-36.

[7]C.Song,Z.Wang,Q.Chen,J.Cai,and L.Liu.High aspect ratio copper through silicon vias for3D integration[J].M icroelectronic Engineering,2008(85):1952-1956.

[8]B.Kim,C.Sharbono,T.Ritzdorf,and D.Schmauch.Factors affecting copper filling process w ithin high aspect ratio deep vias for 3D chip stacking[R].Proc.Electronic Componentsand Technology Conference,2006:838-843.

[9]S.Spiesshoefer,J.Patel,T.Lam,R.Figueroa,S.L.Burkett,L.Schaper,R.Geil,and B.Rogers.Copper electroplating to fill blind vias for three-dimensional integration[J].Journal of Vacuum Science&Technology A:Vacuum,Surfaces,and Films,Jul.2006,24(4):1277-1282.

[10]N.Ranganathan,Liao Ebin,Linn Linn.Integration of High Aspect Ratio Tapered Silicon Via for Through Silicon Interconnection[R].Electronic Components and Technology Conference,2008:859-865.