QPSK中频全数字解调器的研究与FPGA实现

2012-09-12张钰磊姜生瑞

张钰磊,姜生瑞

(兰州交通大学电子与信息工程学院, 甘肃兰州 730070)

0 引言

随着通信技术的飞速发展,模拟通信系统已在实际应用中逐渐消失,数字移动电话GSM、CDMA网络系统已经取代了模拟蜂窝移动通信系统,数字电视广播系统正在中国快速发展,模拟电视正处在被淘汰的边缘。第三代移动通信系统(3G)、高清晰度电视(HDTV)和互联网这些通信系统都采用的数字通信。

在无线通信中,QPSK调制方式因其具备高效率、低误码率、频谱性能好等特点被广泛应用于商业和军事通信系统中。但是现在的数字通信系统并没有实现全数字化。在传统的通信系统中,从发射机调制器开始到接收机解调器,系统调制部分和解调部分所传送的信号、采用的器件都是模拟的,只有信号处理部分是数字的。因此,对QPSK中频全数字解调器的研究就具有划时代的意义。

1 QPSK中频全数字调制解调基本原理

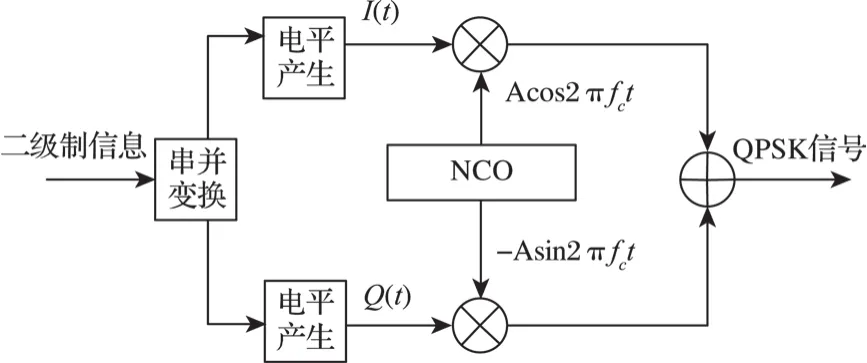

1.1 QPSK调制系统

QPSK调制器的原理方框图如图1所示。输入信号为串行的二进制信息,经过串并变换分成两路序列,这两路序列的速率都会减半。经过电平发生器产生双极性电平信号I(t)和Q(t),然后对cos(t)和sin(t)来进行调制,相加后即可得到QPSK信号。QPSK正交调制信号为:

图1 QPSK调制器的原理方框图

式中an,bn分别表示调制的二进制信息,ang( t) cos wct为同相分量, bng( t) sin wct为正交分量。

多相位数字调制通常表示为M进制相移键控[2](MPSK)。在M进制相移键控信号中,M指的是M种不同的载波相位,对应M种持续时间为Ts的不同符号。与二进制调制2PSK相比,MPSK具有两个特点[3]:

(1)同一码元速率的传输系统,MPSK比2PSK信息传输速率高,正交相移键控(QPSK,Quadrature Phase Shift Keying)是2PSK信息传输速率的2倍。

(2)同一信息速率的传输系统,MPSK比2PSK码元速率低,由奈奎斯特定理知,MPSK比2PSK码间干扰小。

在实际中,应用较多的是QPSK调制方式,也叫作四进制相移键控。

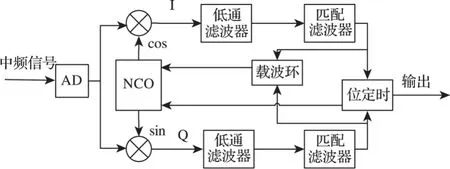

1.2 QPSK解调系统

中频(Intermediate Frequency)按其在电路中的位置与作用来划分时,中频信号是指高频信号经过变频而获得的一种信号。为了使放大器能够稳定的工作和减小干扰。一般的接收机都要将高频信号变为中频信号。

QPSK正交解调器方框图如图2所示。全数字解调器[5]包括数字下变频、匹配滤波器、载波同步和位同步这几个主要模块。全数字解调器的工作过程[6]为:接收到的中频信号经过AD转换器后为输入信号,它与NCO产生的cos(t)和sin(t)信号混频,下变频解调出IQ两路同相分量和正交分量, 经过低通滤波器滤除高频分量,得到低频信号。低频信号通过匹配滤波器,由于匹配滤波器采用平方根升余弦函数,能够平滑的滤波,同时这里的匹配滤波器和调制时的成型滤波器参数都相同,所以能保证码元干扰降到最低。载波环主要完成载波同步的功能,从匹配滤波器输出经过非线性变换检测出载波频率误差,然后输入到NCO进行调整。位定时主要完成位同步的功能,从匹配滤波器输出经过非线性变换检测出鉴相误差,然后输入到NCO进行调整。

图2 QPSK正交解调方框图

2 数字下变频及匹配滤波器

2.1 数字下变频及匹配滤波器的FPGA实现

数字下变频模块实现将中频信号的频带搬移,解调出基带信号。数字下变频器的FPGA实现包括NCO模块、数字混频模块、低通滤波器模块,匹配滤波器由匹配滤波器模块组成,这里和数字下变频器一块完成实现。

下变频模块及匹配滤波器模块整体的FPGA实现框图如图3所示。

图3 下变频实现框图

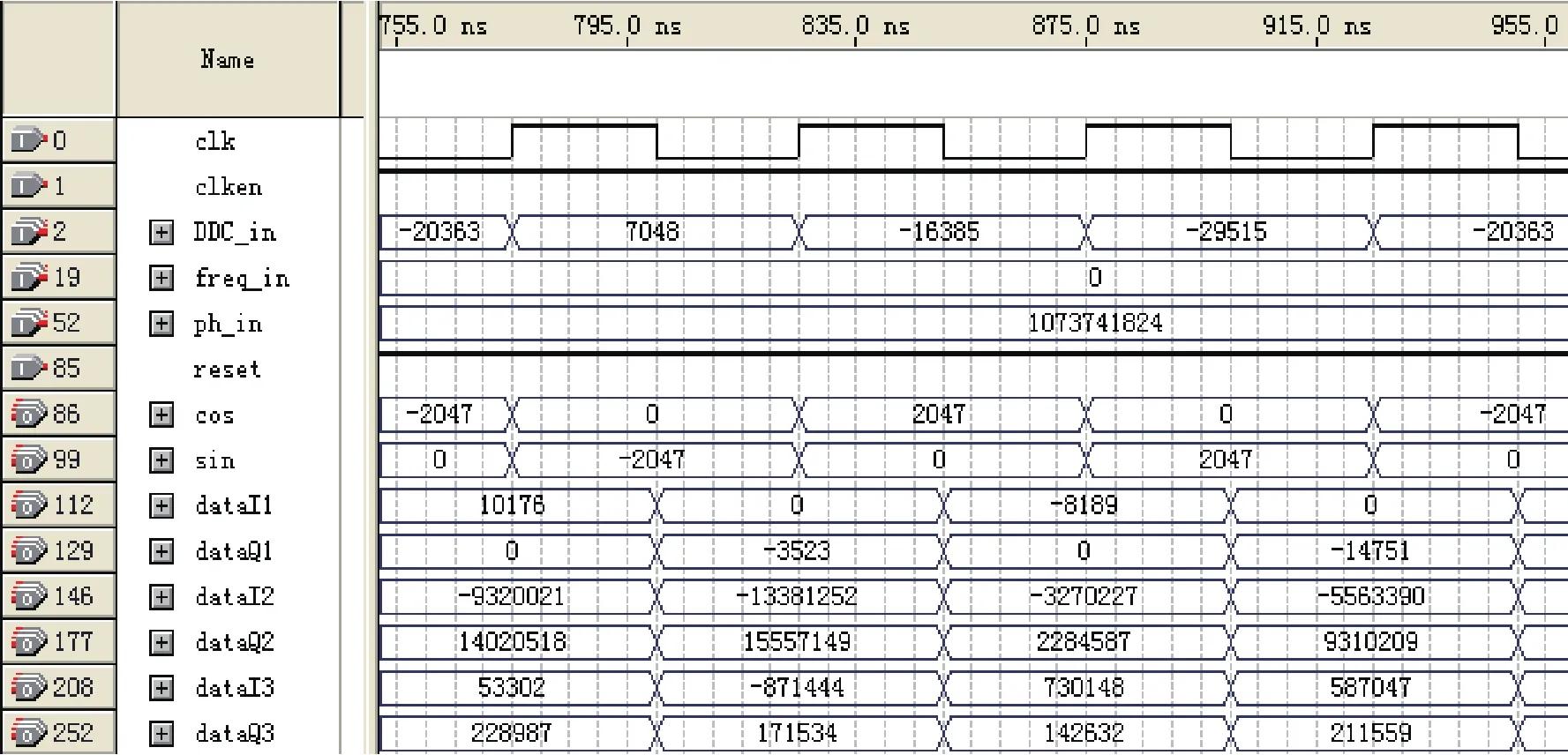

下变频模块的工作过程:

(l)控制信号:clk是系统工作的时钟,经过分析后本文采用周期为50ns的时钟信号。clken是时钟使能信号,当为clken高电平时,模块才能处于工作状态。reset是系统复位信号,当为reset低电平时,该模块停止工作,当reset为高电平时,则才开始工作;

(2)产生信号:调用 Quartus II 9.0中自带的NCO的IP核,设置NCO的初始频率控制字ph_in为2的30次方即1073741824,设置调频接口输入freq_in为0。其中,NCO相位累加器是32位,输出数据取12位量化位数,截取相乘结果的16位。输入信号DDC_in与NCO产生的余弦信号cos和正弦信号sin与进行混频相乘,得到两路数据 dataIl和dataQ1;

(3)低通滤波:调用低通滤波器的IP核,将MATLAB中用FDA工具仿真输出的低通滤波器的参数导入到调用的IP核中,设置低通滤波器参数位宽是12位,输入信号为16位。下变频后输出的数据dataIl和dataQ1在经过低通滤波器输出数据dataI2和dataQ2;

4)匹配滤波:调用升余弦滤波器的IP核,设置升余弦滤波器输入信号为16位,匹配滤波器输出数据dataI3和dataQ3。

利用Quartus II 9.0自带仿真工具对模块进行综合以及功能仿真之后,仿真结果如图4所示。

2.2 数字下变频及匹配滤波器的MATLAB仿真

数字下变频模块实现将频率为20 MHz的中频信号的频带搬移和滤波,生成一个基带信号[7]。数控振荡器NCO与输入的中频信号相乘得到IQ两路同相分量和正交分量,要实现这个功能就要产生所需的频率的正余弦波形。所以设置 NCO的工作时钟为80 MHz,产生的正余弦信号频率为20 MHz。如图5为调制后频率为20 MHz的IQ两路信号,图6为下变频后匹配滤波器I路输出的信号。

图4 下变频电路仿真波形

图5 QPSK调制IQ路信号

图6 QPSK匹配滤波I路输出

3 仿真结果

3.1 解调电路仿真

在Quartus II里对解调电路完整仿真时,输入相同的信号,得到的输出结果与在MATLAB中仿真得到的结果相同,只是有部分的延迟,如图7所示。MATLAB中解调后的信号为11010110100000……,从图7可以看出,Quartus II中解调后的信号为11010110100000……解调的结果相同,从而验证模块设计的正确性。

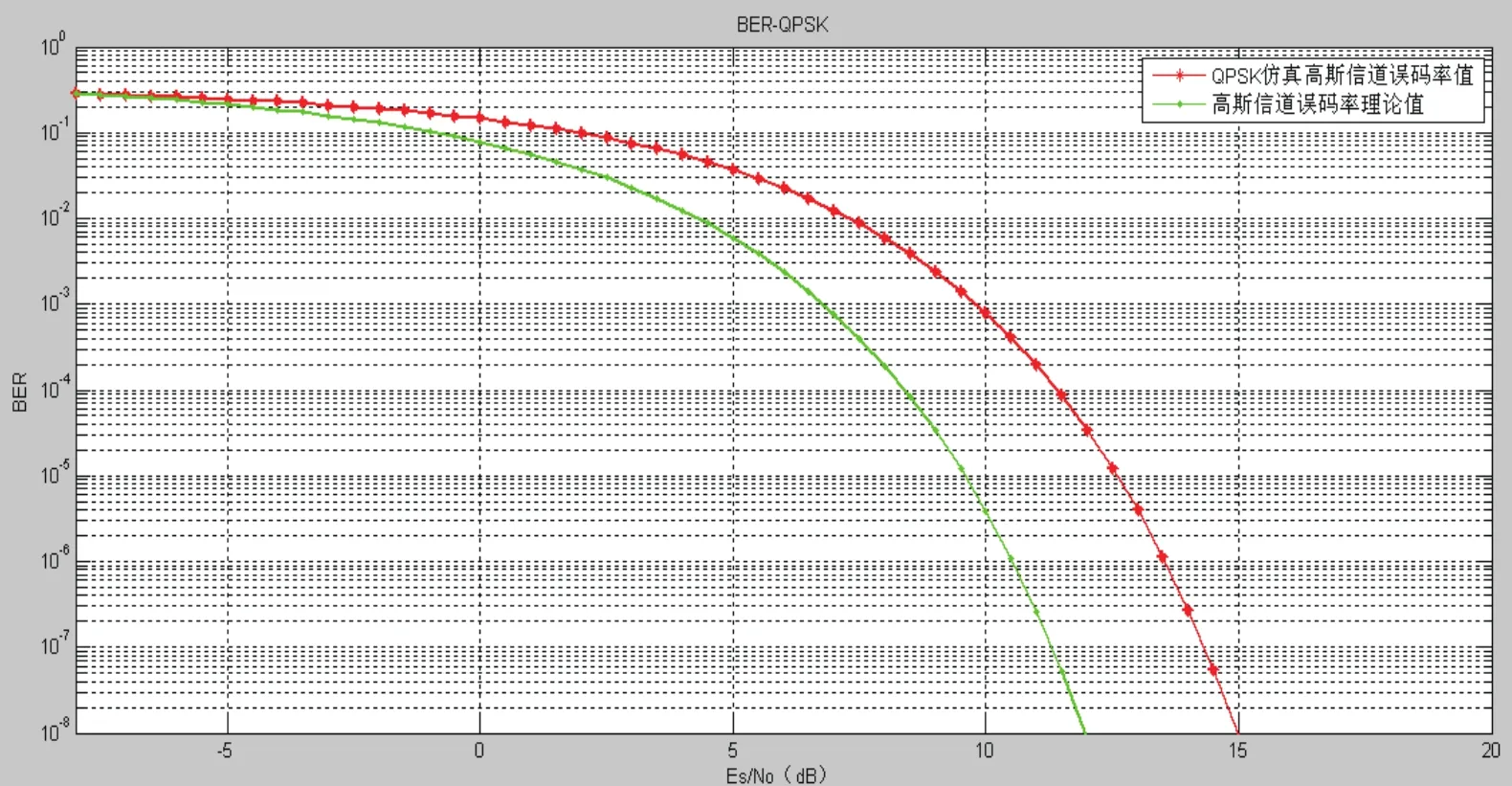

3.2 误码率曲线

通过对QPSK电路仿真得到的误码率曲线与QPSK理论计算得到的误码率[8]曲线,如图8所示。由图8可以看出,在信噪比较小的情况下,电路仿真得到的误码率和理论的误码率性能没有太大差别,但是随着信噪比的提高,电路仿真得到的误码率和理论的误码率性能相比有所下降。本课题要求在信噪比为10 dB时,误码率达到10-3,显然电路的设计能够达到要求的性能指标。

图7 解调仿真波形

图8 解调误码率曲线

4 结论

本文完成了基于FPGA设计QPSK中频全数字解调系统研究与FPGA实现。采用可编程逻辑器件CycloneⅡEP2C70F896C6N成功地实现了QPSK全数字解调的电路的设计,在Quartus II 9.0软件中进行系统的仿真与验证。通过比较Quartus II仿真结果和MATLAB仿真结果,解调出来的结果是一致的,这也说明了所设计的解调模块是正确的。在信噪比为10dB时,误码率达到10-3,显然电路的设计能够达到要求的性能指标。

[1]雷红,陈建春.基于FPGA的8PSK调制系统设计与实现[J].电子元器件应用,2006,(5):32-35.

[2]赵叶星,韦志棉.基于FPGA的DPSK调制解调器的全数字实现[J].RADIO ENGINEERING OF CHINA,2007,37(5):32-35.

[3]路布新.基于FPGA的全数字QPSK通信系统的研究[D].南京:南京理工大学,2006.

[4]Y.Linn.Robust M-PSK Phase Detector for Carrier Synchronization PLLs in Coherent Receivers: Theory and Simulations[J].IEEE Trans.Commun.,June 2009,57(6):1794-1805.

[5]Jeng-Kuang Hwang,Cha-Hsing Chu.FPGA Implementation of an All-digital T/2-Spaced QPSK Receiver with Farrow Interpolation Timing synchronizer and Recursive Costas Loop[R].Advanced System Integrated Circuits 2004.Proceedings of 2004 IEEE Asia-Pacific Conference on Volume, Issue, 4-5,Aug,2004:248-251.

[6]李兴广,陈殿仁.基于FPGA的宽动态范围DPSK解调器设计[J].通信技术,2011(12):18-20,35.

[7]Y.Wang,E.Serpedin,P.Ciblat.Optimal Blind Carrier Recovery for MPSK Burst Transmi-ssions[J].IEEE Trans.Commun.,2003,51(9):1571-1581.

[8]Mei Xiao,Tao Cheng.Improved Implementation of Costas Loop for DQPSK Receivers Using FPGA[J].Beijing Jiaotong University DXJ03008.