基于System Generator的异构多核片上系统设计

2012-09-05杨宏来黄旻

杨宏来,黄旻

(同济大学电子科学与技术系,上海 201804)

1 引言

多核处理器按照所集成的处理器核种类可分为同构多核处理器和异构多核处理器。同构多核处理器在一个芯片内集成多个相同结构的处理器核,多个处理器核执行相同或相似的任务。异构多核处理器在一个芯片内集成多个不同结构的处理器核,除了主处理器核心之外,多数情况下还集成了具有某些针对特定应用设计的处理核心,如ASIP、DSP、GPU等。异构多核处理器可将不同类型的任务分配到不同类型的处理器核上并行处理。面对不同应用需求,它可以提供比较灵活、高效的处理机制[1~2]。

多处理器片上系统(MPSoC,Multi Processor System on Chip)将多个不同类型的处理器核集成在同一个芯片中,构成一个异构多核片上系统。对于嵌入式系统,MPSoC可以满足其在性能、成本和功耗等多个方面的约束条件[3]。

数字图像、音频、视频的多媒体处理技术应用广泛,目前处理算法通常是由软件来完成的。随着深亚微米工艺和大规模集成电路技术的发展,多媒体实时硬件处理成为一个新的发展趋势。现场可编程逻辑器件(FPGA)性能优越,资源丰富,采用并行处理方式,在数字信号处理领域具有很大的优势。采用FPGA设计灵活,程序和模块可移植性强,可缩短设计周期,减少硬件投资风险[4]。本文提出了一种面向SoC的异构多核的系统设计,运用System Generator进行设计实现,通过EDK Processor自动生成Pcore,然后运用EDK建立基于MicroBlaze的嵌入式系统,最后把MicroBlaze和Pcore构建成一个异构多核片上系统,该方法消减了大部分手动硬件语言编写,使设计流程趋于简化,在一定程度上提高了设计效率。

2 图像的退化和复原

2.1 图像退化模型

设有一成像系统,输入图像为f(x,y),输出为g(x,y),即g(x,y)=T[f(x,y)]。其中T为作用函数,可以是线性的,也可以是非线性的。

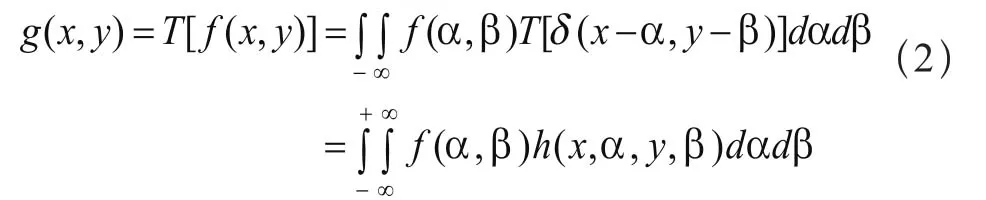

在线性情况下,一幅图像f(x,y)可以看作由一系列点源组成,由点源函数的卷积来表示为:

式中,δ函数为点源函数,且有δ(x-α,y-β)=δ(x-α)δ(y-β),由此可得输出图像为:

式中,h(x,α,y,β)=T[δ(x-α,y-β)],称为系统的冲击响应。图像退化正是由于系统的冲击响应是唯一不变的,此时h(x,α,y,β)=h(x-α,y-β),输出图像可表示为:

图像退化除了成像系统本身的因素外,有时还受到噪声的污染。一般假定噪声n(x,y)为加性白噪声。这时退化后的图像为:

图像的退化如图1所示。

图1 图像的退化模型

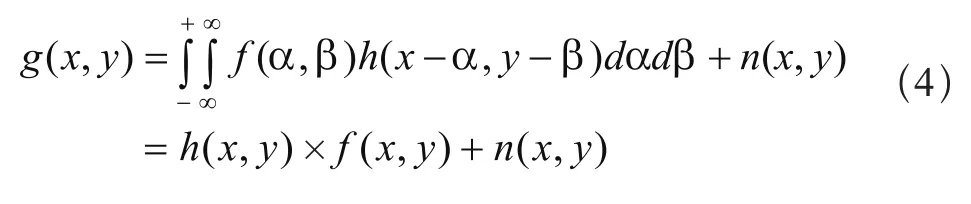

2.2 图像复原模型

图像滤波复原的方法是通过某种方法寻找一个滤波器传递函数,通过频率域图像滤波,得到复原图像的傅里叶变换,然后再经傅里叶反变换求得复原图像,如图2。

图2 连续图像的复原模型

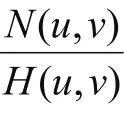

这里根据逆滤波法阐述图像复原模型,根据式(4),假设复原过程为一个线性空间不变系统,若该系统的响应为hT(x,y),则复原图像可表示为:

由卷积定理知,对应的傅里叶变换为:

设复原的滤波器传递函数为:

则式(6)可表示为:

3 系统架构

整体系统架构如图3所示。

图3 系统总体构架图

3.1 MicroBlaze

图3所示系统总体构架中MicroBlaze是Xilinx公司推出的一个高度灵活可以配置的软核。MicroBlaze采用32位哈弗RISC架构,32位独立的地址总线和数据总线。在采用缓存模式下,独立的指令和数据可以缓存并通过XCL(Xilinx CacheLink)接口连接到内存。在不采用缓存的机制下,地址和数据总线直接通过PLB访问内存。用户IP可以通过PLBv46总线或快速点对点连接(FSL)接入系统。其中PLB比较适合基于总线形式的用户IP开发;FSL比较适合基于简单点对点输入输出的用户IP开发。

3.2 System Generator

System Generator是Xilinx公司的系统级建模工具,在Match Works公司的Simulink平台中运行。SG提供了适合硬件设计的数字信号处理(DSP)建模环境,用户只需要根据设计要求在Simulink下进行系统建模,使用SG工具即可自动产生可执行比特文件、测试文件等,去掉了繁琐的仿真、对比和验证过程。

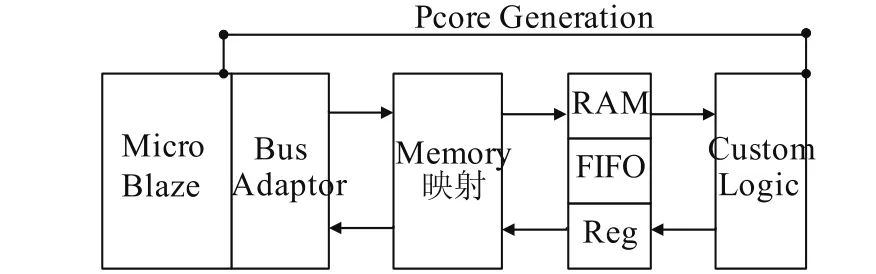

在SG中,提供了3种将嵌入式处理器加入Simulink工程的实现方法:BlackBox、PicoBlaze微控制器以及EDK处理器模块。其中EDK处理器模块提供了MicroBlaze处理器的接口,允许将共享存储器(包括From/To Register,From/To FIFO和Shared Memory)和MicroBlaze关联起来,一旦建立关联关系,MicroBlaze就可以对它实现读写控制[6]。

在FPGA设计中添加处理器Processor,涉及最多的问题是处理器和外部逻辑的数据交换,一般来说交换发生在总线上,协调处理其关系是一个非常繁琐和繁重的工作。System Generator提供的EDK Processor模块能自动帮设计者完成上述所有问题,可以通过在Processor和外部逻辑间使用共享存储器来实现,本文以设计Memory映射和硬件实现等问题为例[7]。

3.2.1 Memory映射

图4 Memory和硬件映射

EDK Processor模块允许共享存储器作为其Memory映射的一部分,这种情况下,EDK Processor模块将自动产生与Memory映射相关的控制逻辑,同时用总线控制器把Memory映射和Processor正确连接起来。其中共享存储器用于软件和硬件(MicroBlaze processor)的接口交互,硬件的当前状态(Status)写入Register,PC通过读取Register当前值获取硬件状态,达到交互信息的目的。

3.2.2 硬件映射

EDK Processor模块支持两种模式的硬件实现方式:EDK Pcore Generation和HDL netlisting。这里采用第一种模式,System Generator将MicroBlaze外部的所有模块综合成Pcore,包括外围设备的硬件描述、驱动、总线连接和相应文档等。产生的Pcore可以导入EDK工程使用。

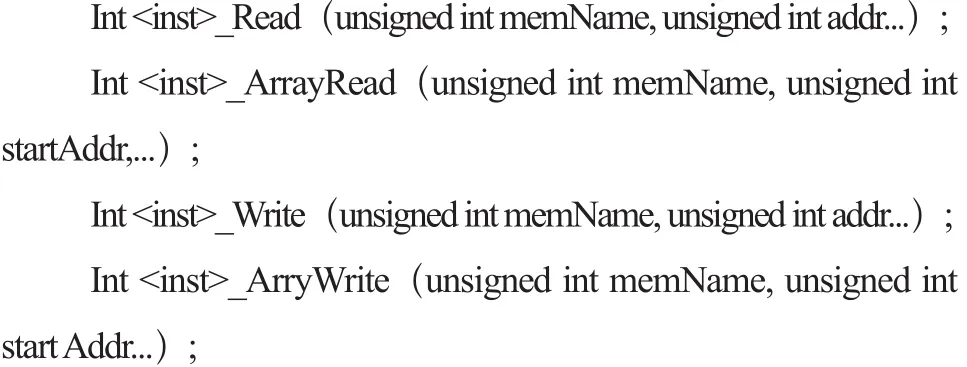

3.2.3 驱动程序的产生和验证

当Memory映射后都会自动产生对应的驱动程序,并且在EDK XPS工具进行软件库编译时验证驱动程序的正确性,软件库编译成功后得到对应驱动的参考文档。在驱动程序中包括最基本的4个调用共享存储器函数,Read和Write分别表示读写共享存储器,单字节或者矢量读写模式都支持。

4 具体设计与仿真

4.1 图像退化实现

这里采用的退化模型为图像水平移动模糊,即将图像的行像素卷积上h,h=[1 1 1 1]。卷积公式可以简化为:

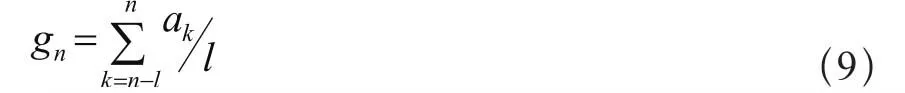

式中,α为原图像像素值;g为退化后图像像素值;l为卷积长度,这里取值为4。

用System Generator系统搭建模型如图5所示。模型中利用三个Register模块来实现移位寄存器,从而完成了行卷积的操作。由于模型的卷积仅为行卷积,所以需要Control模块负责产生Register模块的清零信号。

图5 图像退化的SG实现

4.2 图像复原实现

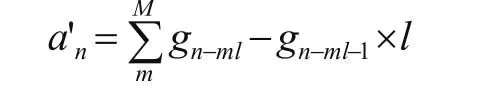

根据式(9)的退化模型,可以推导出与退化模型相对应的时域反卷积模型公式,有:

式中,g为退化了的图像像素;α’为复原后图像像素;M为n/l向下取整;l为退化模型卷积长度。

时域反卷积也可以变换成:

用System Generator系统按照式(10)搭建复原模型如图6所示。

图6 图像复原的SG实现

4.3 基于MicroBlaze的嵌入式系统构建

运用Xilinx Platform Studio(XPS)来创建一个嵌入式系统工程。XPS支持基于MicroBlaze的嵌入式系统的软件和硬件开发。使用Base System Builder Wizard,自动创建一个处理器系统,它由以下处理器IP组成:MicroBlaze、opb_mdm、OPB bus、LMB BRAM、BRAM、UART。本次设计采用的目标板是Xilinx的Virtex-II PRO FPGA开发板。

4.4 系统集成

运用EDK Processor模块产生Pcore导入XPS工程。EDK Processor会自动为每一个共享存储器产生Memory映射,设置Compilation标签为Export as a pcore to EDK,选择目标板的芯片类型,然后在工程目录下生成一个Pcore文件夹,包含Pcore相关的所有文件。把System Generator产生的所有文件复制到XPS工程中,将其添加进MicroBlaze系统中。

4.5 仿真及验证

进行系统搭建的同时可以进行仿真验证,System Generator中的Blockset工具库中,WaveScope可以查看系统仿真的波形。图7和图8分别显示了图像退化和复原的仿真波形图,通过WaveScope Block我们可以查看仿真模型中任意信号线中的信号变化,结果显示本文设计的系统能够实现图像的退化和复原。

设计在Xilinx的Virtex-II PRO开发板上进行了验证,在Xilinx的嵌入式系统开发平台EDK中对系统进行了构建,主核采用MicroBlaze软核,时钟频率选择50MHz,使用PlatGen功能,生成硬件网表,最后生成比特流文件,将其下载到FPGA开发板中进行功能验证。验证结果显示功能正确,但是对图像数据的输入输出处理还不完善,在后期的SoC实现中应主要完成这方面的改进。

图7 图像退化模型的仿真结果

图8 图像复原模型的仿真结果

5 结束语

本文提出了一种面向SoC的异构多核的系统设计,可以方便地实现图像处理。System Generator在很多方面扩展了MathWorks公司的Simulink平台,提供了适合硬件设计的数字信号处理建模环境,加速、简化了FPGA的DSP系统级硬件设计,结合Xilinx的EDK开发工具,可以方便快速地搭建面向SoC的异构多核系统,表1给出了基于SG的SoC设计和SoC传统的Top-Down设计方法的对比。从表1可以清晰看到System Generator简化了SoC的设计流程,提高了设计效率。

表1 基于SG的SoC设计和Top-Down设计流程对比

本文运用System Generator实现了图像的退化和复原的基本算法,生成Pcore协处理器核,在FPGA中进行嵌入式设计,运用软硬件协同设计的方法,实现了基于System Generator的异构多核片上系统设计。该方法消减了大部分手动硬件语言编写,使设计流程趋于简化,在一定程度上提高了设计效率,在教学实践和工程实际中都能够发挥重要作用。

[1]陈芳园,张冬松,王志英.异构多核处理器体系结构设计研究[J].计算机工程与科学,2011,33(12):28-29.

[2]岳虹.嵌入式异构多核处理器设计与实现关键技术研究[D]. 国防科学技术大学.2006:5-12.

[3]Jerraya A, Wolf W. Multiprocessor systems-on-chips[M].SanFrancisco, USA:Morgan Kaufmann Publishers, 2004.

[4]Harding, B F, R C Cofer. Rapid system prototyping with FPGAs-Embedded technology series[M]. Amsterdam:Elsevier/Newnes, 2006. 301.

[5]薛良峰,齐欢.图像复原的逆滤波器技术探讨[J].自动检测技术,2002,21(5):46-47.

[6]Castleman K R. Digital Imagine Processing[M]. 北京:电子工业出版社,2008. 325-329.

[7]XILINX. System Generator for DSP Getting Started Guide[EB/OL]. http ://china.xilinx.com/support/documentation/dt_sysgendsp_sysgen10-1.htm, 2008-4-29.

[8]Alba M Sanchez G., Ricardo Alvarez G., Sully Sanchez G. Architexture for fi ltering images using Xilinx System Generator[J]. International Journal of Mathematics and Computers in Simulation.2007,2(1).