芯片叠层封装工艺技术研究

2012-09-05李丙旺徐春叶欧阳径桥

李丙旺,徐春叶,欧阳径桥

(华东光电集成器件研究所,安徽 蚌埠 233042)

芯片叠层封装工艺技术研究

李丙旺,徐春叶,欧阳径桥

(华东光电集成器件研究所,安徽 蚌埠 233042)

随着大量电子产品朝着小型化、高密度化、高可靠性、低功耗方向发展,将多种芯片封装于同一腔体内的芯片叠层封装工艺技术将得到更为广泛的应用,其封装产品的特点就是更小、更轻盈、更可靠、低功耗。芯片叠层封装是把多个芯片在垂直方向上堆叠起来,利用传统的引线封装结构,然后再进行封装。芯片叠层封装是一种三维封装技术,叠层封装不但提高了封装密度,降低了封装成本,同时也提高了器件的运行速度,且可以实现器件的多功能化。随着叠层封装工艺技术的进步及成本的降低,多芯片封装的产品将更为广泛地应用于各个领域,覆盖尖端科技产品和应用广大的消费类产品。

叠层封装;堆叠;曲翘度;低弧键合

1 引言

现代便携式电子产品对微电子封装提出了更高的要求,其对更轻、更薄、更小、高可靠性、低功耗的不断追求推动微电子封装朝着密度更高的三维封装方式发展[1],芯片叠层封装(stacked die package)是一种得到广泛应用的三维封装技术,叠层封装不但提高了封装密度,降低了封装成本,同时也减小了芯片之间互连导线的长度,从而提高了器件的运行速度,而且通过叠层封装还可以实现器件的多功能化,芯片叠层封装就是把多个芯片在垂直方向上累叠起来,利用传统的引线封装结构,然后再进行封装。由于这种结构的特殊性,芯片和基板之间、芯片和芯片之间的粘接与互连是叠层封装的关键。现在普遍是以引线键合方式实现叠层封装的互连,为避免对现有工艺进行大的改动,叠层封装一般通过减薄芯片的厚度来保证总的封装厚度不变;但是芯片厚度的减少会造成芯片刚度降低,易发生变形,在热处理过程中芯片内应力集中点甚至会造成芯片的损坏。此外,由于塑封料厚度的减小,阻止水汽侵入芯片和塑封料界面的能力就会减弱,水汽的侵入会促使裂纹的产生和扩展。本文就叠层封装在实际生产过程中所遇到的问题及解决方案进行了详细的阐述。

2 叠层芯片封装工艺流程

为了更好地解决生产工艺过程中出现的问题,必须对叠层封装工艺整体工艺流程有着充分的了解,叠层芯片封装工艺流程如下:

晶圆研磨/减薄(grinding)→晶圆贴膜(wafer mounting)→晶圆切割/划片(wafer dicing)→粘片/贴片(die bonding)→打线/键合(wire bonding)(根据具体堆叠方式的需要确定)→芯片堆叠(chips stacking)→打线/键合(wire bonding)→目视检测(vision inspection)→塑封(molding)→电镀(plating)→打标(marking)→切筋成形(trim&form)。

从上述整体工艺流程看,为了达到叠层贴片、键合的高精度要求,其对减薄的厚度和翘曲度、划片的边缘齐整度等都有较为严格的要求。

3 叠层晶圆的减薄、划片

常规的MOS集成电路一般都是表面型器件,功耗小,无需考虑散热问题,所以对芯片厚度要求不高。芯片厚度一般为300μm~400μm左右,然而叠层封装芯片厚度一般为200μm以下,这就必须考虑减薄后晶圆的翘曲以及划片崩裂等问题。

如果采用普通减薄工艺,完工厚度是200μm,Φ200mm的晶圆翘曲度可达1500μm以上,如图1(a)。由于其脆性较强,在交接运转过程中易受振动或外力的损伤,影响成品率,并且因背面加工的粗糙度偏高,高低不平纹路,造成应力集中,在后续工艺划片、贴片时易产生隐形的裂纹,其结果会影响产品的可靠性。为适应芯片叠层封装工艺要求,后段细磨改用直径更小的金刚砂颗粒使其粗糙度小于0.2μm,从而使背面损伤层小于2μm左右。虽然采用此工艺可以去除粗磨阶段形成的大部分损伤层,减小表面的粗糙度,达到较好的镜面效果,但细磨本身也会造成一定的损伤。利用此工艺加工的Φ200mm晶圆,如果完工厚度是200μm,翘曲度可达到180μm左右,如图1(b)。

图1 减薄后晶圆翘曲度图

切割厚度在230μm以上的晶圆,由于划片刀的自修正,即金刚砂颗粒不断被磨损、剥落和更新,崩片问题能及时得到修正。然而,切割厚度在230μm以下时,由于晶圆很薄、很脆,背崩就可能延伸到晶圆正面,发生崩裂,所以在加工较薄晶圆时,必须解决崩裂问题。

划片刀选用金刚砂颗粒较小、中等强度结合剂和中等金刚砂密度的,由于较小的颗粒容易在切割时从刀片上剥落,保持刀片的锋利并且切割较浅,冷却效果好,所以不会发生过载现象,使得划片槽边缘齐整度较好。

4 叠层芯片贴装

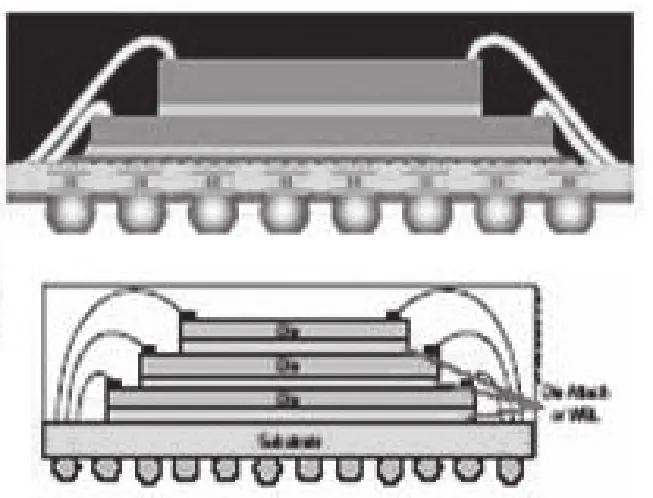

芯片叠层封装是将两个以上芯片封装在一个塑封体内,它是将第一个芯片贴装在引线框的底座上,然后第二个芯片贴装在第一个芯片的上面,第三个芯片贴装在第二个芯片上,如此堆叠下去(如图2)。在内引线连接时有芯片到芯片的引线连接,也有芯片到内引线的连接,因此对贴片精度提出了较高的要求。

在粘片工艺中点胶一般是采用滴胶方式,但这种滴胶方式不能保证芯片的平整度,而改用写胶的方式,它不仅可以保证芯片和胶在接触过程中,芯片在胶上尽量少的漂移,从而确保贴片位置的精度,而且也能较好地满足芯片的平整度的要求。第一层芯片直接和引线框小岛接触,采用普通的工艺即可,用导电胶来粘接,芯片与芯片之间的粘接最好采用绝缘胶。

图2 叠层贴片示意图

表1 封装组件材料属性[2]

叠层封装的IC芯片,面积较大又比较薄,这样它的抗应力能力就较弱,Cu引线框的膨胀系数为160×10-7/℃~180×10-7/℃,Si芯片的膨胀系数为26×10-7/℃(见表1),膨胀系数差异造成在温度快速变化时,因为产生较大的应力,芯片发生弯曲,而作为粘接材料的胶既起到粘接作用,又可以在Cu引线框和Si芯片之间起到缓冲热膨胀应力的作用,要想降低应力,必须从两方面来考虑:一是控制胶层的厚度,薄的胶层对改善由于膨胀系数差异而产生的应力不太明显,厚的胶层可以很好解决这方面的问题,但是如果胶太厚则会影响到封装工艺的质量,最后我们将导电胶和绝缘层的厚度控制在30μm±5μm;二是贴片胶的固化条件对应力的影响,固化的温度太高不利于应力的消除,因此固化条件采用三段时间固化:升温→主固化→降温,其在主固化阶段采用降低温度延长时间的方法。

5 芯片堆叠方式

芯片堆叠应根据封装的不同要求而采用不同的堆叠方式,具体的芯片堆叠方式如下:

(1)金字塔式

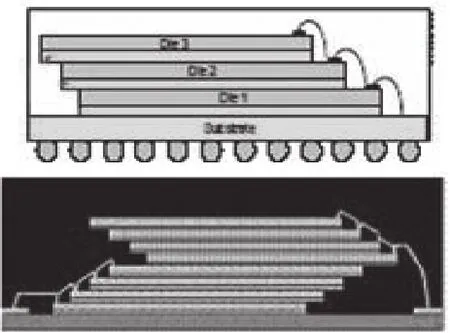

第一种是金字塔型的叠层封装(如图3),使用大小不同的芯片,上层芯片面积比下层芯片面积小,这样下层芯片表面就有足够的面积和空间可以用来进行引线键合。

图3 金字塔型贴片键合示意图

(2)错位式

第二种是错位式的叠层封装,使用大小相同的芯片,上层芯片与下层芯片之间进行错位贴装(如图4),这样每层芯片表面就有足够的面积和空间可以用来进行引线键合。

图4 错位式叠层贴片键合示意图

(3)交替式

第三种是交替式的叠层封装,使用大小相同的芯片,上层芯片与下层芯片进行不同方向的错位贴装,交替进行(如图5),这样每层芯片表面就有足够的面积和空间可以用来进行引线键合。

图5 交替式叠层贴片键合示意图

(4)同尺寸式

第四种是同尺寸式的叠层封装(如图6),使用大小相同的芯片,通过在上下层芯片之间加入一层垫片(spacer)以便于下层芯片的引线键合,垫片是一块面积比上、下层芯片小的普通硅片。

6 叠层焊线键合

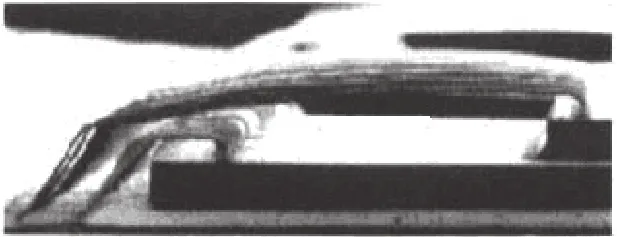

芯片叠层封装的键合最关键的技术是Z方向的立体键合技术[3],包括金线低弧键合技术(如图7)和芯片与芯片间的金线键合技术(如图8)。高度限制及叠层结构技术要求所增加的复杂性对在叠层芯片应用中的金线键合技术提出了一些特殊的挑战[4],当芯片厚度增加时,不同线环形层之间的间隙相应减少,这时就需要降低较低层的引线键合弧高,以避免不同的环形层之间的线间短路。环形顶层也需要保持低位,以避免在塑封后金线露出塑封体,器件键合线的最大弧高,不应高于保持环形层之间最佳缝隙的芯片厚度。因此,如果芯片厚度为100μm,最佳的弧高应为100μm或低于100μm。

图6 同尺寸叠层贴片键合示意图

图7 金线低弧键合

图8 三维金线键合

对于不同的芯片堆叠方式应采用不同的键合工艺和方法,如金字塔型堆叠、单向的错位式堆叠可采取先堆叠,后键合的方法;而对于堆叠后对键合区产生阻碍的堆叠方式(如交替式、同尺寸等)都应采取贴片、键合交替循环的工艺方法。

7 芯片叠层封装

芯片叠层封装一般采用环氧塑封料注模成形的封装方式,在封装过程中主要应注意以下几个方面的问题:

(1)用环氧塑料封装的电路是非气密性的,电路暴露在空气中会吸收水分,如果塑封体吸湿或塑封料含水量过多,当其处于典型的回流焊或波峰焊温度中时,会产生裂纹;产生的气压如超过塑封体强度还会使之破裂,高温和温度突变是产生开裂的主要因素[5]。

(2)由于内部叠层芯片堆叠结构不同,树脂在模具型腔里的流动发生变化,很容易产生内部气孔,所以选用流动性好、黏度低的树脂就非常重要。同时也可以适当提高模具温度,使树脂能顺利充满型腔。

(3)由于叠层芯片的顶层芯片与塑封体外壳的距离只有不到0.5mm左右,外壳的抗爆能力较弱。

8 结束语

芯片叠层封装是一种3D电子封装技术,其封装的电子产品密度更高、功能更多、速度更快、性能更好、可靠性更高、成本更低。随着大量电子产品向小型化、轻量化发展,随着技术的进步及成本的降低,相信芯片叠层封装工艺技术将得到更为广泛的应用。

[1]田民波.电子封装工程[M].北京:清华大学出版社,2003.

[2]Utsumi Shigeru,Oka Serji.Electrical Properties and Reliability of Organic Integral Passives Substrate[C].2003 ICEP,International Conference on Electronics Package,2003∶ 199-206.

[3]王毅.高密度高性能电子封装技术的新发展[J].电子工业专用设备,1998,27(3)∶31-45.

[4]刘文俊.高密度高性能电子封装技术[J].微电子技术,1998,26(2):1-14.

[5]孙宏伟,罗文丽.塑封成形缺陷研究[J].微电子技术,1999,27(2).

The Research of Packaging Technoligies in Stacking Chips

LI Bing-wang, XU Chun-ye,OUYANG Jin-qiao

(East China Photoelectronic IC Research Institute,Bengbu233042,China)

The stacking-chips packaging(SCP)process technology which packages two or more chips in the same volume is getting more abroad application in the development of electronic products smaller, more compressive, more reliable, lower power-expending, because it’s character is smaller, more light、more reliable、lower power-expending.The SCP is stacking chips on the traditional frame to package.The SCP is a solid packaging technology,it is not only improving compression、speed,but also reducing cost and carring out multi-function. The product of SCP is getting more abroad application in every fi eld including high-tech and consumption in the development of process technology getting ahead and cost reducing.

SCP; stacking; bended degree; low-radian wire bonding

TN305.96

A

1681-1070(2012)01-0007-04

2011-09-09

李丙旺(1971—),男,安徽望江人,高级工程师,1996年毕业于安徽大学,南京理工大学通信工程专业工程硕士在读,工作于华东光电集成器件研究所,主要从事半导体及特种器件测试、封装工艺研究及相关设备的维修工作。