采用CPCI总线的通用高速数传接收机

2012-09-03刘进军

刘进军

(中国西南电子技术研究所,成都 610036)

1 引 言

近年来,随着高速数传技术应用领域的不断拓展,高速数传技术不仅广泛应用于侦察卫星、军事卫星、资源探测卫星、高分辨率对地观测卫星等航天器中,而且航空飞行器如预警机、高空侦察机、无人机等,以及临近空间飞行器也纷纷增加了数据获取功能,需支持高速数据传输或海量存储能力。在高速数传系统中,高速解调设备是核心。目前,国内主流的高速解调设备处理能力均低于300 Mbit/s数据传输速率,已不能满足日益增长的数据传输速率需求。随着系统支持数据传输速率的提高,对接收机的电路设计、解调性能等提出了挑战,高性能的高速解调接收机市场需求迫切。

本文采用软件无线电设计思想,对高数数传接收机软硬件技术进行了深入研究,通过硬件模块化设计和软件动态加载与升级技术,提高了接收机设计灵活性和通用性。

2 接收机实现原理

通常,高速数传接收机可采用模拟、模数混合以及全数字3种实现方式。模拟实现方式存在设备复杂、实现难度大以及通道一致性较差等缺陷,影响高速数据解调性能;而模数混合和全数字实现方式具有通道一致性好、设计灵活等优点,是一种较好的设计方案。

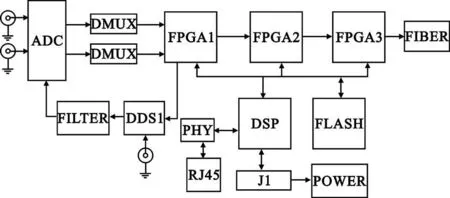

接收机具备高速数据处理能力,其电路器件选择和电路设计需满足高速数传要求,接收机主要由超高速模数变换器(ADC)、直接数字合成器(DDS)和大规模可编程器(如FPGA、DSP等)组成,实现原理框图如图1所示。

图1 高速数传接收机原理框图Fig.1 The block diagram of high-rate data transmission receiver architecture

模拟基带信号或中频信号经信号调理后,由ADC进行采样变换,完成信号离散处理,由FPGA1控制DDS的频率控制寄存器,产生相位连续的正弦波信号作为采样时钟。采样后的离散差分数据通过DMUX降速后,送入FPGA1中进行载波恢复、位同步信息提取、匹配滤波、信道均衡等信号处理[1]后,将数据送到FPGA2中完成译码,包括维特比译码、帧同步、RS译码、Turbo译码、LDPC译码等。译码后的数据通过FPGA3进行数据打包及协议处理,由高速光纤或10/100/1 000Mbit/s以太网接口输出到数据记录模块或远控中心。接收机各模块之间的通信、控制命令、上报状态和数据均采用PCI接口电路,提高了系统设计一致性。

3 主要功能设计

3.1 模拟前端设置

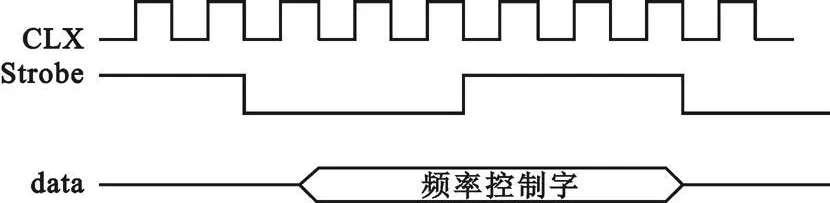

高速数传接收机模拟前端可配置为模数混合和全数字两种接收机结构。接收机工作在模拟接收模式,ADC采用双通道工作,同步采样I/Q两路模拟信号;接收机工作在全数字接收模式,ADC采用单通道工作,对输入的中频信号进行采样。为适应两种工作模式,高速数传接收机需兼容提供不同采样时钟,采样时钟由DSP控制FPGA1,通过FPGA1构建DDS产生,DDS控制时序如图2所示。

图2 DDS控制时序图Fig.2 DDS control logic diagram

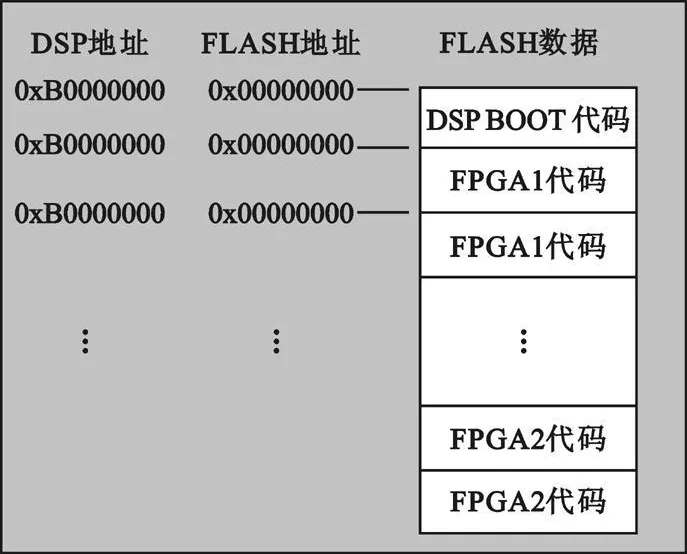

3.2 软件动态加载

为满足接收机通用性设计需求,FPGA1主要功能设计为解调,实现载波恢复、位同步信息提取、匹配滤波、信道均衡等功能。FPGA2主要功能设计为译码,包括维特比译码、帧同步、RS译码、Turbo译码、LDPC译码等。在不同应用环境下,解调和译码程序需要刷新,因此,设计FPGA具有动态加载或远程更新功能。对FPGA1和FPGA2程序进行预先规划,存放于超大容量FLASH地址单元中,通过系统命令选择对应的功能模式。针对新增加功能,可通过远程更新,利用网络将程序传至系统模块中,再由系统将程序写入到未用的FLASH空间,写完后启动代码即实现新功能。DSP外部寻址空间是4 Mbyte,FLASH容量为256Mbyte,寻址空间与容量地址不匹配,因此,通过FPGA3控制FLASH高位地址,DSP的BOOT和程序代码放置于FLASH最低段,按照12Mbyte空间分配FPGA1和 FPGA2的程序代码。FLASH存储空间分配如图3所示。

图3 DSP和FPGA1、FPGA2程序代码分配图Fig.3 Distribution of DSP,FPGA1 and FPGA2 programs

为缩短FPGA1和FPGA2程序加载时间,可预先将数据写入FLASH中,主要有两种写入法:一种是主机通过PCI总线将代码写入DSP,再由DSP写入FLASH中;另一种是由DSP直接读FPGA程序文件,将代码写入FLASH中。FPGA进行动态加载时,直接通过主机选择对应功能版本,由DSP将FLASH中代码直接写入FPGA中。

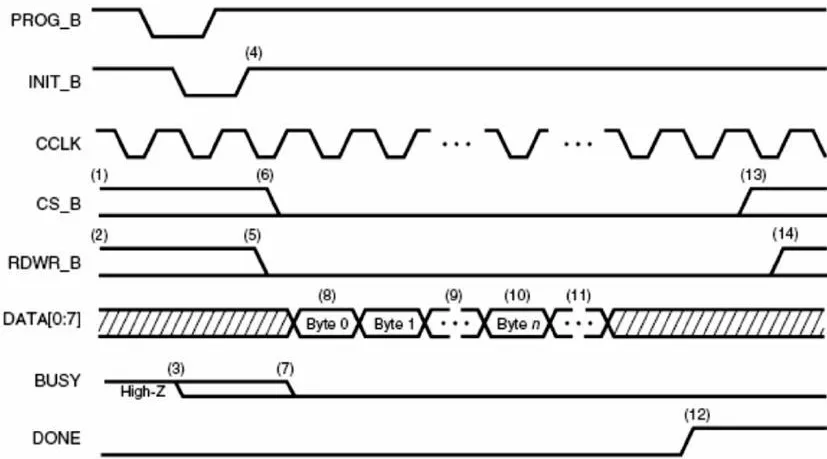

FPGA1和FPGA2动态加载时序如图4所示。

图4 FPGA1和FPGA2动态加载时序图Fig.4 Dynamic loading timing diagram of FPGA1 and FPGA2

DSP异步访问接口和 FPGA3相连,FPGA1和FPGA2加载端口连在FPGA3上,由FPGA3将DSP命令时序转换成图4所示时序。操作步骤如下:

(1)DSP送入FPGA3动态加载命令,FPGA3将PROG-B置一段低脉冲;

(2)DSP从FPGA3读INIT-B状态,由低到高依次读FLASH数据,将数据写入FPGA3;

(3)FPGA3收到写数据命令,产生写时钟,将数据写入FPGA1或FPGA2;

(4)数据写入成功后,DONE信号电平跳变,表示加载成功,并上报状态。

3.3 CPCI总线设计

常用CPCI接口采用PCI桥芯片设计,一端提供PCI总线,一端为本地端口。本接收机系统中,直接使用DSP的PCI外设接口,用C语言代替硬件描述语言做控制逻辑,增加了通用性和灵活性。该PCI接口符合PCI2.3规范,工作频率为33 MHz/66 MHz,本接收机选择工作频率为33 MHz,采用32位数据线,其传输峰值速度可达132 Mbyte/s。

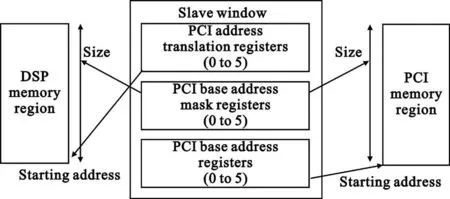

DSP的PCI接口程序主要包括配置寄存器、存储器映射寄存器。对C6455芯片而言,供应商ID、设备ID分别是0x104C、0xB000,对多个板卡共用一个机箱情况下,只需更改ID号就可识别不同设备。DSP地址空间和PCI空间的映射关系如图5所示。

图5 DSP地址空间到PCI地址空间的映射图Fig.5 The address of DSP and PCI mapping diagram

C6455提供了6个基地址寄存器BAR0~BAR5,通过设置基地址寄存器,可实现DSP和主机端的地址映射。DSP作为高速数传接收机的控制功能单元,接收主机下发的各种参数和命令,产生相应的控制流程,同时读取FPGA中各种状态信息,并上报参数。

4 性能测试

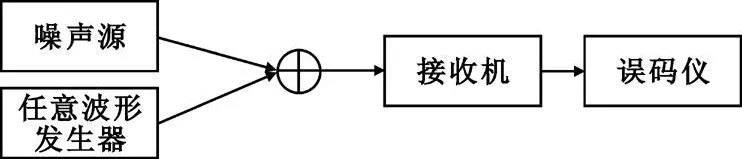

接收机解调误码性能(BER)是衡量接收机性能的重要指标。通过任意波形发生器产生不同的调制数据输入到噪声源,与噪声源产生不同噪声功率谱密度的高斯白噪声相加后,送入接收机解调,解调后数据送误码仪测试解调误码率,就可完成高速数传接收机的解调误码性能指标测试。测试连接如图6所示。

图6 高速数传接收机误码性能测试框图Fig.6 High-rate data transmission receiver BER performance test diagram

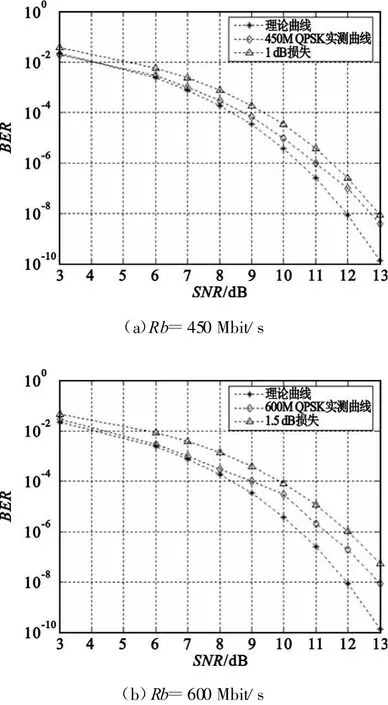

针对QPSK调制信号,数据传输速率分别为450Mbit/s和600 Mbit/s情况下,接收机误码率测试结果如图 7所示。测试结果表明,当码速率为450Mbit/s情况下,接收机的解调损失在1 dB以内,码速率为600 Mbit/s情况下,接收机的解调损失在1.5 dB以内。本文所设计的接收机实现方案从解调损失上要优于文献[2]中设计的接收机,在传输数据速率600 Mbit/s的情况下,本文的方法取得了大约1.5 dB的性能增益,这在实际的应用中是非常有意义的。

图7 接收机误码率测试曲线Fig.7 The BER curves of high-rate data transmission receiver

5 结束语

本文设计的CPCI总线高速数传接收机,采用硬件模块化、功能化以及软件动态加载与升级技术,解决了不同高速数传系统应用中使用同一硬件平台的难题,目前已成功应用在450 Mbit/s和600 Mbit/s两种不同的高速数传系统工程项目中。另外,通过设计了模数混合和全数字接收机两种硬件接口以及ADC采样率实时设置功能,该高速数传接收机具有更强的通用性和灵活性,可应用在其他中低速数传系统中。

[1] 曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,2006.CAO Zhi-gang,QIAN Ya-sheng.Modem Communication Principle[M].Beijing:Tsinghua University Press,2006.(in Chinese)

[2] 董长海,郑雪峰,郑戈,等.600Mb/s高速数传接收的设计与实现[J].遥控遥测,2007(增刊):31-34.TONG Chang-hai,ZHENG Xue-feng,ZHENG Ge,et al.Design and Realization of 600Mb/s High Data-rate Receiver[J].Journal of Telemetry,Tracking and Command,2007(Suppl.):31-34.(in Chinese)