应用于FPGA测试的导航映射方法

2012-07-19张倩莉刘忠立

张倩莉,于 芳,刘忠立,李 艳

(中国科学院微电子研究所,100029 北京)

应用于FPGA测试的导航映射方法

张倩莉,于 芳,刘忠立,李 艳

(中国科学院微电子研究所,100029 北京)

针对目前FPGA厂商的EDA工具不对用户提供专用芯片测试功能,提出一种可应用于FPGA测试的导航映射方法.通过导航映射对FPGA底层硬件进行完全可控操作,精确控制FPGA逻辑资源的使用,可以对FPGA逻辑资源进行有针对性的测试,有效提高FPGA的测试覆盖率,同时在用户约束文件的指导下可以绕开FPGA硬件缺陷进行编程,实现有效的FPGA软件容错功能.本文采用128个测试配置对FPGA进行了验证,结果表明,利用导航映射方法可以得到良好的测试覆盖率.

FPGA,用户约束文件,导航,映射,测试

现场可编程门阵列(FPGA)自从问世以来,凭借其可配置重构这一特性,已经在各个领域得到了广泛的应用.今天的FPGA在结构上更得到了广泛的扩充,更像是1个片上系统(System On a Chip),它可以包括混合信号 I/O(mixed signal IO),千兆赫兹收发器(Gigahertz transceivers),以及大量可配置的逻辑和用于辅助设计的软件工具[1].由于FPGA结构日益复杂,规模越来越大,内部资源的种类日益丰富,致使对FPGA测试的难度也越来越高.

FPGA测试方法的特殊挑战在于[1]:1)FPGA测试方法要与终端应用有相同相关性,同时也要独立于终端应用;2)应该具有可扩展性,并且与阵列尺寸无关;3)可重复使用并且可以自动化操作;4)易于测量定位.

目前对于FPGA的测试分为应用相关的测试和应用无关的测试:应用相关的测试是指将某种特定应用下载到FPGA芯片,观察其功能是否正常,从而检测FPGA的硬件缺陷.这种测试方法的弊端在于,特定的应用对被测FPGA内部资源的底层硬件电路结构没有针对性,测试覆盖率不高;应用无关的测试是指针对FPGA底层硬件结构,设计以测试覆盖率为目标的测试配置,下载到FPGA中,施加测试向量进行测试,这样的方法能达到较高的测试覆盖率,但实现起来有较大难度,因为对底层硬件的操作需要软件设计工具完全可控才能实现.由于FPGA芯片具有可编程的特点,即使FPGA芯片具有工艺缺陷,如果可以确定缺陷位置,在编程时绕过缺陷所在逻辑,那么这种缺陷是可以接受的[2].避开有缺陷的逻辑进行编程,同样要求软件设计工具对底层硬件的操作是完全可控的[3].

目前商用FPGA的EDA工具仅仅支持相关生产商开发的FPGA,不能支持或评估其他厂商开发的不同结构的FPGA[4].并且商用EDA工具并不对用户开放专用的芯片测试功能,所以开发1个带有测试功能,可以对底层硬件操作完全可控的EDA工具对具有自主知识产权的FPGA生产商具有较大意义.

为了在EDA工具中加入FPGA测试功能,并在应用无关的测试过程中实现较高的测试覆盖率,同时在FPGA应用设计时达到避开有缺陷的逻辑进行编程的目的,实现有效的FPGA软件容错功能,本文提出一种可以对底层硬件进行完全可控操作的可用于FPGA测试的导航映射方法.

1 FPGA硬件结构

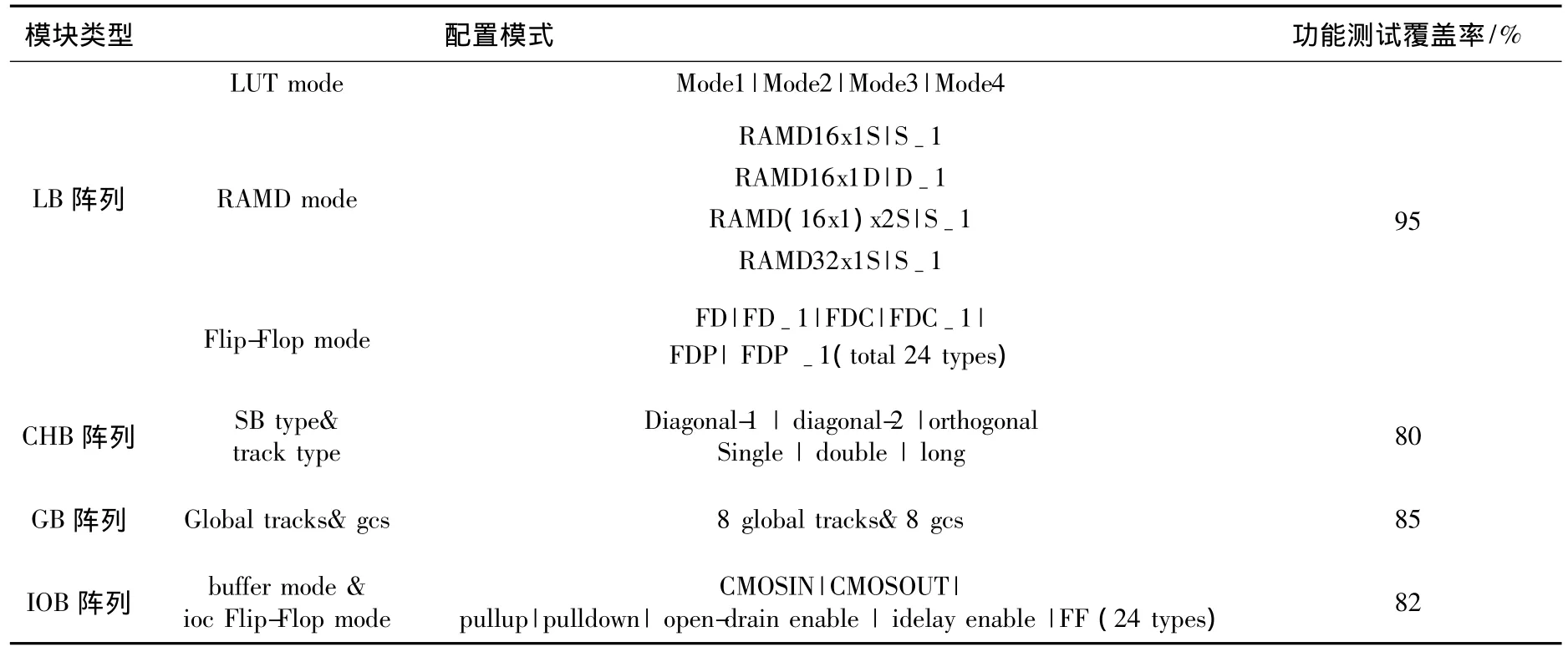

本文所针对的特定结构FPGA是自主研发的基于0.5 μm SOI-CMOS工艺的5万门 FPGA.该FPGA内部资源包括输入输出模块(I/O Block,IOB),逻辑模块(Logic Block,LB),全局模块(Global Block,GB)以及布线通道模块(Channel Block,CHB).其中,逻辑模块为导航映射主要处理的对象:1个LB由两个逻辑单元(Logic Cell,LC)组成,每个 LC中包括1个4输入查找表(LUT4)和1个D触发器(DFF).

LC结构如图 1所示[5],LUT4是由两个LUT3和1个2-1MUX构成.图中F5MUX连接同一LB中的两个 LC中的 LUT4,使之构成1个LUT5.

图1 LC逻辑结构

同时,LC可配置为分布式存储器(Distribute RAM,RAMD).单个LC中的LUT4可配置成1个16X1单端口(single-port)RAM,或者将1个LB中两个LUT4结合起来配置成1个16X1双端口(dual-port)RAM或者1个32X1单端口RAM.

2 FPGA软件设计流程及映射工具

EDA设计流程如图2所示,电路描述文件经由综合、网表转换、映射、布局、布线、码流生成、下载等几个步骤,完成对FPGA芯片的配置,以达到电路设计或测试的目的.

其中映射工具的主要职能是:对综合结果进行分析,将以基本逻辑单元(Basic Logic Element,BLE,包括 LUT、FF、RAMD、I/O PAD 等)为单位的网表,结合FPGA的结构,转化为以LB为单位的网表,提供给下一步骤的布局布线工具.

本文提出的导航映射方法集成在映射工具中,专门用于对FPGA进行测试以及在应用FPGA时避开已知硬件缺陷.

图2 EDA工具设计流程

3 用于导航的UCF文件

本文提出的导航映射方法是完全遵循导航文件约束和规定进行映射操作的方法.导航文件又称用户约束文件(User Constrain File,UCF),是根据综合结果的网表文件针对基本逻辑单元、I/O、布线资源等在映射(mapping),布局(place)或布线(route)阶段进行约束和指导的文件.

现阶段也有部分FPGA软件采用UCF文件,例如Xilinx的ISE,但是其UCF文件中只能对芯片I/O引脚和一些时序进行约束[6].本文提出的用于导航的UCF文件还具备对FPGA的逻辑和连线进行约束的功能.

用于FPGA模块测试及全芯片测试的导航映射,主要依赖各种测试配置(Test Configuration)的底层硬件电路描述文件以及相应的导航文件.这两种文件采用以下方式获得:利用脚本语言,结合FPGA的硬件结构,自动生成有逻辑块针对性,有一定规律的可以对硬件底层进行操作的测试用电路描述文件和用于导航的UCF文件.UCF文件中一一对应的描述了底层硬件电路描述文件内基本逻辑单元的各种约束信息.

UCF的内容包括以下几方面:所约束模块的类型;基本逻辑单元名称;基本逻辑单元所属LB信息;基本逻辑单元所属 LC信息;打包连线标志.

4 用于测试的导航映射

导航映射中,映射工具需要读取UCF文件,并且严格按照UCF文件的约束和导航进行映射,这样可以有针对性的进行特定目标的测试,有效提高测试覆盖率.

4.1 导航映射的文件读取

在映射工具准备阶段,需要读取FPGA架构文件、综合输出的网表文件作为映射工具的输入.用户需将软件设置为测试模式,映射工具将会调用导航映射算法,并读取导航文件.其中导航文件UCF起到对映射过程的约束和指导作用.

FPGA架构文件主要提供FPGA芯片的结构信息,包括FPGA中各种模块的位置、数量、内部结构及连接关系等.

由脚本语言针对硬件底层结构生成的与UCF配套的测试用电路描述文件(verilog),经过综合器综合(synthesis)输出网表文件,它主要由I/O pad、BUFG、LUT、FF、RAMD 等基本逻辑单元和它们之间的连线构成.本文涉及的特定结构FPGA可以实现1-4输入的LUT.同时,单个LUT4可以配置为1个RAMD 16X1S,1个LB内的两个LUT4可以共同配置为1个RAMD 16X1D或者1个RAMD 32X1S.

映射工具在读取UCF文件时,根据UCF文件中所约束基本逻辑单元的名称,在网表文件中找到对应的BLE,并将所有约束条件记录到该BLE的数据结构中,便于后续步骤使用.

4.2 导航映射的过程

应用于测试的导航映射的特点在于,它脱离原有的映射算法,完全按照UCF文件内的约束进行映射.导航映射的过程如图3所示.

映射工具按照UCF文件的约束条件,遍历网表中所有的基本逻辑单元,选出lb标记值与lc标记值完全相同的BLE,结合FPGA硬件结构将他们进行packing工作,生成以LC为单位的网表文件.接下来,重新遍历网表文件中的LC,选出lb标记值相同的LC,按照它们lc标记值的位置信息,进行clustering步骤,形成LB.映射结束后生成的输出文件是以LB为单位的网表文件,交给布局布线工具进行操作.

图3 导航映射过程

5 用于回避缺陷的导航映射

由于导航映射是一种严格按照导航文件的约束和指导进行的映射方法,所以当测试出FPGA部分逻辑具有缺陷时,可以定位出缺陷逻辑块的坐标,并在导航文件中加以标注和约束,通过导航映射,可以避开有缺陷的逻辑块,实现了一种有效的FPGA软件容错功能.

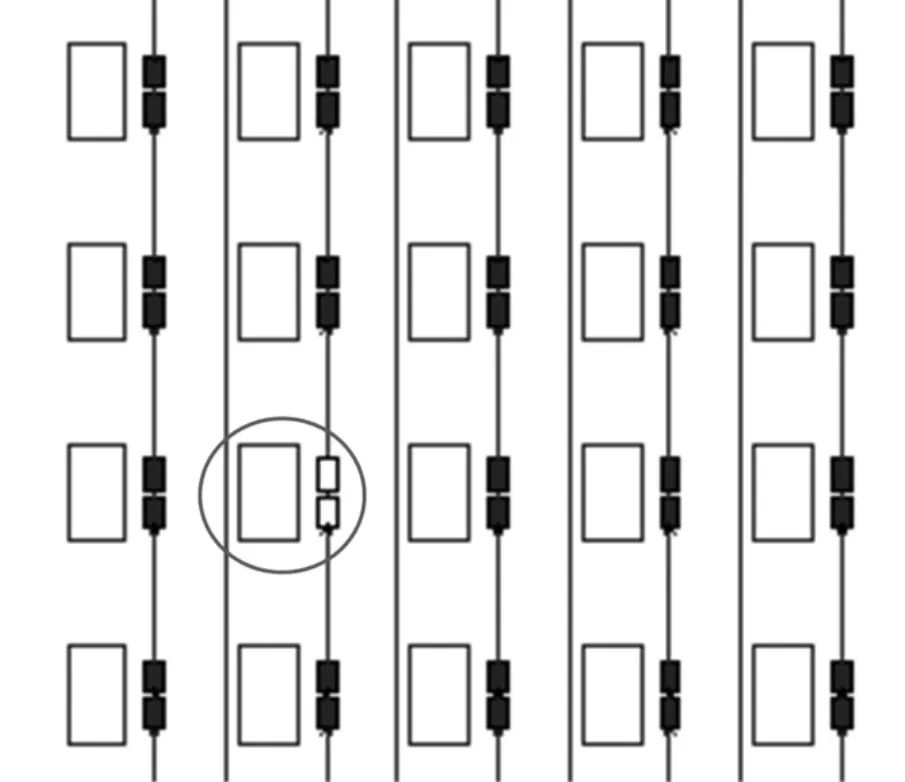

图4为回避缺陷的导航映射结果,通过EDA工具中的导航布局布线后形成的图形界面.圈内部分在导航文件被约束为缺陷逻辑模块,在导航映射以及后续布局布线过程则回避这一缺陷模块,使得FPGA仍可继续使用.

图4 回避缺陷的导航映射

6 测试的实施及测试结果

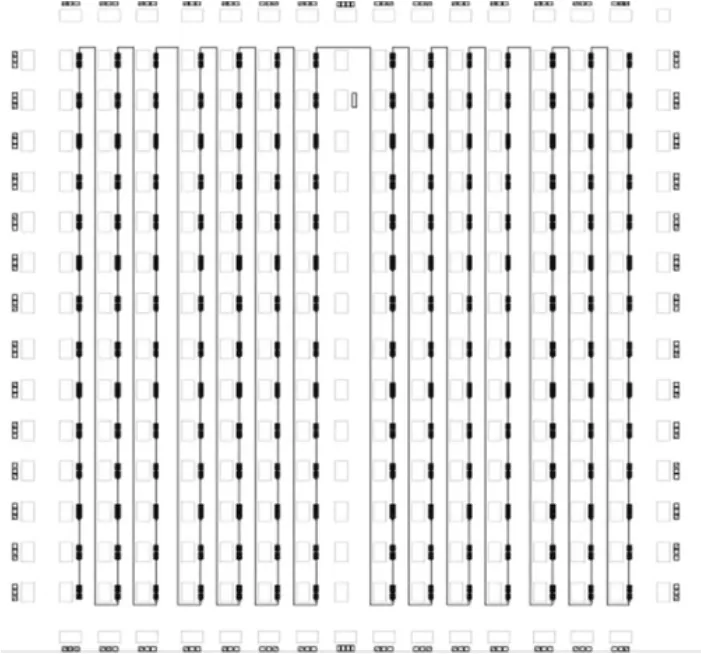

为了在应用无关的测试过程中对FPGA逻辑结构中的每1个逻辑单元都能有针对性的进行测试,并且达到较高的测试覆盖率,利用上文所述脚本语言针对全芯片共生成128个测试配置进行测试.

6.1 测试BLE连线及相应布线通道

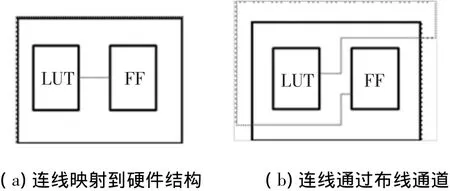

packnet是UCF中的打包连线方式标志,其默认值为1,代表当前BLE进行打包时BLE之间的连线会映射为LC的内部连接.当packnet值为0时,要求当前BLE在进行packing过程时,BLE之间连线需要通过FPGA布线通道,如图5所示.这样可以精确测试到指定逻辑块的特定布线通道.

图5 测试BLE间连线及布线通道

6.2 测试LUT4内部结构

本文所述FPGA的LUT4结构是由两个LUT3构成,如图1所示.在测试过程中,可以在UCF文件中指定C-LUT3,S-LUT3,F4MUX的各种测试组合.通过导航映射的方式,生成相应的测试配置.这种方式同时还可用于进位链这种使用专用布线资源的测试.

图6所示为经过导航映射后生成的进位链的测试配置.图形化结果显示通过导航映射,整个FPGA的进位逻辑被连成1条长链.

图6 测试进位链的资源占用和布线

6.3 测试F5MUX

在本文所述FPGA结构中,可以将同1个LB内的两个LC配置成1个LUT5或者RAMD 32X1S.以两个LUT4实现1个LUT5为例,需要借助1个MUX2实现该功能,图1中的F5MUX负责实现这一功能.通过导航映射,可以测试FPGA中任意LB中F5MUX的功能.

6.4 测试覆盖率

结合FPGA硬件结构、逻辑阵列数量、由脚本语言同步生成的用于测试的电路描述文件、用户约束文件,可以在测试过程中达到很高的覆盖率.表1[5]显示了对全芯片进行的128个测试配置和测试覆盖率,其中针对逻辑模块的测试覆盖率可达到95%,功能测试覆盖率为85%.

表2为针对逻辑资源的有代表性的测试配置通过导航映射和利用T-Vpack算法[7]进行映射的结果比较.其中测试芯片为24×24的阵列,共有576个逻辑模块.通过比较结果可以得出,对于不同测试配置,T-Vpack算法映射的结果差异很大,有的模型超出阵列规模,无法达到针对特定结构FPGA进行测试的目的.而导航映射针对不同的测试配置,能严格根据硬件结构进行映射,得到的结果完全适应阵列规模,满足测试预期.

表1 全芯片测试的128个测试配置

表2 逻辑模块测试配置导航映射和T-Vpack算法映射的结果比较

7 结论和总结

本文提出了一种可以对FPGA硬件底层进行操作,能实现对FPGA进行全面可控并有针对性测试功能的导航映射方法.应用于FPGA测试的导航映射的特点在于:

1)在UCF的导航下,可以按照测试需求,占用部分或全部的逻辑资源,以完成对FPGA芯片测试或辅助测试功能;

2)对于有逻辑缺陷的FPGA,可以通过导航文件约束缺陷坐标,使得映射过程避开缺陷逻辑块,以实现一种有效的FPGA软件容错功能.

经128个测试配置[8]结果显示,本方法对于FPGA的逻辑模块可以达到95%测试覆盖率.利用导航映射方法和T-Vpack算法针对同一结构FPGA进行应用无关测试,比较结果表明,导航映射满足了对底层硬件操作完全可控的要求,达到了对特定结构FPGA有针对进行测试的预期.导航映射结果可预知,具有测试针对性,测试目标确定可控.

如果将导航映射与映射算法结合,将可以进一步提高测试覆盖率.同时本方法还可以推广到用于任何类似结构FPGA的测试中.

[1]LIAO Y B,LI P,Ruan A W.A HW/SW co-verification technique for field programmable gate array(FPGA)test[C]//Testing and Diagnosis,2009.ICTD 2009.IEEE Circuits and Systems International Conference on.Piscataway:IEEE,2009:1-4.

[2]LIAO Y B,LI P,RUAN A W.Full coverage manufacturing testing for SRAM-Based FPGA[C]//Integrated Circuits,ISIC'09.Proceedings of the 2009 12th International Symposium on.Piscataway:IEEE,2009:478-481.

[3]TOUTOUNCHI S,LAI A.FPGA test and coverage[C]//ITC International Test Conference.Piscataway:IEEE,2002:599 -607.

[4]BETZ V,ROSE J,MARQUARDT A.Architecture and CAD for deep-submicron FPGAs[M].Aarhus:Kluwer Academic Publishers,1998:2 -10.

[5]HAN Xiaowei.Design and verification of radiation-hardened SOI-based FPGA(Ⅱ)[D].Beijing:Chinese Academy of Sciences,2011.

[6]薛小刚,葛毅敏.Xinlinx ISE 9.X FPGA/CPLD 设计指南[M].北京:人民邮电出版社,2007:173-207.

[7]ZHANG Qianli,CHEN S L.Mapper design for an SOI-based FPGA[C]//The 10thIEEE International Conference on Solid-State and Integrated Circuit Technology.Piscataway:IEEE,2010:821-823.

[8]WU Lihua.Design and verification of radiation-hardened SOI-based FPGA(Ⅰ)[D].Beijing:Chinese Academy of Sciences,2011.

A navigated mapping method for FPGA testing

ZHANG Qian-li,YU Fang,LIU Zhong-li,LI Yan

(Institute of Microelectronics,Chinese Academy of Sciences,100029 Beijing,China)

Because the FPGA factories presently do not offer the special testing function in their EDA tools,this paper addresses the design of a navigated mapping method used for FPGA testing.The navigated mapping tool totally controls the basic elements and exactly controls the usage of FPGA logic resource,tests some targetable logic of the FPGA and increases the coverage of each test vector effectively,implements the FPGA software defect-tolerance function.The result is well proven in test converage through 128 test cases.

FPGA;UCF;navigated;mapping;testing

TN47

A

0367-6234(2012)09-0144-05

2011-05-12.

张倩莉(1986—),女,博士,助理研究员;

于 芳(1960—),女,研究员,博士生导师;

刘忠立(1940—),男,研究员,博士生导师.

张倩莉,zhangqianli@ime.ac.cn.

(编辑 张 宏)