SRAM型FPGA的单粒子效应及TMR设计加固

2012-07-18黄伟刘涛王华潘卫军

黄伟 刘涛 王华 潘卫军

(北京空间机电研究所,北京 100076)

1 引言

目前,FPGA被大量的应用于星载电子设备的数据处理、探测器中流程控制以及时序发生。随着系统复杂度的增加,100万门级以上规模的FPGA已经广泛的应用于空间中[1]。然而随着器件集成度的提高和工作电压的降低,空间高能粒子对电子系统可靠性的威胁越来越大。防辐射加固是FPGA器件空间应用必须考虑的问题之一。

FPGA器件根据工艺和配置方式不同分为反熔丝型和SRAM型两种。基于反熔丝的FPGA一次烧写成型,硬件固化,抗辐射的能力相对较强;基于电可擦除可编程只读存储器(Electrically Erasable Programmable Read-Only Memory,EEPROM)配置的SRAM型FPGA更容易受到空间辐射的影响[2]。但是,基于反熔丝的FPGA器件价格贵,不能重复烧写,其逻辑门数也比SRAM型FPGA少。SRAM型FPGA因其具有丰富的资源以及灵活可配置的优点,已被广泛的应用于各种宇航电子设备中,因此有必要研究SRAM型FPGA受辐射影响的机理以及提高其防辐射性能的方法。

本文介绍了SRAM型FPGA受单粒子效应影响的机理,指明传统的TMR设计架构存在的不足,在此基础上提出了一种改进的TMR设计架构,并将该架构应用于某星载设备关键控制电路的TMR设计中。

2 SRAM型FPGA中的单粒子效应

基于SRAM的FPGA的电路功能是依靠存储在SRAM型配置寄存器中的bits位实现的。总体上可分配置区和功能区。配置区的寄存器组成配置帧,其中的配置信息用于对功能区的可编程逻辑块、可编程IO端口以及可编程互联线的硬件编程[3]。功能区按照配置Bits位信息完成指定的功能。

空间辐照环境对SRAM型的FPGA造成的辐照效应主要有:总剂量效应(Total Ionizing Dose,TID)以及单粒子效应(Single-Event Effects,SEE)[4]。总剂量效应表现为互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)器件长期受高能辐射而造成的性能退化,可以通过选择新型材料,或者改善工艺来提高器件的使用寿命[5-6]。单粒子效应表现为单个高能粒子轰击造成的器件工作异常,按照表现不同可分为单粒子翻转(Single Event Upset,SEU)、单粒子瞬态(Single Event Transient,SET)以及单粒子功能中断(Single Event Function Interrupt,SEFI)等。对于100万门的电路而言,在深层太空中每个芯片的翻转概率为1次/天[7]。因此,缓解单粒子效应对器件的威胁已经成为SRAM型FPGA空间应用应解决的首要问题。

典型6管CMOS实现的SRAM单元结构若受到宇宙高能粒子轰击,有可能导致PMOS管与NMOS结合部位电子空穴分离,从而引起正负电荷的积累。积累的电荷量较小时会引起电路上的瞬态脉冲即SET,严重时将导致逻辑翻转即SEU,也就是造成SRAM存储单元存储信息的改变。对于SRAM型FPGA,发生SEU的部位可能位于配置存储区,也有可能位于功能区。若SEU问题发生在配置存储区,可以通过将EEPROM中的信息重新载入FPGA的配置帧来解决[8];若SEU问题发生在功能区,则可以选择三模冗余设计技术来缓解。

3 传统的TMR设计架构

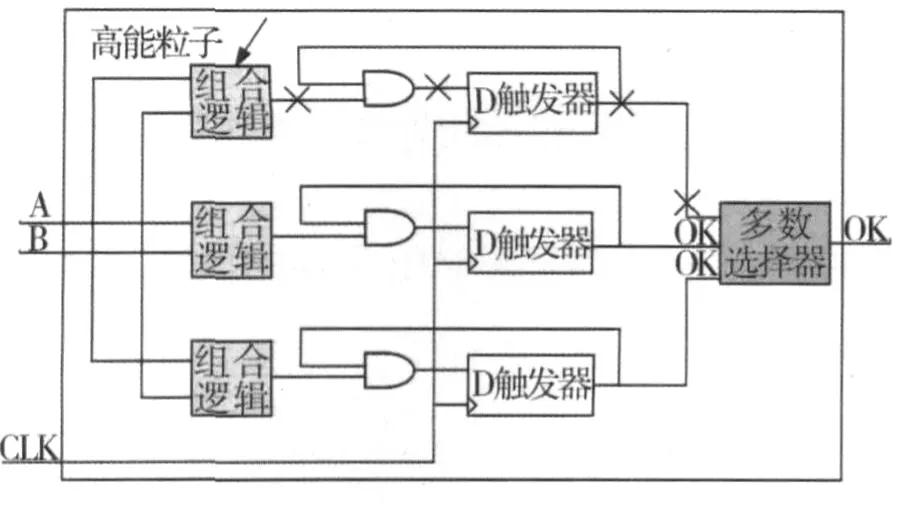

通过三模冗余设计技术可以实现对SRAM型FPGA逻辑电路的防辐射加固,该设计技术将原电路逻辑复制3份,然后添加多数选择器来缓解单粒子的影响。该架构能确保即使某一个分支发生逻辑错误,系统仍能正确运行,从而减小FPGA器件对SEU的敏感性。

传统TMR设计架构对用户逻辑(可分解为组合逻辑加上寄存器)进行了复制处理,3个相同的模块接受3个相同的输入,产生的结果送至多数选择器,选择器的输出取决于3个输入的多数,如图1所示。

假设某一天用户逻辑因SEU的影响而出错的概率为P0,选择器出错概率为P1,两者都采用FPGA中相同的逻辑资源实现,因此具有相同的数量级,根据文献[7],该数值应该小于百万分之一。TMR操作之后,用户逻辑出错的概率为PA,计算过程如式(1):

由式(1)可见,用户逻辑经TMR操作后,电路受SEU影响而出错的概率大大降低,但仍存在如下不足:

1)如图2所示,时钟线若受到SET影响,有可能使中间结果被锁存,导致输出结果错误;

2)若组合逻辑受SEU影响,由于电路没有提供寄存器错误恢复机制,导致本路错误不能恢复;

3)选择器的抗SEU的性能决定了整个TMR设计的性能,若多数选择器受SEU影响,将导致输出错误。

图1 传统TMR电路结构Fig.1 Traditional TMR circuit structure

图2 传统TMR时钟易受SET影响Fig.2 Traditional TMR’s clock vulnerable to SET

4 改进的TMR设计架构

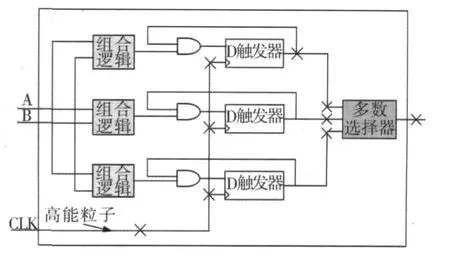

针对传统TMR设计架构的不足,图3给出了一种改进的TMR设计架构:首先将用户输入信号以及时钟进行3模备份;然后将用户逻辑复制3份,对寄存器的输出结果做多数选择,多数选择器也做3模备份;多数选择器之后添加前向的反馈回路;对多数选择器的输出结果进行少数选择处理,其结果作为输出三态门的使能,该选择器能够在本路输入与其它两路都不同时,将本路输出三态门设置为高阻。3个三态门的输出在FPGA的输出端口上实现线与。

图3 改进的TMR设计架构Fig.3 Improved TMR design framework

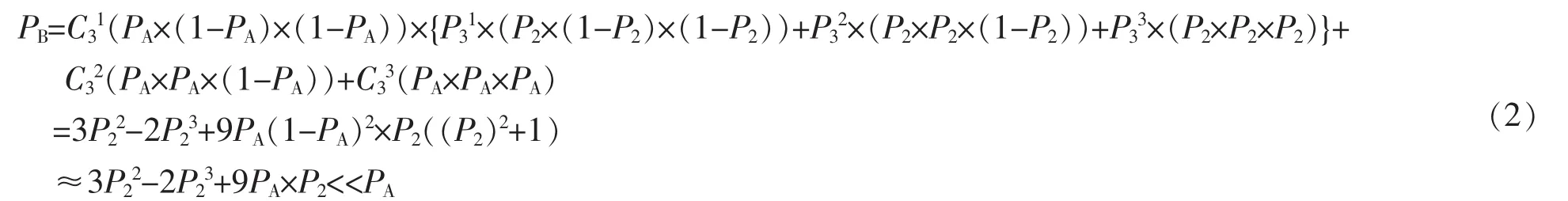

假设少数选择器某一天受SEU影响而出错的概率为P2,则该TMR设计架构受SEU影响而出错的概率PB为:

式中 P0为用户逻辑因SEU的影响而出错的概率;P1为选择器出错概率;PA为用户逻辑经过传统TMR方法加固后受SEU的影响而出错的概率。

由文献[7]可知P0,P1,P2都在百万分之一的数量级,结合式(2)可见,与传统TMR架构相比,改进的TMR架构抗SEU的能力显著提高,具有以下4个特点:

1)对输入时钟进行3模备份,即使某一路时钟受到SET影响,仍能保证结果正确;

2)多数选择器也进行了3模备份,这样即使某一选择器受SEU影响出错,仍可保证结果正确;

3)多数选择器后面添加了反馈回路,可以及时纠正由组合逻辑带来的寄存器错误;

4)FPGA对PCB板的输出端口添加了少数选择器,该选择器能够在本路输入与其它两路不同时,将本路输出三态门设置为高阻,这样就不影响正确结果输出。

为了节省有限的逻辑资源,应尽可能的选用FPGA中的底层硬件资源完成TMR所需的操作。

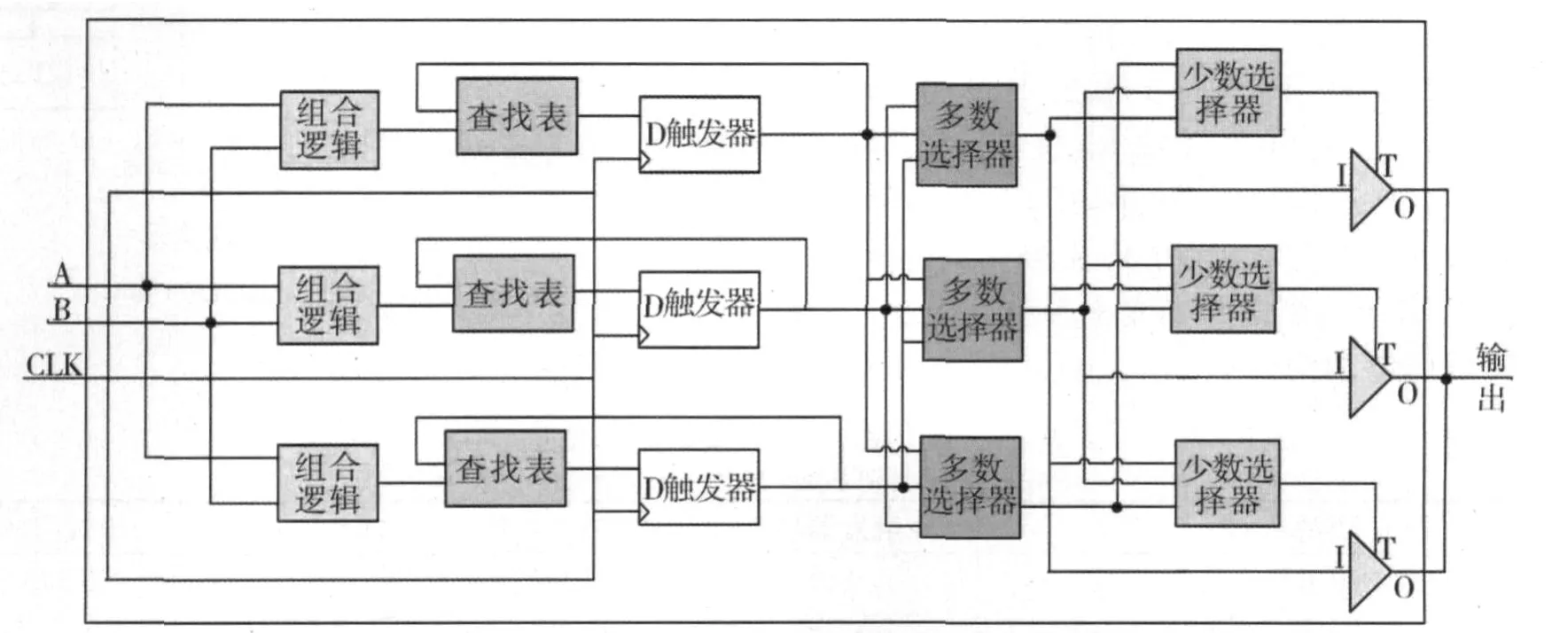

5 某关键控制电路的TMR设计

某星载设备的FPGA软件具有红外探测器时序控制及数据编码功能。顶层工程文件名为TimingTop,其中的Cp_DetClkGen模块实现对探测器的加断电控制功能,只有温度下降到某一个阈值之下,并且接收到三线串口的加电指令之后,才能够对探测器加电。若温度不满足要求或者没有收到加电指令,电路受SEU影响而给探测器加电,有可能造成探测器的永久损伤,导致系统失效,因此必须要对其进行设计加固。

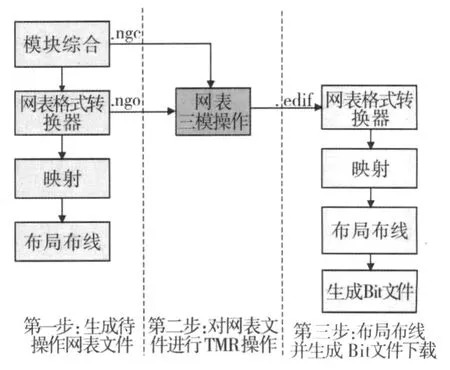

借助于集成开发环境(Integrated Synthesis Environment,ISE),将改进的TMR架构应用于Cp_DetClkGen模块,对其进行三模加固。如图4实现流程分3步:

图4 TMR实现流程Fig.4 TMR realization flow

1)建立第一个ISE工程并综合得到.ngc格式网表文件,对综合后的网表文件进行仿真;

2)对1)中得到的Cp_DetClkGen模块.ngc网表文件进行TMR操作,生成三模加固后的.edif格式网表;

3)建立第二个ISE工程,将步骤2)中的edif文件作为顶层,对其进行综合、布局布线,生成Bit文件。为了验证三模加固操作的正确性,对三模操作后的网表文件进行仿真。

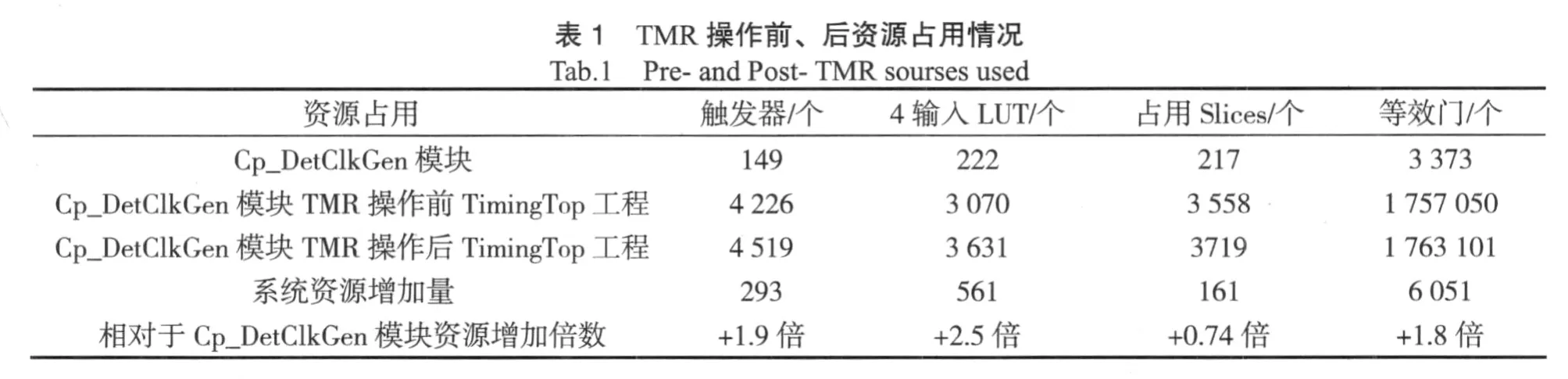

Cp_DetClkGen资源占用情况及整个TimingTop工程TMR操作前、后资源占用情况如表1所示。通过表中数据对比可见,逻辑资源增加约为Cp_DetClkGen占用资源的2倍,符合预期。

?

目前该型号电路已经在轨稳定运行,没有观察到控制电路误操作现象。

6 结束语

本文阐述了SRAM型FPGA受SEU影响的机理,分析及实践表明TMR设计方法可以有效缓解SEU对该类型器件的威胁。在分析传统TMR设计架构的不足之后,提出了一种改进的TMR架构,并利用该架构对某星载设备关键控制电路进行了TMR设计。TMR操作前后资源变化表明,改进后的方法成功的实现了对指定模块的TMR设计。

(

)

[1]万旻.FPGA在成像电路中的应用[C].中国空间技术研究院第二有效载荷专业组学术交流会论文集.北京:北京空间机电研究所,2005.

WANMin.The FPGAA pplicationin Imaging Circuit[C].The Second Payload Professional Group of Chinese Academy of Space Technology Symposium Conference Proceedings.Beijing:Beijing Institute of Space Mechanics and Electricity,2005.(in Chinese)

[2]李冬梅,王志华,高文焕.FPGA中的空间辐射效应及加固技术[J].电子技术应用,2000(8):31-33.

LI Dong mei,WANG Zhihua,GAO Wenhuan.The Space Radiation Effect and the Strengthening Technology in FPGA[J].Electronic Technology Applications,2000(8):31-33.(in Chinese)

[3]Xilinx.Virtex-II Platform FPGA User Guide[EB/OL]//www.xilinx.com

[4]NSREC Short Course,2007[EB/OL]//www.xilinx.com

[5]何玉娟,刘浩,恩云飞,等.SOI MOSFET抗辐射加固的常用方法与新结构[J].半导体技术,2008(3):33-36.

HE Yujuan,LIU Hao,EN Yunfei,et al.The Commonly Used Radiation Reinforcement Methods and New Structure of SOIMOSFET[J].Semiconductor Technology,2008(3):33-36.(in Chinese)

[6]张小平,雷天民,杨松.CMOS集成电路的抗辐射设计[J].微电子学与计算机,2003(Z1):68-70.

ZHANGXiaoping,LEITianmin,YANGSong.CMOS Integrated Circuit Design Against Radiation[J].Microelectronics and Computer,2003(Z1):68-70.(in Chinese)

[7]“Virtex II Static Characterization”Xilinx Single-Event Effects Consortium[EB/OL]Http://parts/docs/swift/Virtex2_0104.pdf,2004.

[8]刘智斌,王伶俐,周学功,等.基于动态局部重配置的FPGA抗辐射模拟[J].计算机工程,2010(14):218-226.

LIU Zhibin,WANG Lingli,ZHOU Xuegong,et al.Radiation Reinforcement Simulation Based on Dynamic Local Reconfiguration FPGA[J].Computer Engineering,2010(14):218-226.(in Chinese)