基于Si4136的小型化低损耗本振设计

2012-07-05闫文智

闫文智

中国西南电子技术研究所,四川 成都 610036

1 概述

频率合成器是现代射频系统的重要组成单元,目前在雷达、通讯、导航和仪器仪表中都得到了广泛的应用。其工作原理是以一个或多个基准频率作为参考,在内部进行四则运算,产生有同样稳定度和精确度的输出频率。频率合成的方法目前主要分为直接合成法和锁相环路法。由于锁相环路法具有频率稳定度高,抑止寄生分量强,集成度和易小型化的特点,所以应用非常广泛。本文基于Si4136芯片介绍了锁相式频率合成器的工作原理及应用设计,具有低功耗,体积小,输出频率相位噪声低等特点,可作为通信设备中超外差接收机的锁相频率合成器使用。

2 锁相式频率合成器的基本工作原理

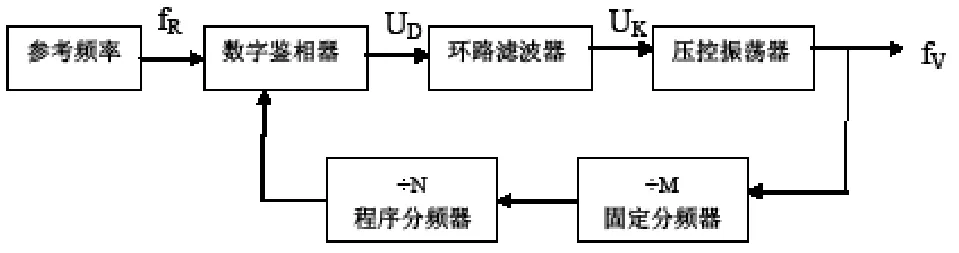

锁相式频率合成器采用了数字锁相式频率合成技术,其基本工作原理如图1所示。压控振荡器的输出频率fV经过固定分频器和程控分频器两次分频后与参考频率fR进行相位或频率的比较,在数字鉴相器的输出端产生控制电压UD,输入到环路滤波器。环路滤波器能过滤掉高频分量及噪声,平滑鉴相器的输出电压,增加系统的稳定性。环路滤波器的输出电压UK的极性与大小直接影响压控振荡器的输出频率fV,具体表现为UK的极性决定振荡频率fV的调整方向,UK的大小决定fV的频率变化大小。

在相同的参考频率fR下为了得到不同的输出频率fV,可在程序分频器中设置不同的分频比N。fR和fV关系表达式为:

fV=MNfR

式中,M是固定分频比,N是程序分频比,fR是参考频率,fV是频率合成器的输出频率。

图1 锁相式频率合成器原理图

3 Si4136的工作原理及特点

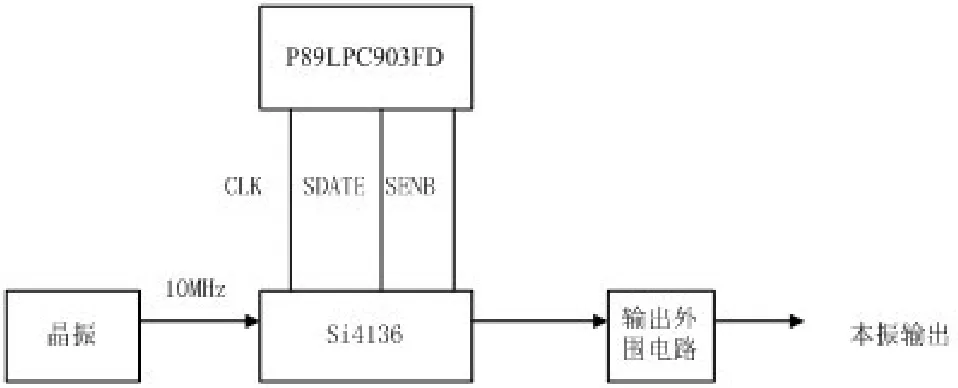

Si4136电路是美国Silicon Laboratories公司推出的含有压控振荡器的完整频率合成器,由一个中频锁相环、两个射频锁相环、三个压控振荡器和三线控制器以及一个22位的数据寄存器构成,内部结构框图如图2。

由于其芯片内部已经包含了完整的参考放大器,鉴相器,压控振荡器(VCO)及环路滤波器等锁相环路工作的必要环节,所以当Si4136作为本振设计时,只需要外部提供电源,时钟参考,单片机输出控制信号即可。

工作时,外部参考信号输入到Si4136后,经R分频器得到鉴相基准频率送至鉴相器。单片机的程序通过时钟信号CLK、数据信号SDATE和使能信号SENB等三根控制信号写入Si4136芯片,可对Si4136的各种状态进行控制及修改。

当Si4136接收到反馈回来的输出频率后,经N分频器得到分频后的反馈信号,与分频后的参考信号在鉴相器中比较,输出低频控制信号以控制内部VCO的频率,使其锁定在参考频率的稳定度上。

图2 内部结构框图

Si4136电路具有以下特点:

1)具有一个中频锁相环,两个射频锁相环;

2)内部含有完整的频率合成器,包括了压控振荡器、环路滤波器、鉴相器等部分;

3)输出信号相位噪声低;

4)功耗低。在3V电压下待机电流小于1μA,工作电流小于18mA;

5)体积小。采用24脚TSSOP封装。

4 本振电路设计

图3 本振设计系统框图

图3为本振设计的系统框图。本文以产生频率为fo=2400MHz的本振信号为例,设计中采用10MHz晶振作为本振电路的输入参考,即fREF=10MHz。Si4136可允许的鉴相频率fφ范围为0.01MHz~1MHz,设计中就以fφ=1MHz为环路的鉴相频率计算,所以参考时钟分频器R=fREF/fφ=10。由于Si4136中射频锁相环含有一个固定的2分频器,由关系式:FVOC=(P*B+A)*FREF/R知,计算得出N=1200。即可得出产生2400MHz本振,由单片机写入控制寄存器的控制字分别为R=(000A)16,N=(04B0)16。

本振输出端口,为了驱动外围50欧的负载,需要在输出端口加入匹配电路。当fo>500MHz时,匹配电路如图4所示。

图4 匹配电路图

5 实验结果

利用频谱分析仪对Si4136产生2400MHz的单载波信号进行测试,其相位噪声测试图如图5所示,相位噪声指标为:<-70dBc/Hz@100Hz,<-80dBc/Hz@1kHz, <-90dBc/Hz@10kHz,<-105dBc/Hz@100kHz,满足工程设计的需求。

图5 2.4GHz相位噪声图

6 结论

采用Si4136构成的锁相式频率合成电路已广泛应用于众多射频收发本振设计当中,它的小型化低损耗已越来越显示出自身的优点。

[1]张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,1994.

[2]仇善忠,张冠百.锁相与频率合成技术[M].北京:电子工业出版社,1996.

[3]周洪敏,王红玉,顾艳丽.直接数字频率合成技术及其设计方案[J].科技咨询导报,2007(24):127-128.