孤立接触孔掩模显影工艺优化

2012-07-04张海平周家万

张海平,尤 春,周家万,陈 卓

(无锡中微掩模电子有限公司,无锡214035)

掩模(Mask),又称光刻板,是大规模集成电路芯片生产最重要的元件之一。在掩模的生产制作过程中,主要有曝光—显影—量测—刻蚀—量测—去胶—量测—检验—修补—清洗—贴膜等工序。其中,显影、刻蚀和去胶后的量测是为了监测掩模图案指定区域的线条宽度(CD)值与设计值之间的差别,从而达到实时监控掩模的制造工艺,保证掩模生产质量。

在实际生产过程中,掩模孤立区域的接触孔经过显影之后量测值(ADI)往往会比设计值偏大。针对这种现象,本文主要研究了通过优化线条偏差(CD Bias)、显影流量(flow)、显影时间(time)、落点、烘烤(Baking)等参数,从而达到改善ADI 偏大的问题。

1 实验

通过选取孤立区域接触孔为3 μm 的图案来进行实验,此掩模图案是由8 个相同图形重复排列组成。选取6 片工程片来进行该项试验。对6 片工程片进行编号:1#、2#、3#、4#、5#、6#。1#片进行未做任何参数修正的实验;2# 片进行CD Bias 修正的实验;3# 片进行显影机的显影流量、显影时间、落点等参数修正的实验;4#、5# 片进行Baking修正的实验;6#片进行CD Bias、flow、落点、Baking 等参数综合修正的实验。

在实验的过程中,6 片实验片的流程相同,除了针对每片修正参数不同外,其余工艺参数都相同,经过显影之后选取的量测点坐标也一样,具体实验如下。

1.1 未做参数修正的显影实验

1#片进行未做任何参数修正的实验。其按照正常流片程序经过曝光、显影之后进行量测,具体量测结果如表1 所示,孤立接触孔光学显微镜下实物图像及检测设备下图案示例分别见图1、图2。

表1 1# 片孤立接触孔ADI

图1 光学显微镜下实物图像

图2 检测设备检验结果(die to database)

从上述实验结果,我们可以看出,没有经过任何参数修正的孤立接触孔显影之后的量测值比设计值偏大250~1000 nm,远远超出线条容差范围(CD Tolerance)。

1.2 CD Bias 参数修正的显影实验

2#片进行CD Bisa 修正的实验。参考表1 的实际量测值,通过6 种CD Bias 值对掩模8 个图案中的6 个进行相应优化,其余2 个图案不变化。然后经过曝光—显影之后进行量测,具体的量测值见表2。

表2 2# 片孤立接触孔ADI

从表2 可以看出,经过CD Bias 修正的孤立接触孔,可以很好地改善显影之后量测值偏大的现象。不过此种做法增加了数据处理的难度,需要消耗大量的人力和设备,在bias 处理上,不适用于大生产。另外此种方法也有局限性,如果缺陷数量过多的话就不能进行CD Bias 修正了。

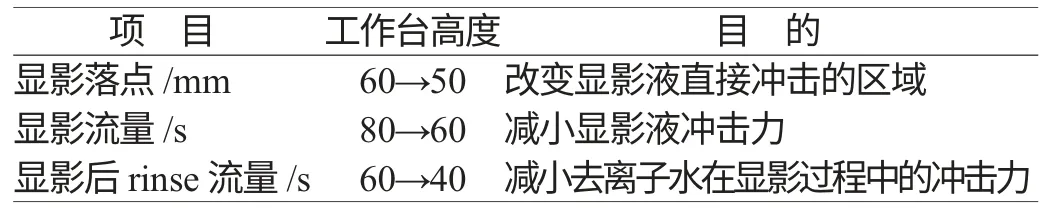

1.3 显影机流量等参数的修正实验

3# 片进行显影机流量、时间、落点等参数修正的实验。3# 实验片经过曝光之后,在显影的过程中,优化显影机的显影流量、显影时间、落点(具体参数修正见表3 所示)。然后再进行量测,具体的量测值如表4 所示。

表3 3# 片孤立接触孔ADI

表4 显影机落点、流量等参数调整情况

从表4 我们可以看出,修正显影机显影参数,对部分CD 值的改进有一定帮助,但还是不能达到线条容差值的范围,不能满足实际生产要求。

1.4 增加Baking 的显影实验

4#、5#片进行Baking 参数修正的实验。4#片在掩模曝光之后显影之前,增加一Baking 过程:119.5℃,5 min。经过显影之后进行量测,其具体量测值如表5 所示。通过表5 我们可以看出,显影之前增加一Baking 过程,可以比较明显地改善这一现象。

表5 4# 片孤立接触孔ADI

5# 片在掩模曝光之后显影之前,增加一Baking 过程:119.5 ℃,30 min。经过显影之后进行量测,其具体量测值如表6 所示。

表6 5# 片孤立接触孔ADI

通过表6 我们可以看出,增加烘烤时间对CD改善不大。

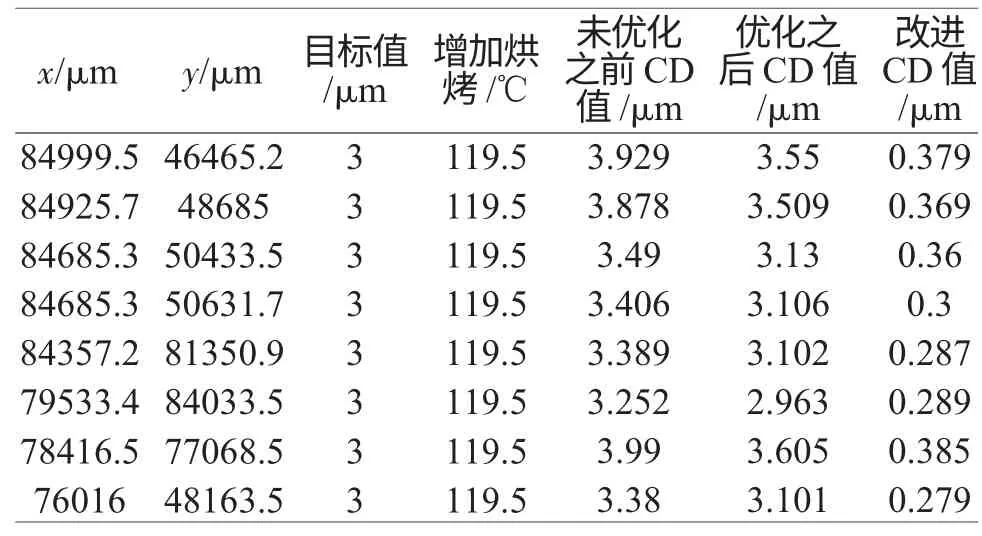

1.5 所有参数综合修正的显影实验

实验五:6# 进行CD Bias(按一固定值对所有的孤立接触孔进行统一修正,减少数据处理难度和时间)、显影机flow、time、落点、压力值、Baking等参数修正的实验。6# 片经过曝光之后,按照左右参数优化值进行显影,然后再进行量测,具体量测值如表7 所示。

表7 6 # 片孤立接触孔ADI

从表7 可以看出,经过上述参数的优化之后,接触孔的量测值与设计值的差值在容差范围内。因此,通过优化CD Bias、显影机的显影流量、显影时间、落点、增加烘烤过程可以显著地改善孤立接触孔显影之后量测值偏大的问题。

2 结 论

大规模集成电路芯片的缺陷对其后续电路的性能影响非常大,现在社会对芯片的质量要求非常高。质量合格的掩模是集成电路芯片生产的前提。本文通过实验的方法,找出了解决掩模孤立接触孔显影之后偏大的方法,可以用来指导掩模的实际生产,保证掩模的生产质量。

[1] Benjamin G.Eynon,Jr.,BanQiu Wu.Photomask Fabrication Technology[M]. 2005.

[2] GB/T16880-1997,光掩模缺陷分类和尺寸定义的准则[S].

[3] I.Kagami,Makuhari,Japan.A sludy on photomask Defect printability and quality assurance for 0.13 μm technology[M]. proc. SPIE VoL. 4186:2000.