SEM在半导体工艺研究中的应用实例

2012-07-02王嵩宇宁润涛

王嵩宇,刘 剑,宁润涛

(中国电子科技集团公司第47研究所,沈阳 110032)

1 引言

扫描电子显微镜(SEM)诞生以来,渐已成为人们观察和检测各种材料的有力工具,尤其在微米、亚微米乃至纳米领域。在20世纪90年代初,大规模特别是超大规模集成电路的研制及生产中,SEM是亚微米时代关键尺寸(CD)控制的主要仪器。SEM在获取微观失效证据方面作用突出,其报告在失效分析中不可替代。它是介于透镜和光镜之间的一种微观形貌观察手段,可直接利用样品材料表面的物理特性进行微观成像,具有较高的放大倍数,有很大的景深,成像富有立体感,可直接观察凹凸不平表面的细微结构。

2 原理

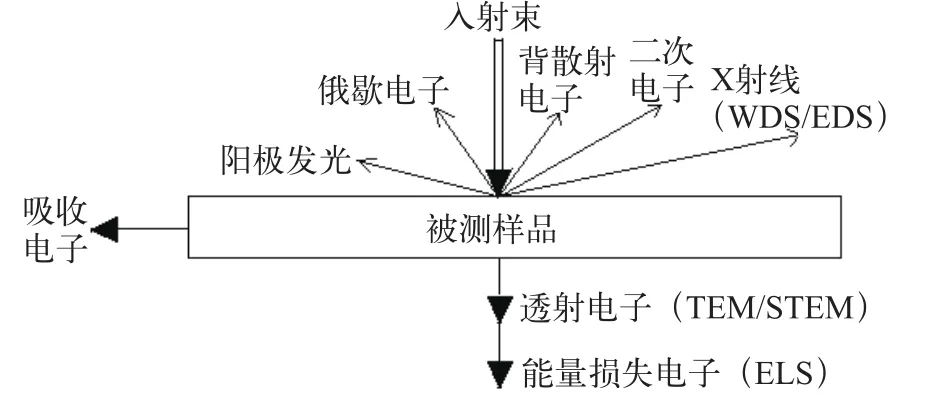

SEM的基本工作原理是加速阴极所发射的电子束,聚焦后形成电子束流。这束高能电子束轰击到样品表面激发出各种信息,经收集、放大后,就在荧屏上得到各种相应的图像。扫描电镜主要利用二次电子像来作形貌观察,其产生数量随着原子序数的变化而变化,它主要取决于表面形貌。二次电子像可以观察芯片表面金属引线的短路、开路,剖面各层介质的台阶形貌,还可用来作为图形线条的尺寸测量等。很多电子元器件、集成电路及工艺的失效分析步骤都是首先借助SEM手段,对失效模式和机制作出基本的判定;即使不能立刻作出准确判断,整体失效分析思路也会以扫描电镜的分析结果为依托,并作为重要图像及基本组份数据采集平台,然后再借助于其他实验手段确定失效模式和机理,并提出相应的改进方法。

图1 电子束与物质相互作用产生的信息

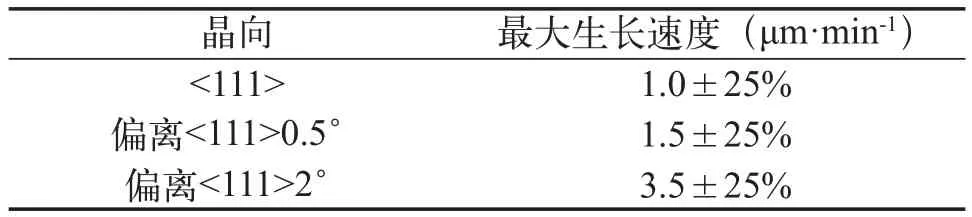

表1 外延最大生长速度与晶向的关系

3 方法

扫描电镜剖面分析技术应用到集成电路的研制与生产中,必须根据不同的器件、不同的工艺情况,以确定相应科学合理的样品制备条件。下面将所应用的关键技术手段介绍如下:

首先根据要分析的位置,用金刚刀将样品划断。如果在管芯中有多个重复单元,就应该按解理方向进行解理,半导体样品的断口不仅要求准确,而且还需要进行相应的缀饰,用以暴露所需要的结构细节部分,在缀饰后要将表面或断口清洗处理干净,其主要目的就是最大限度地呈现样品的特征信息。样品大小必须适合设备专用样品座尺寸,一般小样品座直径为3mm~5mm,大的样品座直径为Φ30mm~50mm,后者可以分别用来放置不同大小的样品,样品的高度也有限制,不同的设备有不同的要求,一般在5mm~10mm左右。

扫描电镜对样品的基本要求是导电性良好,对于那些导电性较差的材料,需要先进行镀膜处理,在材料表面形成一层导电薄膜,既可以避免电荷积累,影响图像质量,也可以防止试样的热损伤。镀膜的方法有两种,一是真空镀膜,另一种是离子溅射镀膜。离子溅射镀膜方式装置结构简单,使用方便,消耗贵金属少,每次仅约几毫克,溅射耗时短;而真空镀膜方式则要半个小时以上。另外对同一种镀膜材料来说,离子溅射镀膜方式质量好,能形成更细颗粒、更加致密、均匀且附着力更强的膜。

4 应用分析实例

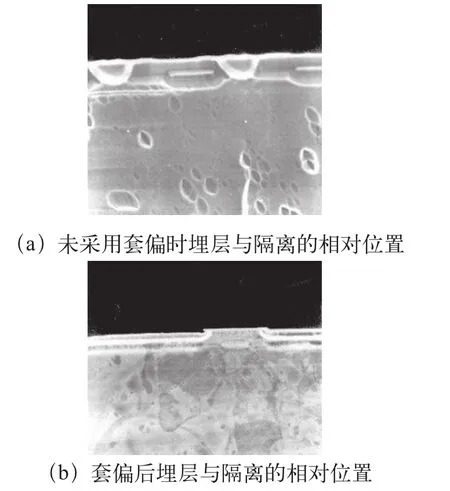

4.1 埋层漂移

在双极型集成电路中,为降低NPN管收集极的串联电阻,都需要做N+埋层,而对于有纵向结构PNP管的电路还要在N+埋层上做P型埋层。但是埋层图形在形成外延后会产生漂移,这种现象将导致光刻隔离区时无法与埋层图形对准,造成“隔不透”。外延漂移主要影响是在外延隔离上,造成岛与岛之间击穿电压为零,隔离不成功。发生埋层漂移时,部分埋层可能会与隔离槽发生短路。即使在隔离工艺正常完成的条件下,N+埋层也不易被隔离的P+扩透。因此,隔离槽底部仍有N+把相邻的隔离相连,岛与岛之间击穿电压为零,产生未隔离透的现象。另外,反应室型式、压力,外延生长温度、速率、厚度、硅源等都是影响埋层图形漂移的因素,<100>比<111>晶相图形畸变小。我们借助SEM剖面分析,确定埋层漂移的方向及距离,在光刻时根据这个结果对版图进行修改,采用定向、定值套偏的方法,很好地解决了这个问题,从根本上提高了产品的成品率及可靠性。埋层漂移见图2。其中照片(a)为未采用套偏时埋层与隔离的相对位置,照片(b)为套偏后埋层与隔离的相对位置。如果产品设计时埋层与隔离之间的尺寸宽余,可不必校正,正常的隔离工艺也不会造成埋层与隔离岛相连。对于埋层与隔离之间尺寸要求苛刻的电路则必须采用埋层漂移套偏,否则会造成功能失效。

图2 SEM照片

4.2 MEMS器件

MEMS(微型机电系统)是在半导体技术基础上发展起来的一门新型科学技术,涉及各学科的交叉以及多种工艺的应用。MEMS电路大多数都是由复合薄膜构成,通过薄膜腐蚀及牺牲层释放实现。因为在工艺过程中产生残余应力,造成结构形状、尺寸发生变化,过大的残余应力致使MEMS器件发生翘曲破坏。因此,研究MEMS器件残余应力是相当重要的问题。图3(a)是微桥电路,上部是桥面结构,下面是电路部分,该位置同时显示了这两部分结构,并且定位了因为残余应力断裂开的悬臂梁,这在光学显微镜下是无法实现的。针对此问题的监控进行了工艺改进,大大降低了去除牺牲层过程中残余应力的释放,同时使悬臂梁的强度有了质的提升,顺利通过客户验收。对于MEMS工艺及器件的研究,SEM的高放大倍数和立体感极强的景深,是其他观测设备无法比拟的。

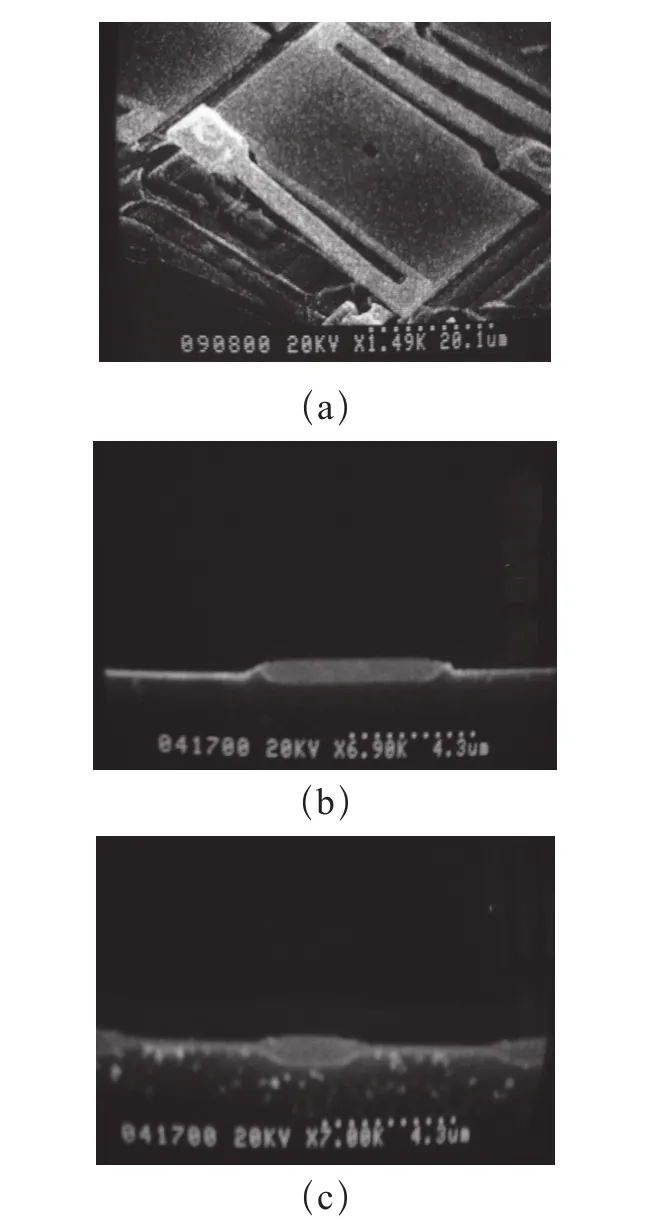

4.3 PBLOCOS技术

PBLOCOS(硅局部选择氧化法)的目的是在电路的场氧化工艺过程中减小“鸟嘴”长度,保证有源区的有效面积。随着沟道长度的减小,器件有源区的尺寸也越来越小,用LOCOS(局部选择氧化法)方法形成的有源区“鸟嘴”区相对太长,采用PBLOCOS工艺技术可以大幅度减小“鸟嘴”长度。在局部选择氧化工艺中,利用氧在氮化硅中扩散缓慢,当硅表面有一层氮化硅时,无法生成二氧化硅,只在没有氮化硅保护的区域生长了二氧化硅层。但氮化硅薄膜沉积在硅表面时会显出较高的应力,因此在它下面增加了一层用来缓解应力的预氧层,预氧层越厚,传给硅衬底表面并会引起晶格错位的应力越小,但氮化硅屏蔽氧化的作用也随之降低。因为,这时横向氧化作用加大,有源区的“鸟嘴”就变长。在PBLOCOS技术中,用多晶硅缓冲层取代大部分二氧化硅缓冲层,并用较厚的氮化硅层作屏蔽,可以取得较好的结果。选择等平面氧化时,通常在氮化硅与硅之间预先热生长一层薄二氧化硅,以防止氮化硅与硅之间的应力失配导致表面缺陷。但这层二氧化硅在进行选择氧化时,会产生横向氧化,二氧化硅越厚,横向产生的“鸟嘴”就越大。高压低温氧化能够缩短氧化时间,降低氧化温度,有利于减小“鸟嘴”。我们则是通过降低氮化硅厚度,或在氮化硅与预氧化层之间加一层多晶硅等方法,达到上述目的。参见图3(b)、(c)。PBLOCOS技术与CMOS工艺兼容,完全可以应用在CMOS工艺流程中。

图3 SEM照片2

5 结束语

随着集成电路工业的发展,半导体元器件的可靠性问题已越来越引起人们的重视。对于科研生产来说,工艺及产品的失效分析具有非常重要的意义,SEM则是其中重要的技术手段,尤其在线检测更是物尽其用。SEM常与其他分析技术结合使用,如EDX、FIB。可以大胆地设想,随着IC加工水平向90nm、65nm乃至量子器件的迈进,整合SEM、TEM、FIB功能的半导体加工设备一定会在不久的将来出现。积累SEM技术在IC元器件微观结构和失效机理方面的经验,在隐患的缺陷演变为问题之前就加以解决,最大程度避免大规模的分析调查;可为产品设计、工艺控制等提供科学依据,对于提高成品率、可靠性具有重要的意义。

[1] 郝秀云,杨洁. 塑封器件中高聚物的失效分析[J]. 电子与封装,2011,11(5).

[2] 吴兵,薛智民,王清波,陈宝忠. 高速BiCMOS外延工艺研究[J].电子与封装,2010,10(7).

[3] 汪继芳,刘善喜. RF MEMS开关工艺技术研究[J].电子与封装,2010,10(3).

[4] Stephen A. Campbell. 微电子制造科学原理与工程技术[M].北京:电子工业出版社.

[5] 《电子工业生产技术手册》编委会,编. 电子工业生产技术手册(7)·半导体与集成电路卷[M].北京:国防工业出版社.

[6] 张有纲,罗迪民,宁有功. 电子材料现代分析概论(第二分册)[M]. 北京:国防工业出版社.