IC设计中的ESD保护技术探讨

2012-07-02曹燕杰华梦琪吴海宏

曹燕杰,王 勇,朱 琪,华梦琪,吴海宏,张 勇

(中科芯集成电路股份有限公司,江苏 无锡 214072)

1 ESD在IC设计中的重要性

为了避免集成电路在生产过程中被静电放电所损伤,在集成电路内皆有制作静电放电保护电路。静电放电保护电路是集成电路上专门用来做静电放电保护的特殊电路,静电放电保护电路提供了ESD电流路径,以免ESD放电时电流流入IC内部而造成电路损伤。

静电放电(Electrostatic Discharge,ESD)是造成大多数电子器件或电子系统受到过度电性应力(Electrical Overstress,EOS)破坏的主要因素。这种破坏会导致半导体器件或电子系统形成一种永久性的毁坏,因而影响集成电路(Integrated Circuits)的电路功能,使得电子产品工作不正常。 而静电放电破坏的产生,多是由于人为因素所形成,但又很难避免。电子器件或系统在制造、生产、组装、测试、存放、搬运等的过程中,静电会累积在人体、仪器、储放设备等之中,甚至在电子器件本身也会累积静电,而人们在不知情的情况下使这些物体相互接触,因而形成了一条放电路径,使得电子器件或系统遭到静电放电的损害。

如何才能避免静电放电的危害呢?除了加强工作场所对静电累积的控制之外,必须在电子产品中加入具有防患静电放电破坏的装置。首先必需考虑这额外装置的效能,如何处理才能达到有效保护的功用。同时装置应放在何处,以及在工业上的大量应用中如何才是最省成本的设计方式都是应一一处理及考虑的问题。

在保护装置的设计上,从加强集成电路本身对静电放电的耐受能力上着手,可以解决芯片包装后组装、测试、存放、搬运等所遭遇到大多数静电放电的问题。

静电放电保护电路(ESD protection circuits)是集成电路上专门用来做静电放电保护之用,此静电放电保护电路提供了ESD电流路径,以免ESD放电时静电电流流入IC内部而造成损伤。人体放电模式(HBM)与机器放电模式(MM)的ESD来自外界,所以ESD保护电路都是做在PAD(芯片压焊点)的旁边。在输出PAD,其输出级大尺寸的PMOS及NMOS器件本身便可当作ESD保护器件来用,但是其布局方式必须遵守设计规则中有关ESD布局方面的规定。在输入PAD,因CMOS集成电路的输入PAD一般都是连接到MOS器件的栅极(gate),栅氧化层容易被ESD所打穿,因此在输入PAD的旁边会做一组ESD保护电路来保护输入级的器件。在VDDpad与VSSpad的旁边也要做ESD保护电路,因为VDD与VSS脚之间也可能遭受ESD的放电。

2 IC设计中对ESD设计的要求

IC设计对ESD设计的要求可以分成4类:健壮性、有效性、速度、透明性。好的ESD设计必须满足这4个要求。

(1)健壮性指的是ESD保护电路能够承受的ESD电流的能力;

(2)有效性是指ESD保护电路能把电压限制在安全值以下,不使被保护电路失效;

(3)满足了健壮性和有效性的ESD保护电路,必须有足够快的速度把ESD降低到安全水平;

(4)透明性是最后一个优秀的ESD保护电路的指标,要求ESD保护不影响I/O电路和芯片的正常工作,这包含I/O的参数和电路的规范。例如:

(a)电容:ESD保护电路不应该有太大的电容,违背I/O信号的负载限制。

(b)漏电:在I/O,高电平或低电平时没有超规范的漏电,也包含电源-地之间没有大的漏电。

(c)上电顺序:ESD保护电路不会影响正常的上电顺序。

(d)热插拔:当有要求时也不能违背。

(e)过压状况:在混合电压端口,如3.3V/5V,ESD保护电路表现正常。

(f)Latchup:不能造成芯片的latchup。

透明性对高频端口和低漏电电源尤其重要。

3 常见的ESD设计方法或注意点

3.1 ESD 保护策略介绍

在静电保护的各种手段中,最主要也是最有效的方式还是在集成电路内部电路结构设计时加入静电保护电路结构。静电保护结构的作用就是在静电电压产生时能将其安全地释放,防止其被导入器件内部工作电路。实际上,设计有效的静电保护结构是一个长期的、不断发展的过程。一个好的、具有较强抗静电能力的保护结构,往往要进行很多次重复的改进才能完成。而且,原有的一些比较成功的保护结构,随着器件尺寸的不断减小以及工艺技术的改进,其可靠性和有效性会大打折扣,因此需要不断改进甚至重新设计新结构。

3.2 ESD保护器件介绍

在ESD冲击发生时,ESD保护电路必须保证及时地释放ESD能量,并且保护电路本身必须能够承受大电流。所以ESD保护电路必须要具有较低的击穿电压(breakdown voltage)或者较快的触发速度,形成低阻通路,并均匀地释放ESD能量。因此这就对ESD器件在大电流、高电压情况下的工作机制提出了一定的要求。这些器件的工作机制与它们在正常工作状态下的机制有很大不同。在这里简要叙述了常用ESD保护结构构成的器件在ESD状态下的特性和工作机制。这些器件包括半导体电阻、传统的二极管(正反向)、厚氧化层(Field-oxide)器件、NMOS管。

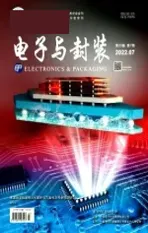

图1 各种ESD保护器件的I-V特性

从图1器件的I-V特性可知,各种ESD保护器件在正向偏压及反向偏压之下,其工作电压是不同的,例如二极管在正偏的工作电压约在0.8V ~ 1.2V左右,但是该二极管器件在反偏的工作电压约在-13V~-15V左右。因此,当相同大小的ESD放电电流流经该二极管器件时,在反偏情形下所产生的热量远大于该二极管在正偏情形下的热量,也就是说在器件尺寸大小相同的前提之下,二极管器件在正偏所能承受的ESD电压远大于在反偏所能承受的ESD电压。因此,如何设计一个具有高ESD承受能力但只占用小布局面积的ESD保护电路必须考虑器件在不同偏压之下的特性。

至于MOS器件或厚氧化层(Field-oxide)器件的ESD承受能力,跟该器件的二次击穿电流(It2,secondary- breakdown current)有关。当ESD放电电流大于该器件的It2时,该器件便会造成不可回复的损伤。

3.2.1 电阻

电阻往往起到限流、分压等作用。MOS工艺一般采用多晶硅电阻、P+或N+扩散电阻、P阱或N阱扩散电阻来实现。在ESD保护结构中也要用到电阻,起的作用主要也是限流和分压。但是ESD的释放是短时间高能量的释放,这种情况下这些电阻都会表现出不同的特性。

多晶硅电阻并不适用于ESD保护结构。因为ESD冲击发生时,ESD保护结构要释放ESD的能量,而多晶硅电阻与衬底间有二氧化硅隔离,使多晶硅电阻在ESD冲击发生时散热不良,主要失效模式是熔断开路而破坏电路性能,因此不推荐使用。而N+、P+、N阱、P阱等扩散电阻在ESD冲击发生时会进入非线性区。这是因为,扩散电阻是载流子在电场E作用下的定向漂移运动形成的:Vd=uE,其中Vd是载流子的漂移速率。而ESD具有相当高的电压,当ESD冲击发生时,载流子的速率将达到饱和速率Vs;再增大电压将只会增大电场,而不会增大电流密度,器件进入饱和状态。在扩散电阻中,若电流到达一定程度(数量)时电流会被限制,若继续增大电压,载流子反复撞击产生大量空穴电流,当空穴电流足够影响总电流时,会出现负阻现象;这时电压开始下降,只要较低的电压就可以维持较大的电流。在ESD可靠性研究中扩散电阻的高电流行为已经被大量研究;但需注意在更高的电流等级下电阻最终发生永久热失效,因此设计时必须考虑到其能量释放的密度问题。

3.2.2 二极管(diode)

二极管结构作为ESD保护器件被广泛使用很长时间。二极管拥有良好的电流导通特性(50mA/μm)和很低的导通阻抗。因此,在1.5μm工艺以下ESD保护器件主要使用MOS管和场管,利用它们寄生的npn管的snapback特性。

二极管,在Vdd-Vss间有足够好的ESD保护电路,能够利用其优秀的正偏特性正常工作,而不需要工作在反向击穿。另外,二极管不像其他保护器件如MOS管、SCR结构有latch-up风险。

3.2.3 厚氧化层(field oxide oxide)器件

场管作为ESD保护器件主要使用在特征尺寸从1μm到3μm的工艺里。实际上,场管主要以寄生的横向npn工作。在大尺寸工艺中,场管的ESD性能好是因为寄生npn管工作区域离硅表面更远,产生的热量远离硅表面。

就ESD而言,场管的主要参数有:沟道长度(L)、漏端的孔到扩散区边缘的距离(DS)、沟道宽度(W)。关于DS这个参数,增大DS,一方面增加了漏端的串联电阻,另一方面可以增大寄生npn管的有效导通区域,有利于提高ESD水平。但如果DS过大,可能会造成接触孔和衬底的穿刺现象(contact spiking)。常见的解决办法是在接触孔下放n-well,这样击穿就不会发生在接触孔的下面了。

对于突变结工艺,漏端的孔到扩散区边缘的距离(DS)非常关键,但当轻掺杂漏(LDD)结的引入,增大DS的效果就变差了。当引入硅化物(silicide)工艺时,增大DS的效果就完全没有了。原因是硅化物大大减小了接触孔到沟道的电阻。最有效的解决办法是在接触孔到扩散区边缘之间阻挡硅化物的形成。

3.2.4 NMOS管

在深亚微米工艺中,NMOS管有更好的ESD性能。研究表明,0.1μm工艺里的NMOS管的ESD能力比1μm工艺的好。这主要由于随着尺寸的缩小,击穿电压和snapback维持电压减小,产生的功耗降低。

NMOS管的主要设计参数有:沟道长度(L),漏端的接触孔到栅的距离(DCG),沟道宽度(W)。对于1μm以上的工艺,一个典型的设计参数为:晶体管的W=200μm,L约大于最小沟道长度,DCG =6μm。关于多个MOS管并联设计的晶体管,ESD性能并不能随着并联管子个数的增加而正比例增大,除非使用其他的技术,比如栅耦合、衬底触发技术。单个MOS管的沟道宽度也必须进行优化,作为经验推荐单个管子的沟道宽度为40μm~80μm。

3.3 ESD保护电路介绍

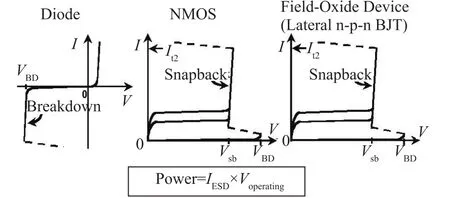

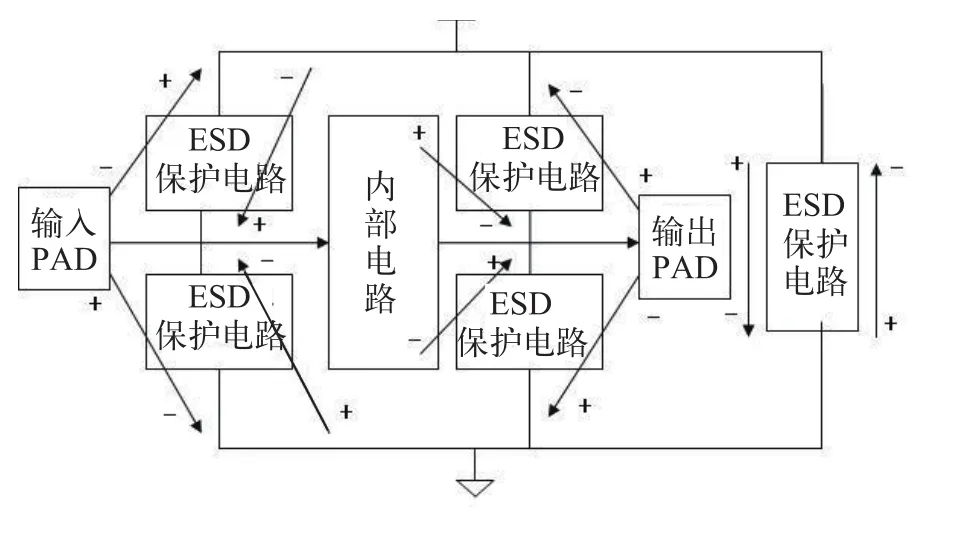

ESD保护电路的布局必须全方位考虑到ESD测试的各种组合,因为整颗IC的所有脚中,在各种测试模式下最低的ESD耐压值为该颗IC的ESD failure threshold。因此,一个全芯片ESD保护电路的布局要如图2所示。Input pad与Output pad要具有保护PS、NS、PD、ND四种模式的静电放电,静电放电模型如图3所示。另外,VDD到VSS也要有ESD保护电路,静电放电模型如图4所示。

图2 全方位静电放电保护电路的安排

图3 I/O Pin的静电放电测试组合

(1)PS-mode:VSS脚接地,正的ESD电压出现在该I/O脚对VSS脚放电,此时VDD与其他脚皆浮接;

(2)NS-mode:VSS脚接地,负的ESD电压出现在该I/O脚对VSS脚放电,此时VDD与其他脚皆浮接;

(3)PD-mode:VDD脚接地,正的ESD电压出现在该I/O脚对VDD脚放电,此时VSS与其他脚皆浮接;

(4)ND-mode:VDD脚接地,负的ESD电压出现在该I/O脚对VDD脚放电,此时VDD与其他脚浮接。

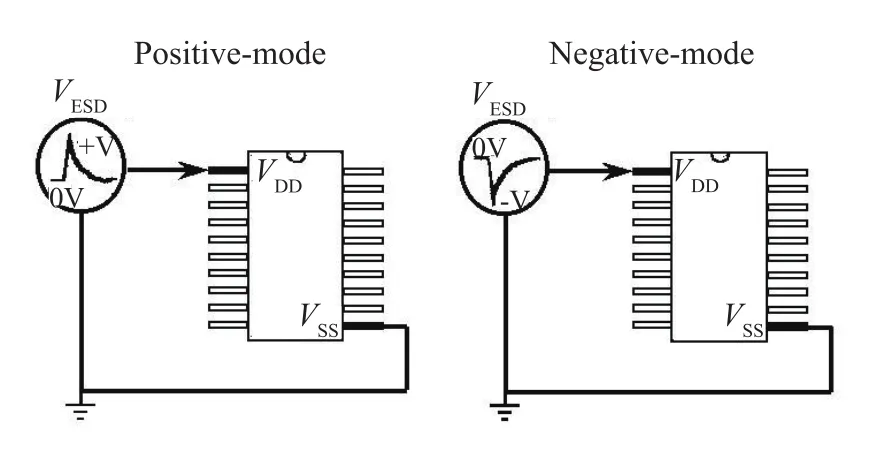

图4 VDD to VSS的静电放电测试组合

(1)Positive-mode:正的ESD电压出现在VDD脚, 此时VSS脚接地,但所有I/O 脚皆浮接;

(2)Negative-mode:负的ESD电压出现在VDD脚,此时VSS脚接地,但所有I/O 脚皆浮接。

因为ESD保护电路是为了保护ESD而加入的,在集成电路正常操作情形下ESD保护电路不工作,因此在加入ESD保护电路于集成电路中时必须要考虑到之前所列举的注意事项。其中,在设计上除了要能符合集成电路所要求的ESD保护能力之外,也要尽可能降低因为加上该ESD保护电路而增加的成本,例如布局面积的增大或者制造工艺的增加等。

另外,在一些ESD保护电路中,尤其是在Input pad,其ESD保护电路只安排在Input pad与VSS之间,Input pad到VDD之间没有安排ESD保护电路。当ND模式的ESD放电发生时,负的ESD电压会先经由Input到VSS之间的ESD保护电路跑到VSS电源在线,沿着VSS电源线流向VDD与VSS之间的ESD保护电路,再经由此VDD与VSS之间的ESD保护电路转到VDD电源在线,最后由VDDpad流出此IC。

ND模式的静电放电是藉由Input到VSS以及VDD与VSS之间的ESD保护电路来旁通ESD电流。有些加了Input到VSS之间的ESD保护电路,却忘了加上VDD与VSS之间的ESD保护电路,这时在ND模式ESD测试组合之下,集成电路的内部电路常常先被ESD放电电流所损坏,但是在Input pad上的ESD保护电路却毫发未伤,这种内部电路损伤无法自Input pad的I-V变化观测得到,必须再经由IC功能测试分析才会发现。随着芯片的尺寸越做越大,环绕整个芯片的VDD与VSS电源线也越拉越长,寄生的电容电阻效应便会显现出来,当IC的布局造成电源线的杂散电容电阻效应,这些杂散电阻电容会延迟ESD电流经由VDD与VSS之间的ESD保护电路旁通而过。这时,来不及放电的ESD电流便会借着电源线的连接而进入到IC内部电路中,IC内部电路在布局上一般都以最小尺寸来做,也不会考虑ESD的布局方式,因此其更易被此种ESD电流所损伤。因此造成异常的ESD损伤现象,也就是在I/O pad上的ESD保护电路完好,但内部电路已失效,这种内部损伤是无法从单一输入脚或输出脚的I-V变化看出来的。

因此,当芯片尺寸较大时,必须要在Input pad与VDD之间也提供ESD保护电路来直接旁通ESD电流,而不能只借由VDD与VSS之间的ESD保护电路来间接放电。

4 深亚微米工艺中的ESD设计方法

在进入深亚微米的CMOS工艺中,为使MOS管能符合各式各样的应用,器件中的杂质分布及结深都有了许多改变,然而这些工艺参数都会影响到器件对静电放电的防护耐受度。在半导体代工盛行的今天,一旦工艺发展稳定后,为了在集成电路中设计出有竞争力的静电放电保护电路,设计工程师就仅能从选择适当器件以及改变其版图几何结构上来做变化,以实现具有最佳静电放电防护能力的防护装置。在作为静电放电防护的器件中,以MOS晶体管的导通特性用做静电放电防护最适合,因此通常在设计静电放电防护电路时,多以MOS晶体管为主。

这里介绍一款LED驱动芯片的ESD保护结构。芯片只有一对电源和地,在ESD构架方面比多对电源和地的芯片更简单。可以分为几种情况:输入保护、输出保护、电源和地之间的保护。ESD保护的设计除了使芯片免受静电的损伤,还要考虑其他方面:首先,加入的ESD保护不能影响端口的功能;其次,不能造成芯片端口的漏电;再次,不能造成芯片的latch-up。以下进行这4种端口的设计,该芯片采用0.35μm 1P3M 5V CMOS工艺设计。

4.1 输入端口的设计

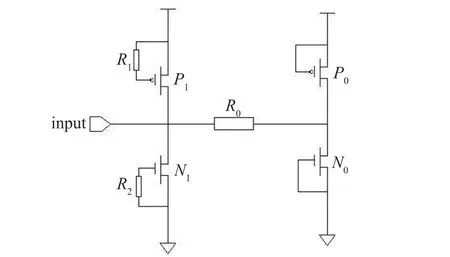

为了使输入的薄栅氧得到最好的保护,所以采用两级保护。第一级采用soft-pull 的MOS管,第二级采用poly电阻加栅接地的NMOS和栅接电源的PMOS。电路图如图5。

第一级选用MOS管,是因为在0.35μm工艺下,二极管、场管的保护效果不理想;另外SCR(可控硅)的效果比较好,面积利用率高,但比较难设计,而且有latchup风险。通常MOS管的ESD保护能力为10V/μm,如果想通过3000V(HBM),设计中心值处在4000V,MOS管的宽度为400μm,单个管子宽度根据ESD规则(30μm~60μm)定为50μm。沟道长度根据规则定为0.6μm。

图5 输入端口保护电路图

针对NMOS存在不均匀导通的情况,即NMOS管的沟道宽度虽然设计值为400μm,但实际上可能只有100μm的NMOS管导通了,采用了soft-pull结构,此结构采用了gate-couple原理,使得NMOS管的触发电压降低,有利于NMOS管均匀导通。而PMOS管不存在这种情况。

第二级保护中的电阻选用poly电阻,主要是因为n-well电阻偏差比较大,而N+扩散电阻击穿电压低,此处设计并不想让电阻击穿。poly电阻的优点是寄生电容小、精度高,但散热的特性比上两种电阻差。所以,设计poly电阻的宽度足够宽,保证散热的面积足够大以及能通过比较大的电流。一般poly电阻的宽度为10μm~20μm,由于是第二级保护,电流较小,宽度选为10μm。

第二级保护的MOS管主要是进一步降低输入电压,泄放ESD电流很小,所以宽度定为50μm,单个管子宽度为25μm。按照10V/μm计算,它能承受的ESD电压为500V,能承受的ESD电流为500/1.5k=333mA。该芯片的输入/输出信号的频率较低,第二级保护的电阻可以选大一些,设计规则最低要求200Ω,此处选了800Ω。假设第一级保护的MOS管二次击穿的电压为20V,那第二级保护的电阻和MOS管上的电流只有20/800=25mA,远远小于第二级保护上MOS管能承受的电流。

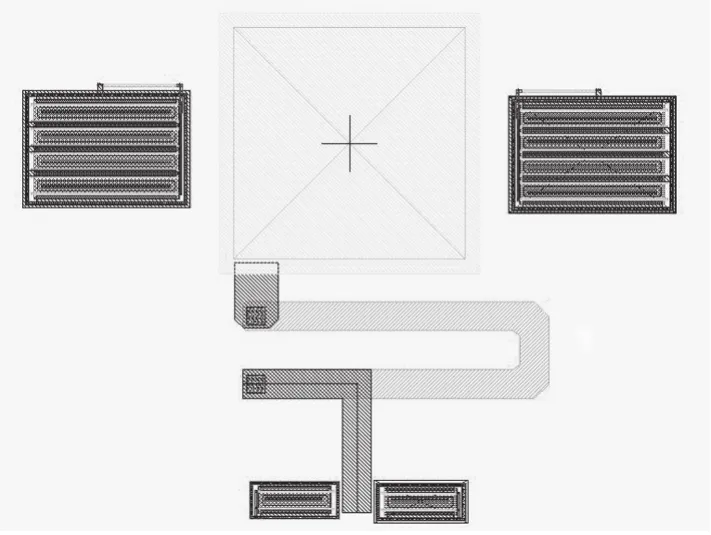

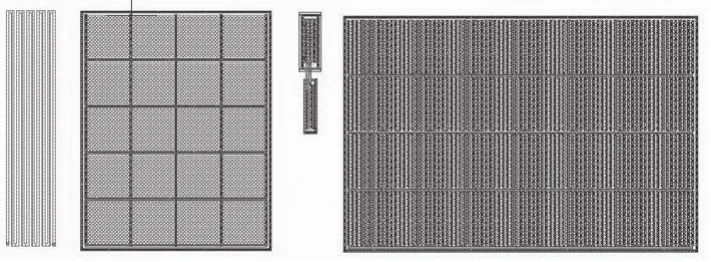

在版图方面,剩下的主要参数是MOS管漏端的孔到栅的距离DCG。在深亚微米下,DCG通常为2μm~3μm,在亚微米,通常为5μm~6μm。在这里依据ESD的设计规则定为2μm。各个器件的版图见图6~图8(图片中的二铝已经隐藏)。

图6 输入端口的ESD保护版图

图7 输入端口的第一级保护NMOS管

图8 输入端口第二级保护的NMOS管

4.2 输出端口的设计

输出端口和输入端口的主要区别在第二级保护上,限流电阻不能太大,否则会影响输出的驱动能力。一般要求尽量小,出于ESD的考虑,电阻值定为100Ω。

图9 输出端口保护的电路图

一般情况下,由于芯片在生产、运输、测试过程中,芯片并未上电,静电进入端口,输出的输入处于悬空,很容易被耦合到一个高电位,在ESD保护器件工作之前先导通放电。若在输出管进入二次击穿之前,第一级保护的MOS管还未工作,那输出管就损坏了。通常MOS管的触发电压在10V左右。于是输出管必须能承受10/100=100mA的ESD电流,也就是输出管的宽度必须大于100mA×1.5k/10V/μm=15μm。另一方面,如果没有限流电阻,要保证ESD保护管有效工作,需要做耦合电路,让ESD保护管先触发。器件的其他参数基本和输入保护电路相同。

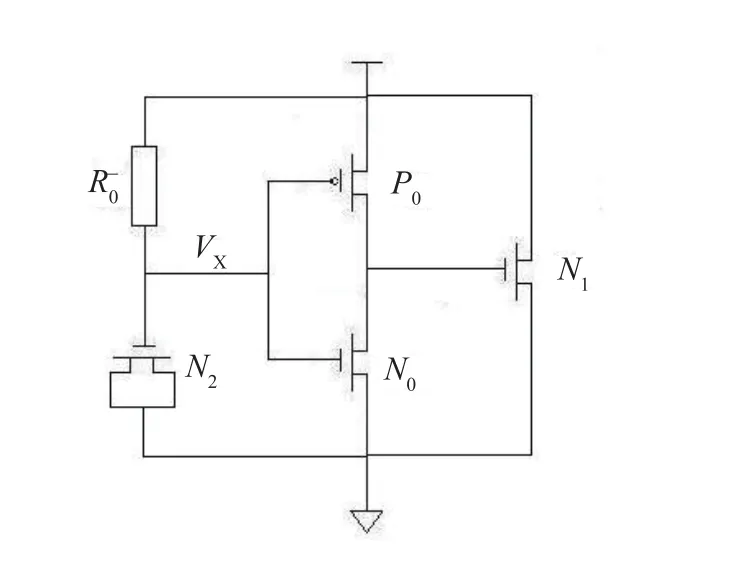

4.3 电源和地之间的保护

电源和地之间的保护电路是由一个电阻电容网络、一个反相器和一个NMOS管组成的;RC网络连接到反相器的输入,它的输出再连接到NMOS的栅极,如图10所示。此电源保护电路在平时是不导通的。人体放电模型(HBM)的放电波形的上升时间约10ns,而芯片在上电时,电源的上升时间约为微秒到毫秒级。为了符合以上两种要求,RC常数设计在次微秒到微秒级之间。当静电出现在电源上时,由于RC网络会产生延迟效应,图10中Vx的电压上升速度会较VDD来得慢,而在两者之间产生电压差。同时电压差也出现在PMOS P0的栅源两端。当此电压差大于其开启电压时,P0导通而将NMOS N1的栅极上拉至VDD,因而NMOS N1就导通而以沟道泄放ESD电流。

图10 电源和地之间的ESD保护

理论上如果N1的尺寸够大的话,光靠导通就可以泄放掉所有的ESD电流而不会使晶体管工作在击穿和snapback区,因此相对于栅极接地技术甚至栅极耦合技术来说,其反应速度要快许多。

此电路参数如图10所示,电阻采用poly电阻,一方面是由于poly电阻精度高,另一方面是因为曾经有公司因采用n-well电阻导致在latchup测试时出现了问题。由于电阻上电流很小,电阻的宽度采用了电阻的最小宽度。电容采用了NMOS管,属于反型的MOS管。

导通ESD电流的NMOS N1宽度很大,因此面积很大。所以芯片面积很小的话通常不采用这样的电源和地的ESD保护方式。该保护电路的版图见图11(图中二铝已经隐藏)。

图11 电源和地之间的ESD保护布局

5 总结

本文从ESD的原理着手,介绍了ESD保护的重要性以及IC设计中常用的一些ESD保护器件、结构、尺寸,并以一款0.35μm 1P3M CMOS工艺中成功验证的芯片ESD保护为例进行具体说明。

当分析ESD保护时,不仅要分析各个端口的保护,更重要的是要把ESD保护当作一个整体来分析。对于每个端口都有4种情况:PS、NS、PD、ND。分析这4种情况时不能只分析某一个端口,一定要把电源和地之间的保护放进来一并考虑。

在设计具体器件时,主要参考foundry提供的ESD设计规则。最好使用I/O单元库,因为单元库是foundry验证过的。如果遇到没有单元库或者所设计芯片端口有特殊要求时,一般不自行设计,而是参考以前的设计经验。

本论文涉及的版图参数主要针对0.35μm的CMOS工艺,并不是通用的尺寸。即使同样是0.35μm的工艺,不同的foundry涉及的参数也不尽相同。

[1] MIL-STD-883C method 3015.7, Military Standard Test Methods and Proc. For Microelectronics[DB].Dept. of Defense, Washington, D. C., U.S.A., 1989.

[2] Ming-Dou Ker and Tain-Shun Wu, ESD Protection for Submicron CMOS IC’s—A Tutorial[DB].CCL Technical Journal,1995,42: 10-24.

[3] T. J. Maloney and N. Khurana. Transmission Line Plising Techniques for Circuit Modeling of ESD Phenomena[DB].EOS/ESD Symposium Proceedings, EOS-7, 1985. 49-54.

[4] T. J. Maloney and N. Khurana. Transmission Line Plising Techniques for Circuit Modeling of ESD Phenomena[DB].EOS/ESD Symposium Proceedings, EOS-7, 1985. 49-54.

[5] C. Duvvury, R. N. Rountree, and O. Adams. Internal chip ESD phenomena beyond the protection circuit[DB].IEEE Trans. on Electron Devices, 1988,35(12): 2133-2139.

[6] H. Terletzki, W. Nikutta, and W. Reczek. Influence of the series resistance of on-chip power supply buses on internal device failure after ESD stress[DB]. IEEE Trans. on Electron Devices, 1993,40(11): 2081-2083.

[7] M. D. Jaffe and P. E. Cottrell. Electrostatic discharge protection in a 4-Mbit DRAM[DB]. EOS/ESD Symp.Proc., EOS-12, 1990.218-223.

[8] C. Cook and S. Daniel. Characterization of new failure mechanisms arising from power-pin ESD stressing[DB].EOS/ESD Symp. Proc., EOS-15, 1993.149-156.

[9] EOS/ESD Standard for ESD Sensitivity Testing[DB]. EOS/ESD Association, NY., 1993.

[10] C.-N. Wu, M.-D. Ker, et al. Unexpected ESD damage on internal circuits of sub-μm CMOS technology[DB].Proc. of International Electron Devices and Materials Symposium,1996.143-146.