应用于ESD防护电路的抗噪声LVTSCR组件研究

2012-07-02马万里

马万里

(深圳方正微电子有限公司,广东 深圳 518116)

1 引言

ESD防护的基本原则就是在尽量短的时间内将尽量多的电荷通过一定的通路泄放掉。由于SCR组件的保持电压低、单位面积的电流泄放能力高,成为目前ESD防护电路中效果最好的组件。

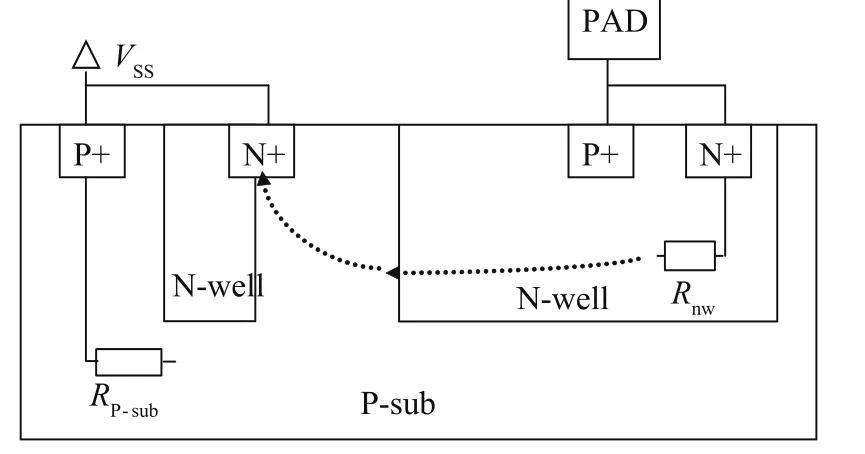

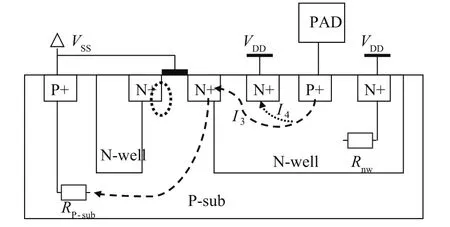

下面以ESD防护中的PS模块(P表示在I/O端口施加正激励,S表示VSS)说明其基本原理。如图1所示,整体为PNPN结构,当PAD端口受到一个高压静电时,N-well与P-sub的结会击穿,产生如图1中虚线所示电流,原本P-sub电位同VSS一致,由于此时P-sub中有电流通过,当Isub×Rp-sub造成的压降值达到一定程度时,会触发由N+、P-sub、N-well组成的寄生NPN晶体管,产生如图2所示的电流,N+为发射极,P-sub为基区,N-well区充当集电区。当Inw×Rnw的值达到一定程度时,会使得N-well与P+形成的PN结正偏,从而触发由P+、N-well、P-sub组成的PNP晶体管。自此,完整的Latch up效应产生了,从PAD到VSS之间形成了一个低阻通道[1],可以释放大量的静电电荷。这就是SCR组件应用于ESD防护的基本原理。

2 低压触发的SCR(LVTSCR)

图1 SCR用于静电防护的基本原理

图2 寄生NPN管的电流流向

从图1中看到,要触发该SCR组件,前提是N-well与P-sub组成的PN结要发生反向击穿,亚微米的CMOS工艺中,这个触发电压一般在30V以上。而芯片内部的N+与P-sub组成的PN结,相比之下,由于N型一侧的掺杂要浓,此结的击穿电压要远低于30V。所以当遇到静电时,还没有等到SCR触发,芯片内部的电路已经烧毁了。更需要说明的是,N-well与P-sub结的击穿电压要高于同工艺条件下MOS器件的栅氧击穿电压,所以必须降低SCR组件的触发电压。

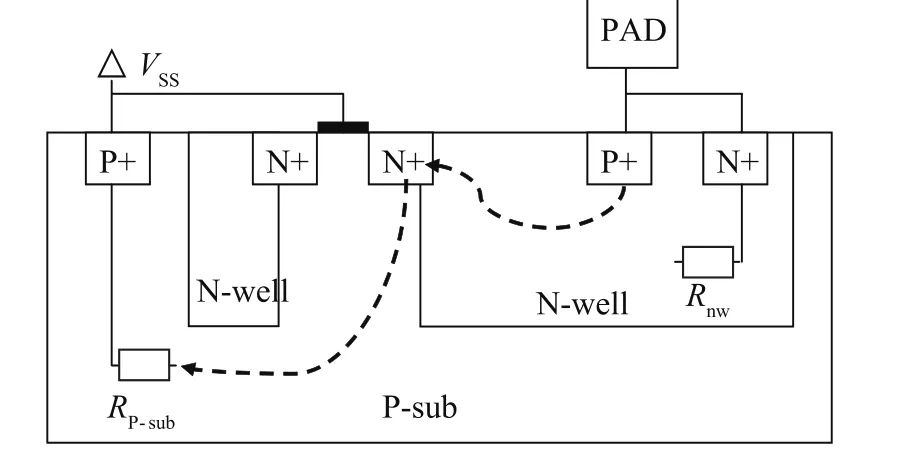

经过改进,在N-well的边缘增加一个N+区域,这样一来,当PAD上受到静电冲击时,这个N+与P-sub组成的结会先于N-well与P-sub的结击穿,大大降低了SCR的触发电压[2~3]。击穿时,产生的触发电流的流向如图3所示。

图3 低压触发SCR的触发过程

同时为了避免此N+与其左侧的N+(如图3所示)产生漏电,需要将两个N+组成的NMOS管的栅极接到VSS。

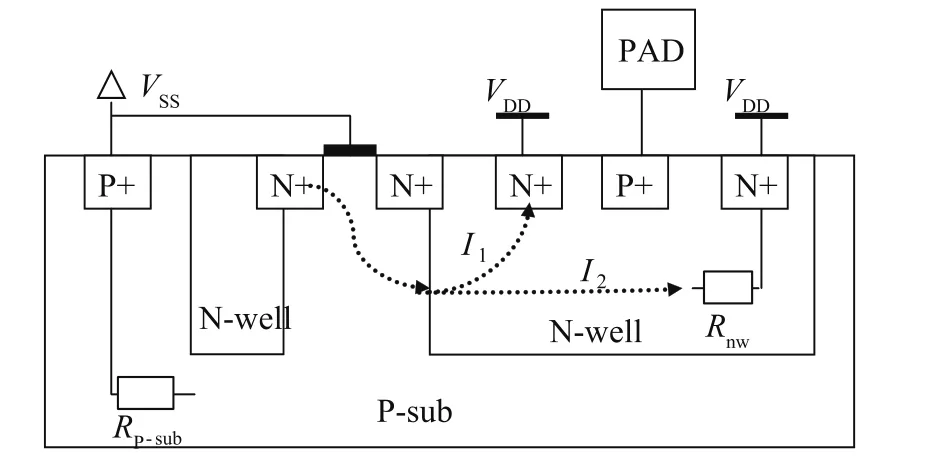

此触发电流通过P-sub到达VSS,当Ip-sub×Rp-sub的值大到一定程度,会触发另一组N-well与P-sub组成的结,使之正偏,也就使得由此N-well、P-sub、N-well组成的NPN管开始工作,产生如图4所示的电流。此电流又通过了N-well中的Rnw,促使了由N-well的P+、N-well、P-sub组成的PNP晶体管开始工作,进而类似Latch up的低阻通路产生,静电可以通过此通路泄放。

图4 低压触发SCR的NPN寄生晶体管电流流向

3 噪声干扰对LVTSCR组件的影响

集成电路在工作时,随时可能受到噪声的干扰,如图5所示,为一反相器接一用于防静电的SCR组件,当反相器输出高电平到PAD端口时,如果在这个时候,有噪音耦合到此电路上,极可能触发SCR,触发后的SCR由于保持电压(holding voltage)很低,只有1V~2V,这会将反相器的输出端电平拉低。

此时PAD端口得到的就不再是本来需要的高电平,而是由于SCR导通产生的低电平,这会造成电路的严重误动作。并且由于VDD到VSS之间形成了一个低阻通道,还会造成严重的能量损耗,所以有必要考虑如何解决噪声干扰问题。

图5 噪声干扰造成的SCR误工作

4 提高LVTSCR的触发电流

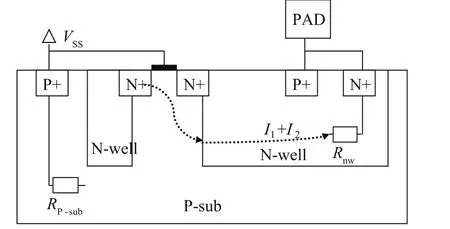

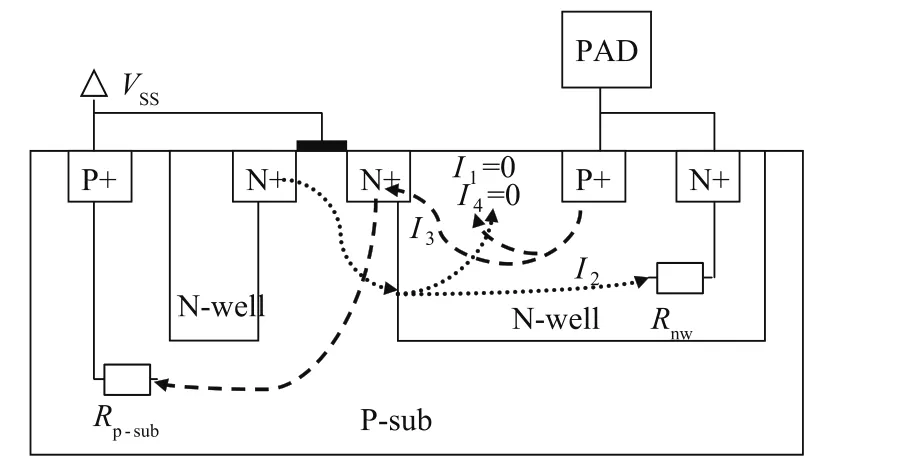

通过在N-well中增加一个N+区域,当PAD遭受到噪声干扰时,虽然仍是N+/P-sub结被击穿,但此时从P+流入的电流会有一部分经过新增加的N+流到VDD[4],如图6所示的I4。直接流入P-sub的电流就少了一些。由于Ip-sub的大小决定了NPN管是否被触发,Ip-sub小了,NPN管就不容易被触发,如果要被触发,就需要更强的噪声。

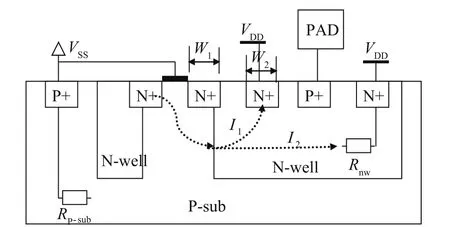

图6 高触发电流的LVTSCR组件剖面

当噪声强到足够触发NPN寄生管时,NPN管的电流(电子流)方向如图7所示。此时进入N-well的电流有一部分被N+区分流了,如图7中的I1。经过Rnw的电流小了,由Inw造成的电压差也随之变小,由N-well中的P+、N-well、P-sub组成的PNP管,因发射结正偏而触发的难度就加大了。如果要被触发,就需要更强的噪声。

图7 高触发电流LVTSCR的寄生NPN管电流方向

对于没有增加N+区域的常规低压触发SCR(LVTSCR),当PAD遭受噪声,N-well/P-sub结击穿时,从P+流出的电流没有被N+分流(I4=0),如图8所示,全部进入P-sub,Ip-sub的电流就相对大些,经过P-sub造成的电压差就大些,NPN管被触发也容易些。万一NPN被触发后,其进入N-well中的电流也全部通过Rnw,没有I1分流(I1=0),如图8。其由Inw引起的压降要大一些,触发PNP管就更容易一些。所以,不加N+区的SCR组件不能有效地抗噪声干扰。

对于有N+区域的SCR结构,称为高电流触发的SCR(HITSCR)。对于采取HITSCR方式的ESD结构,且使用0.5μm SPDM工艺实现的芯片,测量其I-V特性,发现具有很奇特的曲线,具有二次触发特性,如图9所示。

第一触发点m:V=12.1V,I= 2.0mA

第二触发点n:V=9.3V,I=205.5mA

第一保持区A:V =7.9V,I=27.0mA

第二保持区B:V =1.2V,I=12.0mA

图8 无N+区域的LVTSCR组件中的寄生NPN与PNP电流

图9 HITSCR的I-V特性曲线

第一个触发点m,是由于N+与P-sub之间的结击穿所致,击穿造成了低阻通路,电流急剧上升。但是由于N-well中的N+(用于分流的作用)区域存在,此时的电流还不能完全使得SCR组件中的PNP/NPN寄生管的发射结正偏,也就是说还不能触发SCR组件进入闩锁状态。如果只是噪声干扰,已经发生击穿的N+、P-sub通路不能够继续维持下去。这就抑制了噪声干扰。当存在较强静电时,电流会继续增大,进而会完全触发SCR组件中的NPN、PNP寄生管导通,就进入第二触发点n。这会形成完整的闩锁效应,此通路的电流更大、电阻更小,就进入了第二保持区B。

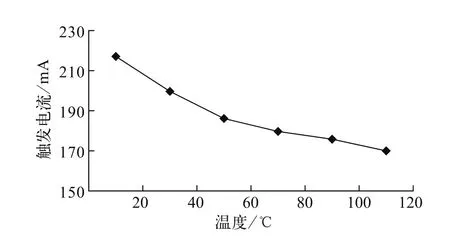

抗噪声干扰的高电流触发SCR组件(HITSCR)对温度也有一定的敏感性,由于NPN、PNP管的放大系数会随着温度升高而变大,而放大系数越大,便可以在更小的触发电流情况下触发SCR组件。所以HITSCR的触发电流随着温度的上升而降低,如图10所示。不过即使在120℃,触发电流仍旧可以达到170mA。这对噪声干扰还是具有很强的免疫能力。

对于同样采用0.5μm SPDM工艺流程、设计面积相同但设计结构不同的ESD防护,通过测量不同结构SCR组件的触发电流、触发电压、抗噪声能力,可以看到HITSCR确实有很强的抗噪声干扰能力,如表1所示。

图10 HITSCR的触发电流与温度关系曲线

表1 不同结构的SCR组件触发以及抗噪声能力对比

5 提高LVTSCR的保持电压

通过提高SCR的保持电压(holding voltage),使之比电路中的VDD电位要高,此时SCR的触发电压不变,但是由于高保持电压,即使噪声干扰触发了SCR,噪声干扰消失后,由于VDD电位不能够提供足够高的保持电压,也不会形成持久的闩锁效应,SCR就会自动关闭。有3种设计方法可以实现此要求。

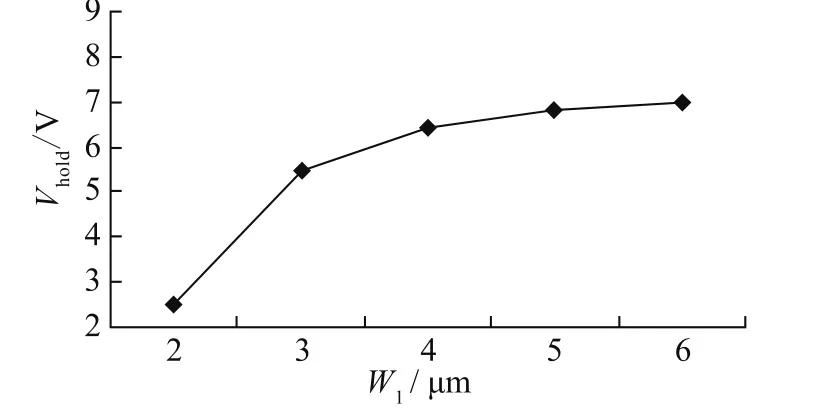

优化SCR结构,使得不容易发生闩锁效应。比如加宽HITSCR组件中的N+区域宽度W1/W2,如图11所示,随着N+宽度W1的增大,对于NPN管来说,P-sub基区的横向宽度也变大了。随着N+宽度W2的增大,对于PNP管来说,N-well基区的横向宽度也变大了。它们的放大系数β变小。SCR组件中NPN、PNP管发生Latch up效应的难度变大,通路中电阻增大,维持电压也增大。但这又会影响遇到静电时的放电效果,所以是一组矛盾关系。在实际的设计中,这点是控制难点,也是关键点。N+宽度既不能过大,也不能过小。如果过大,SCR组件会很难被触发,就不能起到防静电作用。如果过小,虽然防静电效果好,但是又很容易受到电路中的噪声干扰。图12中给出了W1与保持电压Vhold的关系。

此外,可以通过HITSCR组件的串联使用,或将HITSCR与二极管串联[4],也可以使Vhold的总值增大。

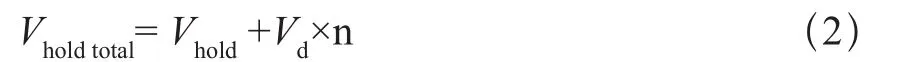

多个HITSCR串联使用时,Vhold关系如下:

Vholdn为各个HITSCR的单个保持电压。

HITSCR与二极管串联使用时,Vhold关系如下:

Vd为单个二极管的正向导通压降。

图11 增大HITSCR的N+宽度提高保持电压

图12 HITSCR的N+区宽度与Vhold的关系

6 结论

通过在well的边缘,设置与well同样类型的重掺杂区域,可以有效降低SCR的触发电压。但这种结构在电路的应用中也极易受到噪声干扰。

优化LVTSCR的结构,通过提高LVTSCR的触发电流,可以在保持低触发电压的前提下,提高对噪声干扰的免疫能力。通过提高LVTSCR的保持电压,可以使得LVTSCR在被噪声触发的情况下,不使之继续维持下去,同样提高了抗噪声干扰的能力。

[1] 董丽凤,李艳丽. CMOS集成电路闩锁效应抑制技术[J].电子与封装,2010,10(9):28-30.

[2] 汤培望. SCR的I-V曲线中二次崩溃对ESD性能的影响[J].现代电子技术,2010,34(18):1-3.

[3] 李冰,杨袁渊. 基于SCR的ESD器件低触发电压设计[J].固体电子学研究与进展,2009,29(4):561-565.

[4] 李冰,王刚. 基于SCR的ESD保护电路防闩锁设计[J].微电子学,2009,39(4):786-789.