DTMB标准的高速多码率LDPC编码器设计

2012-06-22蒋蓝祥刘昌银

蒋蓝祥,刘昌银

(中国传媒大学信息工程学院,北京 100024)

DTMB标准的高速多码率LDPC编码器设计

蒋蓝祥,刘昌银

(中国传媒大学信息工程学院,北京 100024)

针对中国数字电视广播地面传输标准(DTMB)中给出的多码率LDPC码生成矩阵的特点,设计了一种串行输入串行输出基于流水线SRAA(Shift Register Adder Accumulator)结构的编码器,并同时适用于3种不同码率的LDPC码。在Altera公司的EP3SL150型号FPGA平台上,整个设计最高时钟可达341.88MHz,简化了存储器设计结构,完全适合于DTMB标准调制器的开发。

准循环LDPC码;中国数字电视广播地面传输标准;SRAA结构;FPGA

1 引言

早在1962年,R.G.Gallager第一次提出了LDPC码的概念[1]。但是由于其需要庞大而复杂的计算一直不被人们所关心。随着近几年器件水平的发展,LDPC码的优势才再一次被发现。2006年8月,中国数字电视广播地面传输标准DTMB正式公布,该标准前向纠错码由外码(BCH码)和内码(LDPC码)级联实现,包含0.4,0.6,0.8共3种码率[2]。标准中使用的LDPC码为非规则准循环LDPC码,该码性能可接近随即构造的LDPC码,而实现的复杂度又可接近循环LDPC码。

如今准循环LDPC码的实现,主流方法是采用基于SRAA(Shift Register Adder Accumulator)结构设计。对于DTMB标准的LDPC编码器的设计,文献[3-5]也提出了多种改进方法。如采用多级并行SRAA结构的实时编码器、部分并行SRAA结构的编码器等,但其都存在着时钟速度不高,ROM存储器结构复杂资源消耗大的不足,这对整个DTMB调制器的设计带来了瓶颈。

本文针对DTMB标准中LDPC码的特点,基于一种串行流水线的SRAA结构[6],设计了满足三种不同码率的高速LDPC编码器,并在Altera公司的EP3SL150型号FPGA上得到实现,最高时钟可达341.88MHz。整个设计在241.96MHz频率下进行仿真验证,完全满足DTMB调制器设计的要求。

2 DTMB标准的QC-LDPC码分析

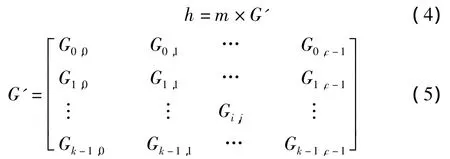

DTMB标准规定,LDPC码的生成矩阵Gqc结构如下:

其中,I是b×b阶单位矩阵,O是b×b阶零矩阵,Gi,j是 b × b 阶循环矩阵且 0≤i≤k-1,0≤j≤c-1,由其首行(即循环子矩阵的生成多项式)决定。三种不同码率的各参数如表1[7]:

表1DTMB标准LDPC三种码率参数

由(1)式可知,标准中的LDPC码为典型的QCLDPC码,且三种不同码率生成矩阵具有相同的结构,其中循环子矩阵Gi,j也都为127阶。

设m为输入信息比特,c为得到的码字,h为得到的校验位,则有:

由(2)(3)式可知,只需求的校验位h即可得到输出码字c。如下式:

标准规定,舍弃最前面的5个校验位则为最后的输出码字,即每组LDPC编码后输出为7488比特码字。为得校验位,只需将循环子矩阵Gi,j的生成多项式存于ROM表中即可,这样既能完全得到生成码字,又可以大大节省存储资源。

表2 DTMB信号帧中含LDPC编码对应参数

DTMB标准规定,每个信号帧由帧头和帧体两部分组成,帧体部分包含36个符号的系统信息和3744个符号的数据信息。而3744个符号的数据信息就是由LDPC编码后的输出码字经星座映射后得到。则可得每个信号帧所需LDPC编码如表2。可知,对于高效的DTMB调制器,要求一帧数据处理中最多可包含3组LDPC码的编码输出,这就需要编码器满足高速率要求。

3 DTMB标准的多码率LDPC编码器

如前文所述,DTMB标准中的LDPC码为QCLDPC码,且三种码率下的循环子矩阵均为127阶。基于生成矩阵来对编码器进行设计,利用其子块循环的特性,由SRAA结构可在低复杂度下完成LDPC编码。

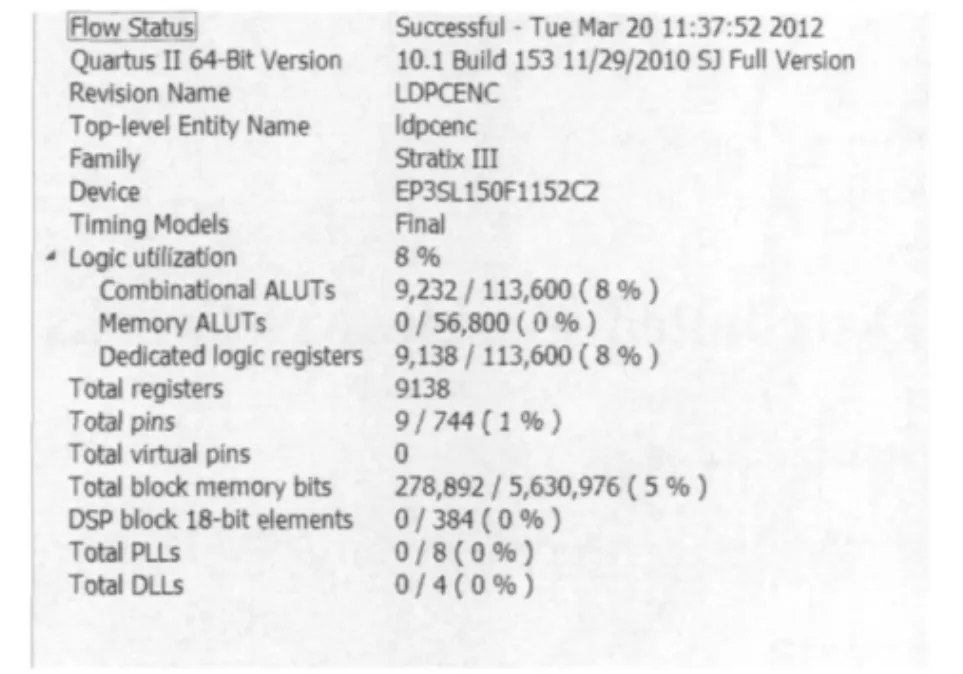

3.1 SRAA结构的编码原理

循环子矩阵的乘法运算可由SRAA结构(即循环移位寄存器累加和结构)来完成。其结构框图如图1:

图1 SRAA结构图

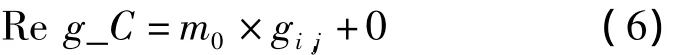

可知,SRAA结构由两个同样深度为127、宽度为1bit的循环移位寄存器Reg_G和移位寄存器Reg_C 组成。以 Gi,j为例,gi,j为其生成多项式,m 为输入信息数据。在GF(2)域中,乘法与相与等效,而加法与异或等效。当第一个信息位m0输入时,将gi,j从ROM中读出并写入Reg_G,与m0相与后再和Reg_C中数据异或后写入Reg_C。这一过程可等效于下式:

当下一个信息位m1输入时,Reg_G循环右移一位得到,再与m1相与后和Reg_C异或后写入Reg_C。此时有:

同理,当第127个信息位m126运算完毕后,有:

这样即完成了信息位与循环子矩阵的相乘运算。

如果随后再输入127比特信息位,Reg_G读入Gi+1,j的生成多项式gi+1,j,再进行同上运算,则有:

当m为k×b的输入信息位,则得到的Reg_C有:

可知,我们只需进行c次上式的运算,即完成了LDPC码校验位的计算。

3.2 LDPC编码器设计

考虑到DTMB调制器中LDPC码前后模块的设计,本文提出一种串行输入串行输出的基于串行流水SRAA结构的LDPC编码器。

由表1中参数可知,编码器在0.4码率下需35个SRAA结构,在0.6码率下需23个,0.8码率下需11个,所以要满足三种码率则需要使用35个SRAA结构。SRAA结构之间按串行流水线形式连接,结构框图如图2。

以0.4码率为例:信息位串行输入,第1个信息位有效周期,数据存于d0寄存器中,SRAA0从数据总线中读取 G0,0的生成多项式 g0,0,并与 d0中的数据进行运算;第2个信息位有效周期,d0中数据移位至d1,新输入数据存入d0中,SRAA1从数据总线中读取 G0,1的生成多项式 g0,1,并与 d1 中的数据运算,而SRAA0中的g0,0进行循环右移,并与d0中数据进行运算;同上述过程,当第3048个信息数据存于d34中并在SRAA34计算完毕就完成了一组LDPC编码,在35个SRAA结构的Reg_C中储存的便是校验位,随后依次将校验位左移输出。

0.6码率与0.8码率模式时,通过控制器控制,当输入数据移位至d22或d10时,便不再后移。同样的,后级的SRAA模块也不再参与运算,满足三种不同码率的编码运算。

采用Verilog HDL的RTL级代码设计整个模块,以下介绍各个模块的设计:

(1)matrix_cell模块

matrix_cell模块主要完成循环子矩阵的运算,即SRAA结构模块。结构如图1,其中含1bit移位输入,1bit移位输出用于校验位的串行移位输出。如图2中的 matrix_cell模块阵列连接方式为,SRAA0的移位输出接到整个编码器的输出,SRAA1的移位输出与SRAA0的移位输入相连接,相同的每个后级的SRAA结构的移位输出与前级的移位输入相连。

图2 LDPC编码器结构框图

(2)matrix_g_rom模块

此模块为存储各个循环子矩阵生成多项式的ROM模块。由表1中参数可知,0.4码率下生成矩阵共含24*35=840个循环子矩阵,0.6码率下含36*23=828个,0.8码率下含48*11=528个,三种码率共含2196个。本设计采用统一的ROM设计结构,即三种码率的生成多项式都存于同一块ROM中。ROM深度为2196,宽度为127,地址0~839中储存0.4码率的生成多项式,地址840~1667中储存0.6码率生成多项式,而地址1668~2195中储存0.8码率生成多项式。这样的设计大大简化了ROM表设计结构,matrix_cell模块阵列可使用同一数据总线,只需控制各matrix_cell模块读取生成多项式的使能即可,也最大程度地节约了存储器空间。

(3)ldpcenc模块

ldpcenc模块为整个编码器的顶层设计模块。模块框图如图3。

d:串行数据输入端;

dvalid:数据有效输入端;

clock:时钟输入端;

clrn:清零输入端;

fec_level:码率选择输入端;

load:码率选择加载输入端;

q:串行数据输出端;

qvalid:串行数据有效输出端。

在此模块中例化了matrix_cell模块阵列和matrix_g_rom模块。使用状态机控制各模块的使能及控制信号,为ROM提供读取地址及各matrix_cell模块生成多项式数据的读取使能。并完成三种码率之间的切换。

图3 ldpcenc模块框图

3.3 编码器性能分析

本设计完成了DTMB标准下LDPC码三种码率的高速编码。三种码率的码长都为7493,标准规定校验位在前,信息位在后,并舍去最前面5位校验位,实际输出码长为7488。为验证方便,本设计仍将前5位的校验位输出,每一组LDPC编码的时间为实际码长7493加上流水线长度c,即0.4码率需7493+35=7528个周期,0.6码率需7493+23=7516个周期,0.8码率需7493+11=7504个周期。

DTMB标准中规定系统基带符号率为7.56Msps,高性能调制器采用4倍升采样设计后的符号率为30.24Msps。标准中给出了64QAM、32QAM、16QAM、4QAM、4QAM-NR五种映射方式,可知系统中可能的最大比特率为7.56M*6=45.36Mbps。考虑到整个DTMB系统中复杂的交织与OFDM信号成帧,系统时钟选用7.56M*16=120.96MHz或者7.56M*32=241.92MHz。为提高系统的高速高效性,采用单时钟同步电路设计,本设计采用241.92MHz时钟作为编码器的工作时钟进行时序约束,结果完全满足系统的要求。

4 FPGA实现及仿真验证

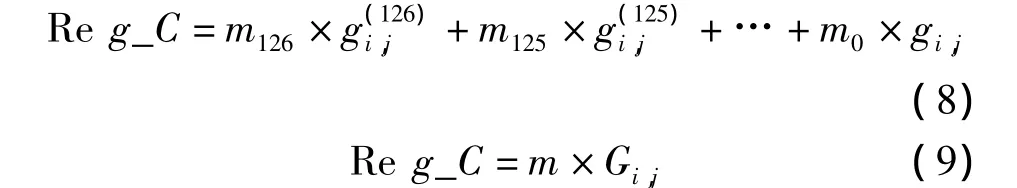

本设计选用 Altera公司 StratixIII系列EP3SL150款FPGA,在QuartusII 10.0环境下进行设计、综合及布局布线,全编译报告如图4:

图4 FPGA全编译报告

可知,编码器仅占用了278892bits的内部存储器资源用作ROM,最大程度的节约了存储器资源。编码器可支持的最大时钟为341.88MHz,如图5:

图5 最高时钟报告

编码器的高速设计远超过于同类设计,并且更加节约存储器资源,但这是以牺牲更多的ALUTs控制寄存器为代价的。

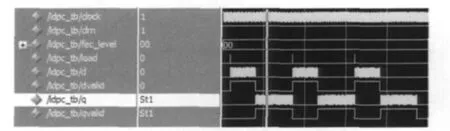

在QuestaSim6.5环境下对编码器进行门级仿真,如图6:

图6 编码器门级仿真图

仿真结果满足实际时序要求,将门级仿真结果数据读入matlab中与直接矩阵运算所得码字进行比对,结果完全一致,编码器设计功能正确。

5 结论

针对DTMB标准中LDPC码的准循环特性,本文直接根据生成矩阵设计满足三种码率的高速编码器。整个设计基于串行SRAA结构,通过流水线形式完成了串行输入串行输出的LDPC编码。在StratixIII系列 FPGA上进行实现,共占用 8%的ALUT,5%的存储器资源,并最高可支持341.88MHz时钟。完全适合于高速的DTMB调制器中的应用。

[1]Gallager R G.Low-density Parity-check Codes[J].IRE Trans Inf Theory,1962,8(1):21-28.

[2]GB20600-2006.数字电视地面广播传输系统帧结构、信道编码和调制[Z].2006.

[3]杨抒文,彭克武,潘长勇.DTMB发射机LDPC编码器的设计与优化[J].电视技术,2008,32(7):4-5.

[4]彭海云,徐建敏,王鹏,刘玮.DTMB标准实时LDPC编码器设计[J].电视技术,2010,34(1):33-36.

[5]XiangOuyang,ChangchengRuan,Lingxiang Zheng.Implementation of LDPC encoding to DTMB standard based on FPGA[J].IEEE Computer and Information Science,2011:235-238.

[6]Zongwang Li,Lei Chen,Lingqi Zeng.Efficient Encoding Of QuasiCyclic Low-Density Parity-Check Codes[J].IEEE Transactions on Communications,2006,53(11):71-81.

[7]杨知行.地面数字电视传输技术与系统[M].北京:人民邮电出版社,2009.

Design of High-speed Multi-rate LDPC Encoder to DTMB Standard

JIANG Lan-xiang,LIU Chang-yin

(Information Engineering School,Communication University of China,Beijing 100024,China)

According to multi-rate LDPC generation matrix distribution property of DTMB standard,a high-speed LDPC encoder based on pipelined Shift Register Adder Accumulator architecture is implemented in this paper,which is serial input and serial output.This design can complete three different rate encodings.The maximum clock frequency of the whole design which is implemented on FPGA chip EP3SL150 of Altera can be 341.88MHz.The architecture use simpler memory structure and is suitable for DTMB modulator.

QC-LDPC;DTMB;SRAA circuit;FPGA

TN949.197

A

1673-4793(2012)02-0029-05

2012-3-29

蒋蓝祥(1988-),男(畲族),江西赣州人,中国传媒大学硕士.E-mail:jlx_cuc@cuc.edu.cn

(责任编辑

:王 谦)