基于FPGA的BLVDS总线设计

2012-06-13张洪亮

张洪亮

(中国西南电子技术研究所,成都 610036)

基于FPGA的BLVDS总线设计

张洪亮

(中国西南电子技术研究所,成都 610036)

针对现有的航空总线系统结构复杂、传输速率低、电磁兼容性差等问题,提出了一种基于FPGA的总线型低压差分信号(BLVDS)总线解决方案。介绍了BLVDS的总线结构,对BLVDS的通信方式和基于FPGA使用硬件描述语言实现BLVDS总线通信的方法进行了深入研究。同时,分析了信号传输质量,在工程中验证了其高速率和高可靠的总线传输特性,为新一代航空高速总线系统提供了参考。

航空总线;数据传输;总线型低压差分信号;硬件描述语言

机载数据总线技术是现代先进飞机电传操作系统和航空综合化最重要的关键技术之一。航空电子系统的发展对机载数据总线不断提出新的要求[1]。采用新一代的高速率、低功耗、电磁兼容性的总线技术成为新的发展方向。

总线型低压差分信号(BLVDS)是一种新型总线接口电路,适合于多点电缆或背板应用。BLVDS可以为系统提供理论最高800Mbit/s的传输速率,并具有功耗低、电磁兼容性好等特点。受1553B总线的传输方式启发,笔者基于FPGA,采用硬件描述语言(HDL)实现了250Mbit/s的BLVDS的FPGA逻辑设计。

1 总线结构及工作过程

1.1 总线系统结构

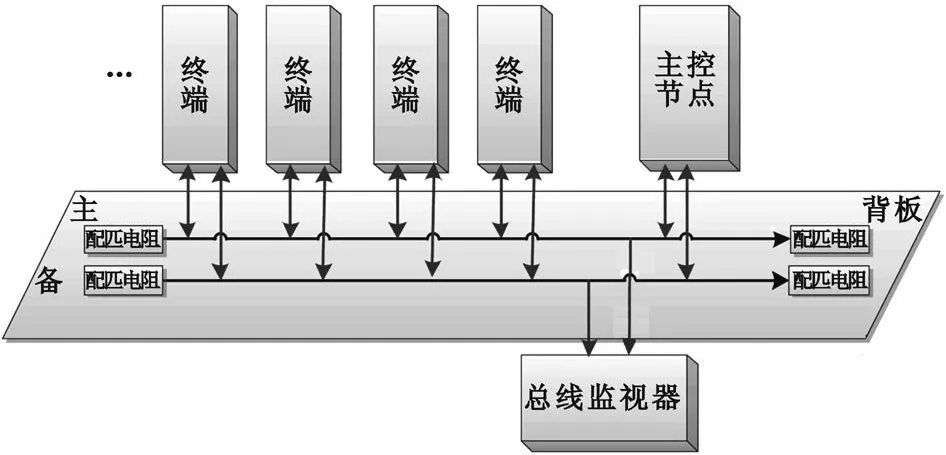

BLVDS总线通信系统由背板和通信子板组成。背板有8个插槽,可以插入8个子卡,并布有BLVDS总线、备份总线和匹配电阻。通信子板包含3种类型:主控节点、总线监视器、通信终端。其中,主控节点向通信终端发送指令字、数据字;总线监视器接收总线上传输的所有数据作为分析使用;通信终端接收主控节点发送过来的指令和数据,并可以回复相应的状态和数据。

通信系统结构如图1示。

图1 BLVDS总线结构Fig.1 The system diagram of BLVDS

1.2 工作过程

BLVDS为一主多从的多点总线。总线的主节点称为主控节点,从节点称为终端节点。

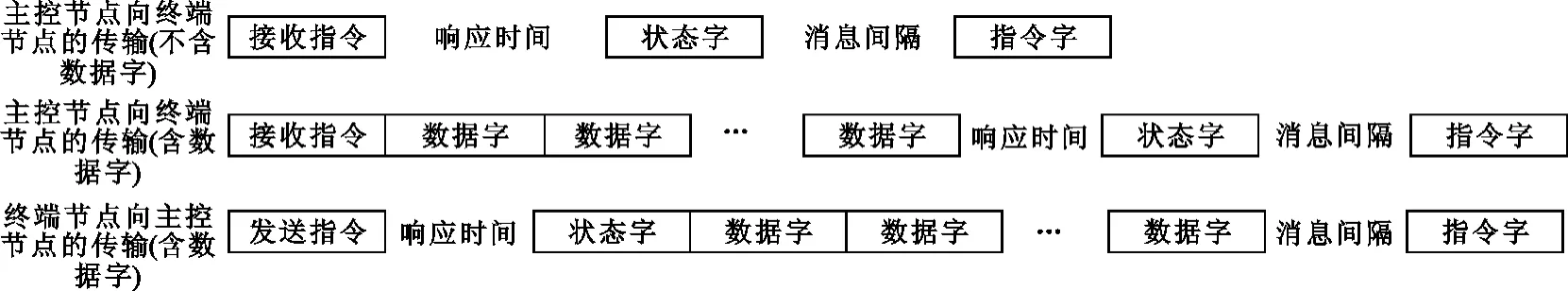

总线上所有节点都有一个唯一的总线地址,用于各个节点的识别。当主控节点需要向某一终端节点发送数据时,主控节点应先向终端节点发送接收指令,终端节点在接收到数据1 ms内向主控节点回复状态字,并将接收到的信息上报应用层。

当终端节点需要发送数据给主控节点时,终端节点的应用层将要发送的数据写入缓存等待发送,主控节点每10 ms都会向总线上各个终端节点发起查询指令,当查询到要发送数据的终端节点时,终端节点向主控节点在1 ms内回复状态信息和需要发送的数据。系统通信流程[2]如图2示。

图2 系统通信方式Fig.2 The communication of system

BLVDS总线上每一次消息的发送或查询只能由主控节点发起,任何终端节点都无权主动向总线上发送数据。当主控节点向某个终端节点发送询问消息后,终端节点应在1 ms之内作出响应,向总线发送状态信息。主控节点若在1 ms内没有在总线上探测到该终端节点发出应答消息,则认为该终端节点响应超时。主控节点判定终端节点响应超时后,则重复向该终端节点发送询问消息,若重复3次发送仍未收到该终端节点的应答消息,则认为该节点为故障节点,并向应用层报告。

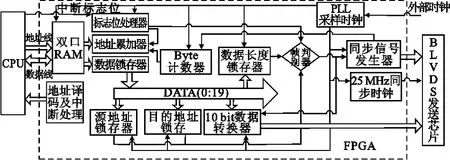

2 设计实现

该设计使用了硬件设计语言在FPGA内部实现,包含终端节点、主控节点和总线监视器各项功能,CPU可以根据需要对FPGA内部的寄存器(双口内部特定地址)进行配置从而获得不同的功能。在CPU需要发送总线数据时,只需要将准备好的数据写入相应地址的双口RAM内部,然后再向FPGA发送一个发送标志位,FPGA将自行将所有数据向BLVDS总线发送数据;在CPU需要接收数据时,FPGA先将接收好的数据进行解析,然后存入相应的双口RAM内,并向CPU发出中断,通知其来读取数据[3]。

2.1 BLVDS帧定义

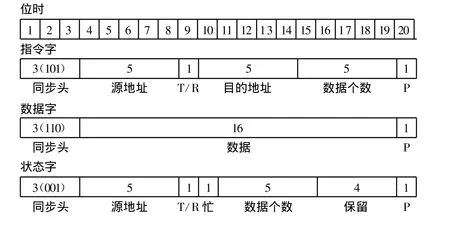

BLVDS总线通信系统的发送/接收方式已经在1.2节中介绍,这里不再重复。图3为指令字(包含查询指令)、数据字、状态字的格式定义。图中,同步头表示该帧数据的类型;数据个数表示该帧数据所包含的数据字个数;源地址表示发送该消息的节点地址;目的地址表示接收该消息的节点地址;P为奇偶校验位。

图3 消息格式定义Fig.3 The frame of message

2.2 FPGA逻辑设计

2.2.1 接收FPGA逻辑设计

外部时钟进入FPGA后,首先使用DCM进行锁相、倍频后生采样时钟。整个逻辑将使用这个采样时钟进行逻辑处理。当外部BLVDS信号(Sy-lock、Sy-data、Sy-rclk)进入FPGA后,首先帧同步器使用采样时钟对这些信号进行采样处理。采样处理完成后,同步信号判决器对同步信号Sy-lock进行判别,若该信号有效,则证明数据处于有效状态,可以对数据进行采样。数据锁存器是将两个10 bit数据进行合并和锁存,然后供源地址锁存器、目的地址锁存器、数据长度锁存器以及双口RAM等所有内部逻辑使用。源地址锁存器和目的地址锁存器的作用是将接收到的源地址和目的地址进行锁存,并与CPU写入寄存器的地址进行比对。在接收数据的同时,Byte计数器也对接收到的字节计数,奇偶校验器也进行同步校验,接收到的数据也被同步写入双口RAM中。当Byte计数器的计数值与数据长度锁存器长度相等时,进入帧判别器,帧判别成功的标志为目的地址与当前模块地址相同、校验正确并符合本协议通信过程后,方可发送判别成功标志。中断处理器检测到判别成功后,向CPU发送接收中断,此时CPU可以从双口RAM中读取数据。图4为接收逻辑框图。

图4 接收逻辑框图Fig.4 The diagram for receiving logic

2.2.2 发送FPGA逻辑设计

当FPGA接收到来自CPU的发送标志位后,标志位处理器开始对标志位同步处理,并将处理好的标志位送至帧判别器。与此同时,地址累加器开始累加,FPGA开始自动读取双口RAM内的数据。数据锁存器将数据锁存,并将需要解析部分的数据送至源地址锁存器、目的地址锁存器和数据长度锁存器。源地址锁存器和目的地址锁存器作用是将锁存到的地址与CPU写入寄存器的地址进行比对,并将比对的结果送入帧判别器。10 bit数据转换器作用是将锁存的数据进行10 bit转换,并将转换的数据送至BLVDS发送芯片。帧判别器的作用是在接收到标志位、并在目的地址和源地址符合要发送的要求时,启动同步信号发生器。同步信号发生器将产生同步信号,并使用25 MHz时钟将同步信号与10 bit数据进行同步。图5为发送逻辑时序图。

图5 发送逻辑时序图Fig.5 The diagram for transmission logic

3 设计验证与测试

为了验证设计的正确性和性能指标,搭建了如图1所示总线测试平台[4],使用Ti公司型号为TMS320F2812的DSP作为CPU进行功能验证、传输测试、工程验证。

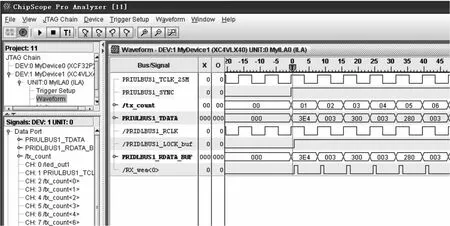

3.1 功能验证

使用DSP作为主控节点和终端节点的CPU进行功能验证。验证流程为:DSP完成设置寄存器后,在主控节点DSP将需要发送的数据写入FPGA,并给FPGA一个发送标志位,FPGA发送逻辑自动发送数据。在经过背板传输后,终端节点的FPGA接收数据,并将接收到的数据发送至通信终端的DSP,DSP将接收到的数据进行打印。在此过程,使用Chipscope软件采集到了主控节点发送逻辑和接收逻辑的时序图,如图6所示。图中tx-count为发送数据字节计数器,PRIULBUS1-SYNC为发送同步信号,PRIULBUS1-TDATA为发送的数据,PRIDLBUS1-LOCK-buf为接收同步信号,PRIDLBUS1-RDATABUF为接收数据。验证结论:发送的数据可以通过总线传输后正确接收。

图6 主控节点发送接收数据时序图Fig.6 The diagram of transmitting and receiving data from master node

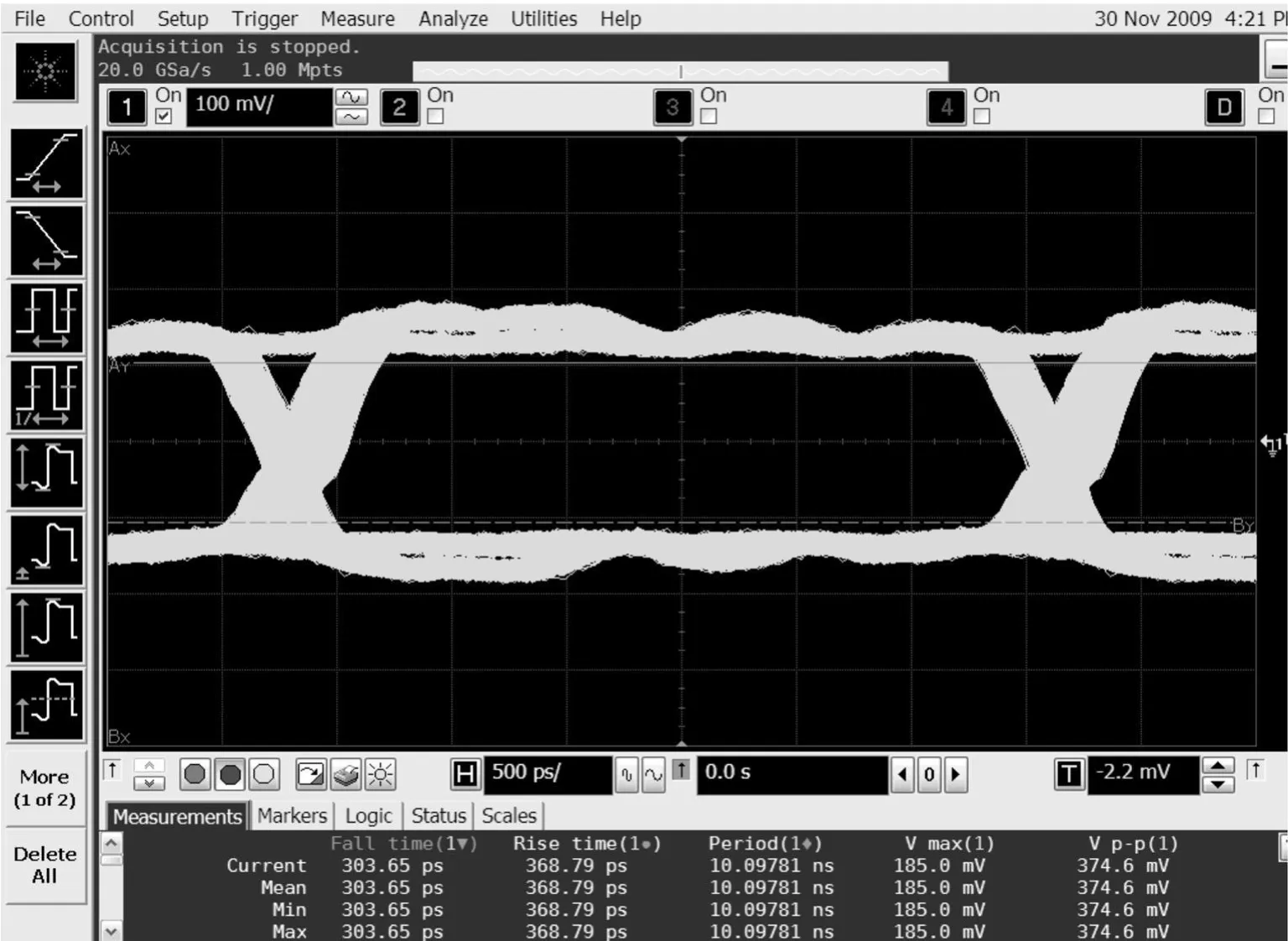

3.2 传输测试

为了衡量传输系统的性能优劣,在实验室中,通常用眼图分析法来分析信号的传输质量。对总线上串化后的数据进行眼图测量,图7为测试时的眼图。从图7中可以看出每个码元将重叠在一起,波形无失真,最终在示波器上看到的是迹线又细又清晰的“眼睛”,“眼”开启得较大,表明信号传输质量较好。验证结论:信号传输质量较好,信号传输可靠。

图7 数据和时钟经过串化后的眼图Fig.7 The eye diagram for serialized data and clock

3.3 工程验证

根据设计需求,使用测试系统进行了工程验证,在速率为250 Mbit/s时,CPU每1 ms周期内需完成20 byte数据的收发和两节点无时间间隙连续收发,分别对主控节点进行自发自收测试,主控节点与通信终端互相收发测试,经过50 000帧数据收发测试,均无误码、丢包现象。由此可得出结论:设计可靠,满足现阶段需求。

4 结速语

数据总线是航空电子系统的神经枢纽。本文设计完成了一种基于FPGA的高速率、低功耗的BLVDS总线通信方式,在严格的时序内完成了模块内部和模块级间的数据传输,并通过功能验证、传输测试和工程验证的方法使设计得到验证,达到了预期的目标和性能,检验了设计的正确性和可行性,为航空领域新一代总线发展提供了重要参考。

[1]支超有.机载数据总线技术及其应用[M].北京:国防工业出版社,2009.

ZHI Chao-you.Avionics Data Bus Technology and Its Application[M].Beijing:National Defense Industry Press,2009.(in Chinese)

[2]聂俊伟,向超,彭启琮.基于NIOS2的MIL-STD-1553B总线协议的分析[J].通信技术,2007(12):18-20.

NIE Jun-wei,XIANG Chao,PENG Qi-cong.Analysis of MIL-STD-1553B Protocol Based onNIOS2[J].Communications Technology,2007(12):18-20.(in Chinese)

[3]黄润龙.基于FPGA的高速同步串行总线设计[J].电讯技术,2008,48(11):92-96.

HUANG Run-long.Design of High SpeedSynchronous Serial Bus Based on FPGA[J].Telecommunication Engineering,2008,48(11):92-96.(in Chinese)

[4]杨翠虹,文丰,姚宗.基于LVDS的高速数据传输系统的设计[J].通信技术,2010(9):59-61.

YANG Cui-hong,WEN Feng,YAO Zong.Design of Longdistance High-Speed Serial Data Transmission System based onLVDS[J].Communications Technology,2010(9):59-61.(in Chinese)

ZHANG Hong-liang was born in Penglai,Shandong Province,in1984.He received the B.S.degree from Harbin Engineering University in2008.He isnow anassistantengineer.His research direction is electronic communication.

Email:anywn310@163.com

Design of BLVDS Bus Based on FPGA

ZHANG Hong-liang

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

To solve problems of avionics system based on electrical bus,such as complex structure,low transmission rate,bad electromagnetic compatibility,a kind of Bus-Low Voltage Differential Signaling(BLVDS)based on FPGA is proposed.The structure of BLVDS bus is introduced and related key technologies are investigated including BLVDS communications and the method for BLVDS communicationsbased on FPGA by hardware description language.At the same time,the signal transmission quality is analysed,the high speed and high reliable bus transmission characteristics are verified in application of project,which provides important reference for new-style avionics high speed bus system.

avionics bus;data transmission;BLVDS;HDL

V243;TP336

A

10.3969/j.issn.1001-893x.2012.06.039

1001-893X(2012)06-1022-05

2011-11-01;

2012-04-10

张洪亮(1984—),男,山东蓬莱人,2008年于哈尔滨工程大学获学士学位,现为助理工程师,主要研究方向为电子通信。