基于PCI总线的HDLC通信卡的设计与实现

2012-03-15邓凤军王益忠

邓凤军,张 龙,王益忠

(中国卫星海上测控部,江苏 江阴214431)

PCI总线及在其基础上发展起来的CPCI总线,在工业控制、数据采集、信息通信、航空航天等领域得到了广泛的应用。高级数据链路控制(HDLC)是一个在同步网上传输数据并面向位的数据链路层协议,具有透明传输、可靠性高、传输效率高以及灵活性高等特点,可以实现点到点或者点到多点的数据传输,在路由器、网关等通信或者网络设备中应用广泛[1]。为了满足实际工作的需要,并为后续系统升级提供拓展空间,本文设计并实现了一款基于PCI总线、符合HDLC协议的通信卡,以满足高速数据传输的需要。通信卡采用PCI总线控制器实现PCI总线接口设计,采用FPGA实现HDLC通信协议及接口逻辑设计,采用RS-422标准对外通信,实现与外系统的互连。

1 HDLC通信卡总体方案

通信卡主要采用PCI9054和FPGA构成硬件系统,其硬件结构图如图1所示。数据传输流程为:接收数据时,通过RS-422接口芯片接收数据,数据格式满足简化的HDLC协议;通过FPGA内部的HDLC模块进行数据接收和串并转换;然后在本地控制逻辑的控制下通过PCI9054以DMA方式传给上位机,实现数据的接收和判读;发送数据时,上位机软件将数据以DMA方式传给PCI9054再输入FPGA,在其内部HDLC模块的作用下,进行数据并串转换和HDLC协议转换,最后通过RS-422发送器进行电平转换和数据发送。预留SDRAM以满足大容量数据通信需要。

2 HDLC通信卡电路设计

2.1 总线接口设计

PCI总线具有高性能、低成本、开放性、兼容性良好等优点,但PCI总线具有严格的时序关系和电气规范,使得开发工作量和难度比较大。PCI总线一般都采用各IC生产商设计的PCI专用接口芯片进行PCI总线设备的开发,以减少开发难度、降低工作量。基于此考虑,在本设计中,采用PLX公司的PCI9054芯片进行总线开发[2]。

PCI9054芯片满足PCI V2.2协议,可作为桥接芯片在PCI总线和本地总线(local bus)之间提供信息传输,既可以作为两个总线的主控设备去控制总线,也可以作为两个总线的目标设备去响应总线。其本地总线可工作在M、C、J三种模式,可方便地与多种微处理器连接。在C模式下,因本地总线的地址线和数据线分开,时序与控制逻辑比较简单,得到了广泛应用[3]。因此本通信卡中,PCI9054工作于C模式从设备方式,本地总线时钟采用40 MHz恒温补偿晶振。PCI9054的PCI总线端引脚按照对应关系与PCI总线金手指连接器相连,本地端地址总线为15 bit,数据总线为32 bit,控制总线包括ADS、BLAST、LHOLD、LHOLDA、LW/R#、READY、EOT# 引 脚 ,将它们分别与FPGA的IO口互连。

2.2 FPGA芯片选型与设计

HDLC协议是面向比特的高级数据链路控制规程,具有强大的差错检测功能、高效和同步传输的特点,利用它可以确保数据信息可靠互通。市场上有许多使用简单的专用HDLC芯片,但由于HDLC标准的文本较多,这些芯片出于专用目的难以通用于不同版本,缺乏应用灵活性,且其片内存储器容量有限。另一种方法是通过软件对MCU编程实现HDLC协议,虽然功能灵活、适应性强,但处理速度慢、占用处理器资源多,难以高速实现对 HDLC数据的插“0”和去“0”操作,一般只适用于路数较少的低速场合[4]。

为了实现与当前系统HDLC协议的兼容,本通信卡采用FPGA实现HDLC收发功能模块,充分利用FPGA硬件可编程的特点,发挥其速度快、灵活性高、并行处理信号、实时性能够预测的优势。同时,考虑到通信卡传输一帧数据的长度通常为512 KB~1 KB,而PCI9054的DMA只有32长字FIFO,且PCI读写速度与HDLC收发速度不一致,需要利用FIFO进行数据缓存,达到时序匹配的目的。为了提高系统集成度及其可靠性,采用FPGA内部存储单元实现FIFO功能。因此,综合考虑FPGA内部存储单元数量、IO引脚数量等,选择Altera公司的EP2C20-F240用于功能模块开发。EP2C20F240为QFP封装,可用IO口142个,内部LE 18 752个,内部RAM为239 616 bit,可以满足系统开发需要。

2.3 差分接口设计

通信卡对外通信采用RS-422方式传输数据,传输频率最高为768 kHz。因此,选用MAXIM公司的RS-422发送器MAX3032E和接收器MAX3094E,其数据传输率最高分别可达20 Mb/s和10 Mb/s,满足数据高速传输需要。

3 HDLC通信卡逻辑设计

通信卡上的FPGA完成PCI9054本地总线数据读写时序逻辑的转换,实现HDLC收发模块和FIFO数据缓存功能。设计中采用VHDL硬件描述语言实现各功能模块,利用Altera公司的集成开发环境Quartus II(11.0)完成相关的编译、调试、下载等开发工作。

3.1 本地总线数据读写模块

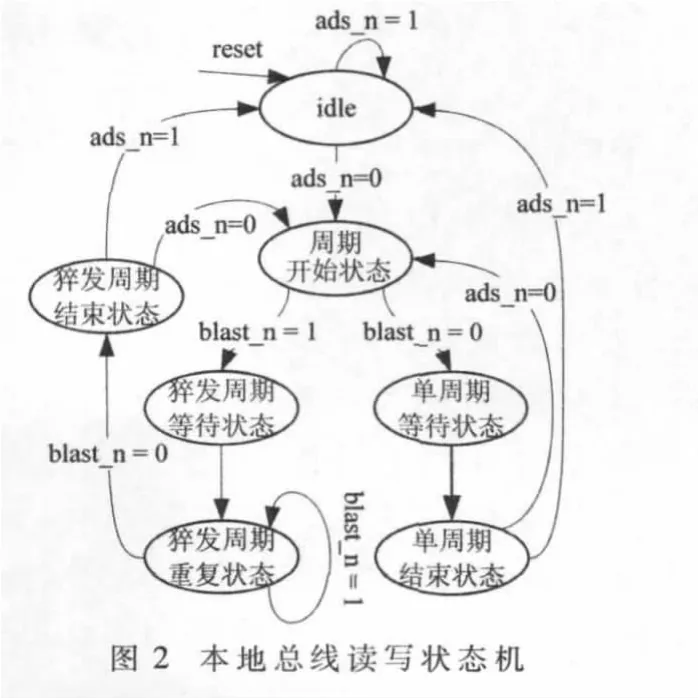

PCI9054工作于C模式从设备方式,采用分散/聚合(Scatter-Gather)DMA方式进行数据快速传输,以发挥其速度快的优势。根据PCI9054读写时序图可知,在C模式从设备方式下,FPGA读取PCI9054本地端ads_n和blast_n的引脚状态,判断是单周期读写状态还是猝发读写状态,实现地址获取和数据读写,其状态机如图 2所示。同时,在上位机读数据完毕后,如果读FIFO为空则将EOT#引脚拉低,将数据传输结束信号上传,强行停止主机数据读操作。这就需要在DMA初始化过程中,设置DMAMODE寄存器的第14位为EOT#有效模式。

3.2 HDLC通信模块实现

HDLC的标准帧格式如表1所示,但HDLC也有由用户定义的非标准帧格式,常用于点对点的通信中。在非标准格式中,地址段、控制段、CRC段是可选的。本通信卡主要用于点对点通信,且采用简化的HDLC协议,即省略地址段、控制段、CRC段。其中CRC校验功能由上位机软件实现[4-5]。

表1 HDLC的帧格式

HDLC是面向位的,在待传数据中出现与标志字一样的数据时,如果不进行处理,就会被误认为是帧边界。为了避免此错误,HDLC规定采用“零比特填充法”使一帧中两个字段之间不会出现6个连续1。具体做法是:发送数据时,先进行帧数据扫描,只要发现有连续的5个1,则立即插入一个0,以此保证数据中不会出现连续6个1;接收数据时,先找到3E字段以确定帧的边界,接着对其后的比特流进行扫描,每发现5个连续1就将其后的0删除,以此保证所传比特流中不出现帧标志,直到帧尾标志出现,从而实现HDLC在链路层的“透明传输”,保证发送端可以发送任意组合的比特流信息,而接收端都能准确无误地接收到[6]。

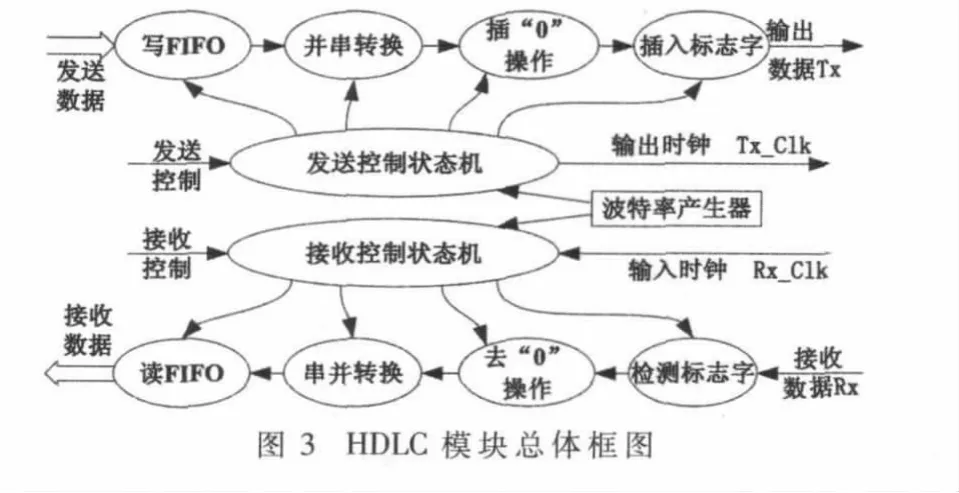

FPGA中实现的简化HDLC模块总体框图如图3所示。读写FIFO采用Altera公司的LPM功能模块实现,大小可根据需要设置,本通信卡设为512×32 bit。发送数据时,写FIFO接收 PC数据(总线宽度为 32 bit),首先进行并串转换,再进行插“0”操作,最后插入标志字按位发送出去,输出数据Tx和输出时钟Tx_Clk保持同步,整个过程由发送控制状态机进行控制。接收数据与发送数据过程相反,由接收控制状态机进行控制。其中输入、输出时钟可以设置为68 kHz或者768 kHz。

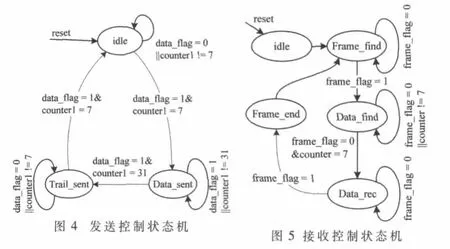

发送控制状态机和接收控制状态机分别如图4、图5所示。发送数据时,发送状态机首先判断写FIFO是否有数据,若有数据,则插入帧头,依次读取FIFO数据,完成插“0”操作和插帧尾操作,并按照从低到高的顺序发送数据,直至写FIFO为空。接收数据时,首先搜索帧头,为了防止接收到连续两个标志字而把后一个标志字误认为是数据,设置搜索数据状态(Data_find),若不是标志字,则作为数据进行去“0”操作,完成串并转换和帧尾检测,并将接收到的数据以32 bit为单位,逐次写入读FIFO中。当一帧传输结束,采用中断信号通知上位机及时读取数据。一旦检测到丢弃序列(0x7F),则结束对此帧数据的处理,并清空读FIFO里的数据,同时上报PC机错误信息,请求发送方重新发送数据。

3.3 功能时序图

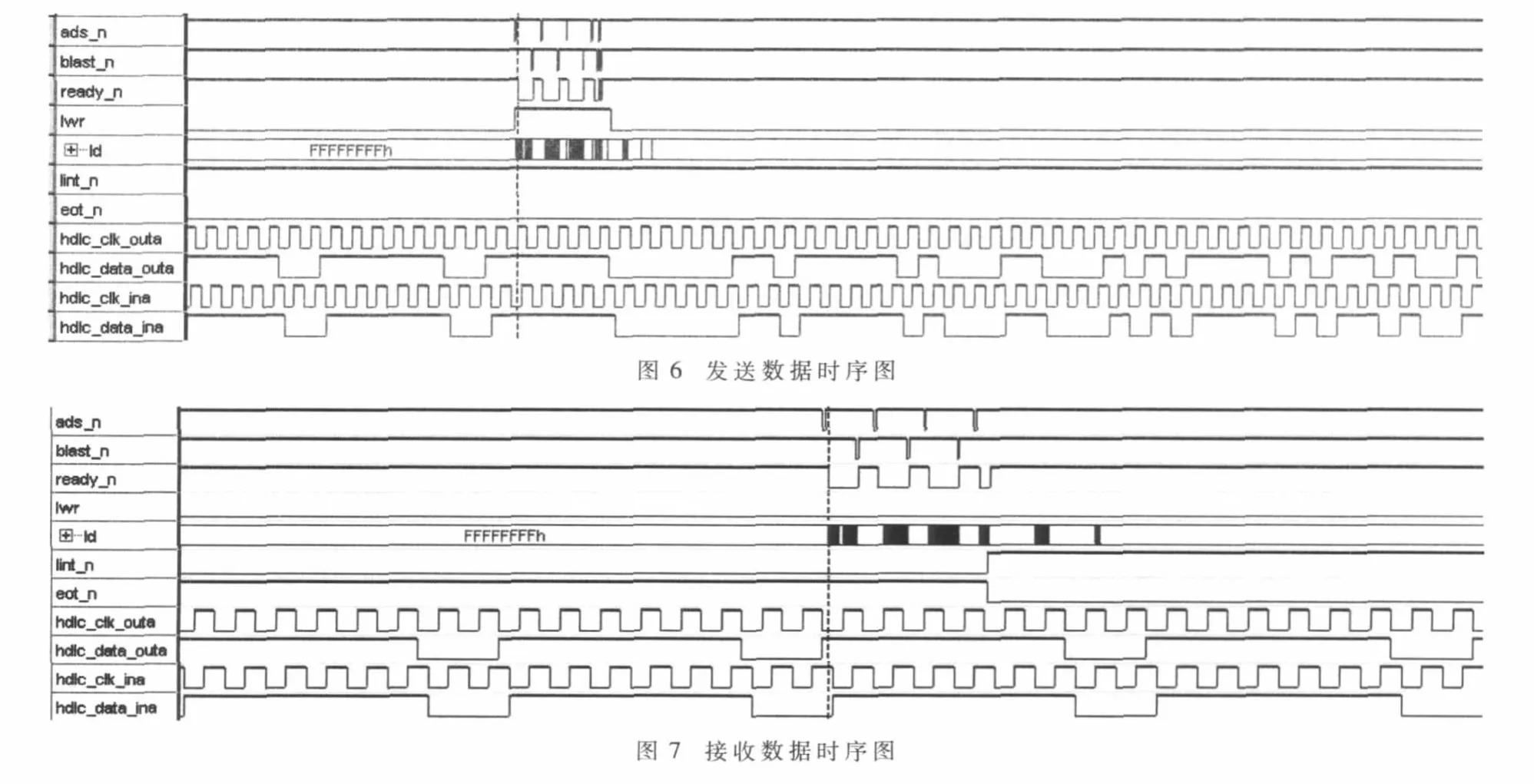

图6、图7分别给出了利用Quartus II的在线逻辑分析仪SignalTap II获取的PCI写数据、HDLC数据发送和HDLC接收、PCI读数据的时序波形图。从图中可以看到,HDLC模块正确实现了插“0”和去“0”操作,并能与PCI9054进行正确的数据收发。

本文采用PCI总线控制器PCI9054和FPGA技术设计实现了一款符合简化HDLC协议的通信卡,并已成功应用于实际工作中。实际应用表明收发数据正确,可以满足高速数据通信要求。同时,该通信卡设计中预留了一定的扩展空间,能够根据需要进行功能拓展。本通信卡可应用于信号处理、数据通信等场合,对PCI总线应用设计有一定的参考价值。

[1]罗文翰,张剑锋.基于MPC860的 HDLC通道驱动程序的设计与实现[J].电子技术应用,2005,31(15):66-68.

[2]张素兰,余国辉.基于PCI总线的高速串行通信模拟系统的设计与实现[J].计算机工程与设计,2007,28(15):3617-3620.

[3]陈斌,王成华,夏永君.基于DSP和 PCI的通用数据采集及处理卡实现[J].计算机应用研究,2005(1):171-173.

[4]罗力凡,常春藤.基于 VHDL的 FPG开发快速入门·技巧·实例[M].北京:人民邮电出版社,2009.

[5]陆园琳,乔庐峰,王志功.多通道高速HDLC处理器的设计与实现[J].电子学报,2003,31(11):1630-1634.

[6]马萍,唐卫华,李绪志.基于 PCIExpress总线高速数采卡的设计与实现[J].微计算机信息,2008,28(9-1):116-118.