FPGA设计中的亚稳态及其缓解措施

2012-03-15汪路元

汪路元

(北京空间飞行器总体设计部,北京100094)

在进行 FPGA设计时,往往只关心“0”和“1”两种状态。然而在工程实践中,除了“0”、“1”外还有其他状态,亚稳态就是其中之一。亚稳态是指触发器或锁存器无法在某个规定时间段内达到一个可确认的状态[1]。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在亚稳态期间,触发器输出一些中间级电平,甚至可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。亚稳态是异步数字电路设计中的固有现象,但是由于其偶发性和温度敏感性的特点,在产品前期测试过程中很难发现。当前多个型号的FPGA产品研制过程中暴露的质量问题均与亚稳态有关,而且多是在设备研制后期进行高低温试验时出现,严重影响了产品研制。因此,亚稳态对系统的危害性应该引起足够重视,并在设计初期阶段应采取有效缓解措施,以提高系统的可靠性。

1 亚稳态产生的原因

所有数字器件(包括FPGA)的信号传输都有一定的时序要求,以保证每个器件将捕获的输入信号正确输出。对于触发器,为了确保操作的可靠性,输入信号必须在时钟沿的某段时间(触发器的建立时间)之前保持稳定,并且持续到时钟沿之后的某段时间(触发器的保持时间)才能改变,而且该触发器的输入反映到输出还需要经过一定的延时(时钟到输出的时间)。如果数据信号的变化违反了建立时间或者保持时间的要求,则触发器的输出会处于亚稳态。此时,触发器的输出会在高电平“1”和低电平“0”之间盘旋一段时间,这也意味着触发器的输出达到一个稳定的高或者低电平的状态所需要的时间会大于时钟到输出的时间。这样触发器输出端Q在有效时钟沿之后较长一段时间处于不确定状态,这段时间称为决断时间。在这段时间里Q端可能为毛刺、振荡或某一固定电压值,而不是等于数据输入端D的值。经过决断时间之后 Q端将稳定到“0”或“1”上,但究竟是“0”还是“1”,是随机的,与输入没有必然的联系。图1所示是第一级触发器存在建立时间或保持时间冲突时导致Q1出现亚稳态的示意图。

图中,tsu为触发器建立时间;th为触发器保持时间;tco为输出相对于时钟沿之后的延迟时间;tres为决断时间;tw为触发器输入数据变化可能形成亚稳态现象的时间窗口,这个时间窗口由建立时间和保持时间两部分组成;tnet为第一级触发器输出至第二级触发器输入端的传输延时。

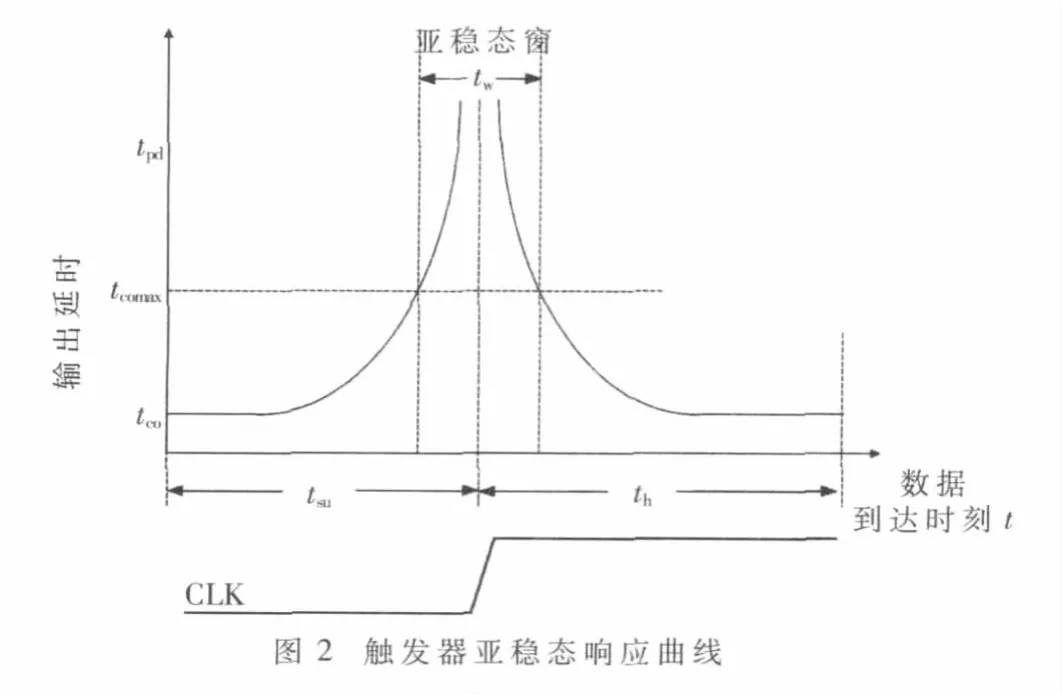

触发器稳态输出是在时钟信号CLK的上升沿之后经过tco延时,将输入数据反映到输出端,但是在亚稳态发生时,输出端数据将再经过 tres后才随机稳定在“0”电平或“1”电平上,与输入数据没有必然联系。图2是触发器亚稳态响应曲线[2],横轴为数据到达时刻(相对于时钟信号的上升沿),纵轴为输出延时。当数据输出延时超过tcomax时,触发器输出就会出现亚稳态,对应的数据达到时刻正好是建立时间和保持时间的临界点。

2 亚稳态与系统可靠性

由于亚稳态输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态对系统的影响主要表现在以下两个方面:

(1)导致后端电路产生逻辑误判,尤其是多扇出电路中,由于扇出延时的差别会导致各负载端识别出不同的逻辑电平,使系统功能发生紊乱。

(2)输出0~1之间的中间电压值还会使下一级产生亚稳态,即导致亚稳态在系统中传播。

亚稳态的出现是一种概率现象,并且结果正确与否也是一种概率现象。因此,为了便于估算,工程实践中提出了一种统计模型来评估亚稳态所造成的危害程度,即平均无故障时间MTBF(Mean Time Between Failures)。MTBF的定义如下[2]:

式中,fC为时钟频率,fD为输入数据变化频率,tr为最大可用决断时间,T0和τ为与器件电气特性和工艺特性相关的常数。值得注意的是,亚稳态本身与器件工作频率无关,但是MTBF与时钟频率相关并成反比,所以系统工作频率越高,MTBF越小,亚稳态引起故障的概率也就越高。

MTBF的计算对象是一个触发器,在实际中器件生产厂家先通过特殊的测试手段得到产品的MTBF,然后再确定公式中的参数指标向外发布。用户可以根据这些参数指标定量计算当前设计的可靠性。对于常用的Actel公司的FPGA和Xilinx SRAM型FPGA,器件厂商均公布了T0和τ的数值[3-4],实际使用时可以进行评估计算。

3 FPGA设计中的亚稳态缓解措施

在FPGA设计中,只要不满足内部触发器的建立时间和保持时间要求,就会出现亚稳态。对于一个全同步设计来说,时钟和数据相位关系固定,所有触发器都由一个时钟信号驱动,虽然在不同点也存在相位差别,但开发工具会通过计算时钟信号线的走线长度来预测传输延时,并通过时钟域内的时钟树综合算法来求得优化的结构,使触发器的建立时间和保持时间满足要求,不出现亚稳态,这也是所有设计规范都推荐采用全同步设计的一个重要原因。但是,实际的系统一般都不只有一个时钟,而是一个多时钟系统,例如常见的下行链路数据复接设备,一般是有多少路输入就有多少个时钟,因而需要分析其中的异步传输路径并采取缓解措施。

3.1 针对单比特信号异步传输的亚稳态缓解措施

(1)慢时钟域信号进入快时钟域(两者周期相差1倍以上)

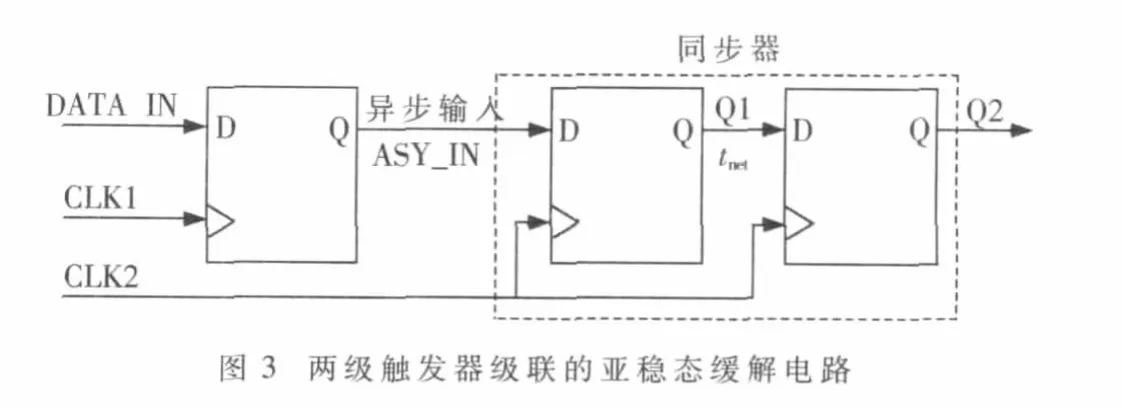

慢时钟域信号进入快速时钟域是工程实践中遇到最多的一种情况,输入信号从CLK1时钟域进入到CLK2时钟域时可以通过两级触发器级联的方式来缓解亚稳态,具体电路如图3所示。

图3电路中,由于无法预知异步输入信号ASY_IN的翻转时刻,所以同步器第一级触发器的输出Q1存在亚稳态,该信号通过FPGA布线路径传输至第二级触发器的输入端。设CLK2的时钟周期为T,且假定CLK2到两个触发器的时钟延时相等(即偏斜为零),第一级触发器输出到第二级触发器输入端的路径传输延时为tnet,其余时序参数定义同图1。则只要满足 tco+tres+tnet+tsu≤T,Q1就有足够的时间从亚稳态恢复至稳定态,并满足第二级触发器的建立时间要求,所以第二级触发器的输出是稳定态。同时还要注意的是,信号在CLK2时钟域内会有T~2T的延时。

设计中,可以通过增加触发器级联的数目来获得更大的MTBF,但是这样会进一步增大信号延时并占用更多FPGA资源。综合考虑现有FPGA器件工艺和电气参数,一般情况下,二级触发器的级联已经可以满足实际要求了。

(2)慢时钟域信号进入快时钟域(两者周期相差1倍以内)

从亚稳态的机理可以知道,图3中Q1的亚稳态恢复结果可能是“0”也可能是“1”,所以要求 CLK1的周期必须是CLK2周期的2倍以上,才能保证当异步输入信号为单周期脉冲时,在CLK2时钟域信号不丢失。所以对于两个时钟周期相差1倍以内的情况,图3的电路是不合适的,可以采用图4所示的脉冲扩展同步电路来缓解亚稳态。

图4电路中,通过“异或”逻辑在第一个时钟域内对信号宽度进行扩展,然后采用两级触发器进行同步来实现。

(3)快时钟域信号进入慢时钟域

当信号从快速时钟域进入慢时钟域时,图3和图4电路都可能会引起输入信号的丢失,这种情况下可以使用图5所示的窄脉冲检测电路来实现。

3.2 多比特并行信号异步传输的亚稳态缓解措施

在许多应用中,跨时钟域传送的不只是简单的单比特信号,很多时候是并行数据信号的跨时钟域传输。这种情况下,不能简单地对并行信号的每一位独立使用图3所示同步器。因为实际电路中无法保证并行信号同时翻转,这样做会导致输出采集到错误的信号值,对系统功能产生影响。针对这种应用可以采用异步FIFO或双口RAM来解决[5]。

在FPGA中,有现成的RAM硬核,设计时可以通过开发工具配置这些RAM的使用方式,可配成异步FIFO或双口RAM。该类存储器读写控制分别采用两个完全独立的时钟域,异步FIFO内部采用格雷码计数器进行编址,操作简单,提供了现成的半满、全满和空信号(这些信号均经过了跨时钟域处理,可以直接在读时钟域和写时钟域使用)。当采用双口RAM时,需要自行处理地址信号的跨时钟域,此处需要注意的是,要将多比特的地址信息在各自时钟域中转化为单比特,然后再使用单比特同步器来解决。

3.3 异步复位过程的亚稳态缓解措施

异步复位由于其实时性好、设计简单以及与FPGA底层库单元(带异步复位的触发器)结合性好等特点,受到广大设计师的青睐,但是在使用过程中往往忽略了其中的亚稳态问题。类似于触发器对输入信号建立时间和保持时间的要求,异步复位信号在释放时有恢复时间(Recovery time)和移除时间(Removal time)的要求,如图6所示。

图中,trec为恢复时间,指复位信号释放时刻与紧随其后的有效时钟沿间的最小时间;trem为移除时间,指时钟有效沿时刻与之后的复位信号释放之间的最小时间。这就要求异步复位释放时刻与时钟的有效沿尽量远,即异步复位应该和时钟没有任何关系。其实不然,对于触发器,异步复位信号对内部保持电路和直接输出电路都有影响。当复位信号有效时,输出清零;当复位信号释放后,输出由保持电路决定,如果复位信号释放时刻离时钟沿太近,则输出会在清零和数据保持之间出现亚稳态。

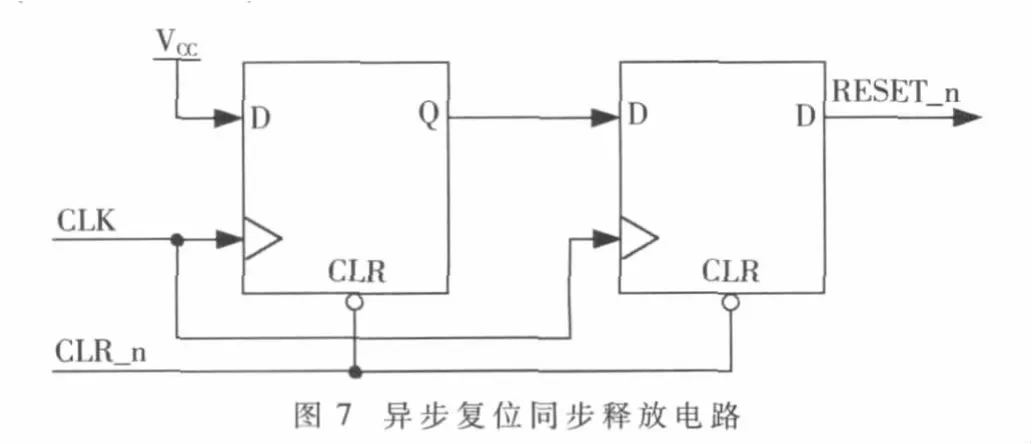

实际电路中,可以采用异步复位同步释放的方式来缓解复位导致亚稳态的影响。低电平有效的异步复位同步释放实现电路如图7所示。图7电路既保持了异步复位实时性好的优点,又缓解了复位释放时刻的亚稳态,实际应用中可以参考。

随着FPGA功能复杂度和运行频率的大幅提升,亚稳态已经成为危害系统可靠性的重要隐患,必须在设计初期采取缓解措施,以获得满足要求的MTBF,将亚稳态的影响降低至系统允许范围。根据实际需要,灵活运用文中的缓解措施,便可以减小亚稳态的影响,提高系统可靠性。

[1]沈立,朱来文,陈宏伟,等译.高速数字设计[M].北京:电子工业出版社,2004:96-105.

[2]FOLEY C.Characterizing metastability[C].Proceedings of Second International Symposium on Date of Conference.Conference Publications,1996:175-184.

[3]Xilinx Corporation.Metastability considerations[R].1997.

[4]Actel Corporation.Metastability characterization report for actel antifuse FPGAs[R].2006.

[5]CUMMINGS C E,ALFKE P.Simulation and synthesis techniques for asynchronous FIFO design with asynchronous pointer comparisons[C].SNUG 2002(Synopsys Users Group Conference,San Jose,CA,2002)User Papers,March 2002.Section TB2,3rd paper.2002.