基于实时解调的AIS信号侦察

2012-03-06侯聪

侯 聪

(中国西南电子技术研究所,成都 610036)

1 引 言

船舶自动识别系统(AIS)是由国际海事组织(IMO)、国际助航设备和航标协会(IALA)以及国际电信联盟(ITU-R)共同提出的技术标准,可用于船舶避碰、水上智能交通管理及海域监视等领域。对于AIS信号的侦察,有利于掌握一定范围海域内的船舶情况,对于海事态势的掌握、海防安全、打击走私、反海盗等都有重要意义[1]。

本文结合FPGA,对于AIS信号侦察的数字信号处理部分,提出了一种较通用的设计实现方案,主要手段包括对AIS信号的实时解调,得到内涵信息;以及在对采样数据和解调数据加上精确时标后,完成存储传输,为后续的各种处理手段提供原始数据。

2 系统概述

2.1 系统的组成和工作原理

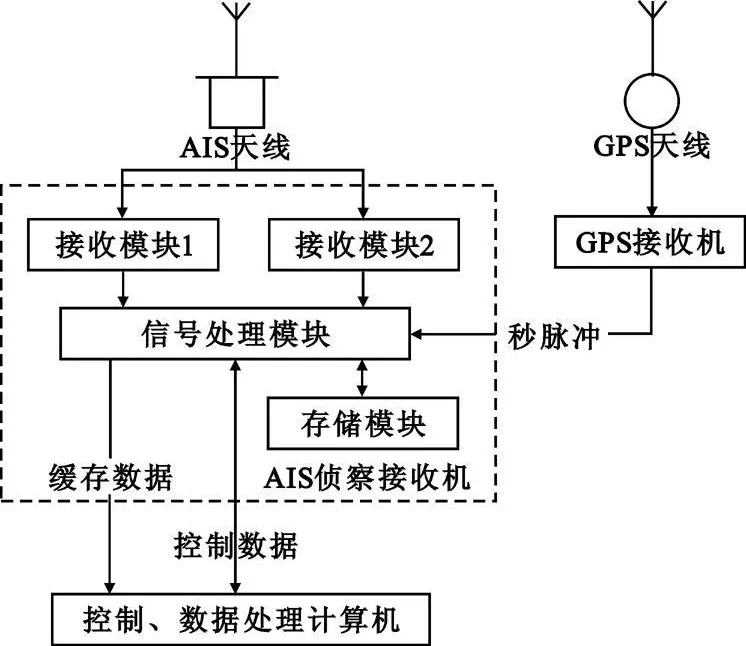

系统组成如图1所示,主要由AIS接收天线、AIS侦察接收机、存储器、GPS天线及GPS接收机,以及后端的计算机组成。

系统中的两个接收模块,目的在于能够同时完成两路不同频点AIS信号的接收;信号处理模块对中频信号进行带通采样、数字下变频[2],完成信号的解调,并根据不同工作模式选择将处理数据实时传输或存储在固态存储器中;后端计算机完成与AIS侦察接收机的通信控制功能,还可以根据实际需要,增加显示、后续等功能。

图1 AIS侦察系统的组成Fig.1 Composition of AIS reconnaissance system

2.2 AIS侦察数字信号处理的主要性能

AIS侦察数字信号处理部分的主要性能包括:

(1)能实时侦收两路不同频点的AIS信号,完成AIS内涵信息的解析;解调方式GMSK 9.6 kbit/s,解调性能20%PER(误包率);

(2)具有原始采样数据和解调数据的存储功能,存储数据通过对外接口输出;能对AIS解调结果和基带存储数据进行时标标注。

3 AIS侦察信号处理的实现

3.1 AIS信号侦收解调相关算法

3.1.1 测频算法

AIS信号调制方式为GMSK,载波分量在信号FFT频谱上不明显,如采用求频谱重心的方法测频则误差较大,本设计中采用信号非线性变换再FFT测频的方法。对输入信号直接平方,对平方后的信号进行FFT,根据谱峰最大值和次大值处对应频率的均值即信号的频率。

3.1.2 AIS信号基带解调算法

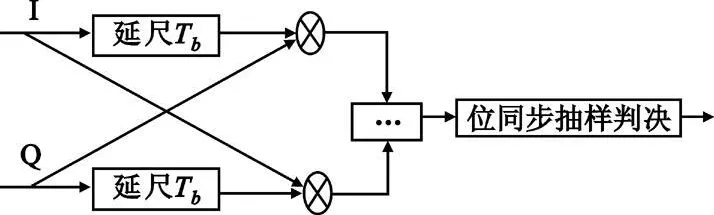

硬件实时解调采用的是1 bit差分非相干解调的算法。AIS采样信号经变换成基带I、Q信号后,根据1 bit差分检测算法找出在1 bit周期内接收到的信号在相位方面的改变量,对改变量进行抽样判决后即得到AIS信息比特流[3]。

图2 AIS基带解调算法原理Fig.2 Principle of baseband AIS demodulation

3.1.3 匹配序列训练、位同步和信号结尾搜索

训练序列匹配是利用AIS信号帧头的特点,将差分鉴频判决为[-1+1]的序列与标准模板序列进行相关,当阈值大于门限时认为有AIS信号,此时还需要确定同步头的起始位置,所以在大于阈值之后的一段时间内还需要对相关计算最大值位置进行搜索,搜索范围为从大于阈值开始到随后计算的若干个数据中找到最大值位置,此处即作为有效数据的起始位置。

通过训练序列匹配发现有AIS信号时,根据训练得到的匹配序列起始时刻、码片长度和当前采样率,可以计算出每个码片的最佳采样时刻,并在最佳采样时刻时取出AIS信息比特流中的数据,得到解调数据。

最后,对解调数据进行分析,当连续出现7个码片的“1”或者“0”时,表示发现AIS信号的结尾,完成一个完整的AIS信号解调,单次解调结束。

3.2 硬件设计和实现结构

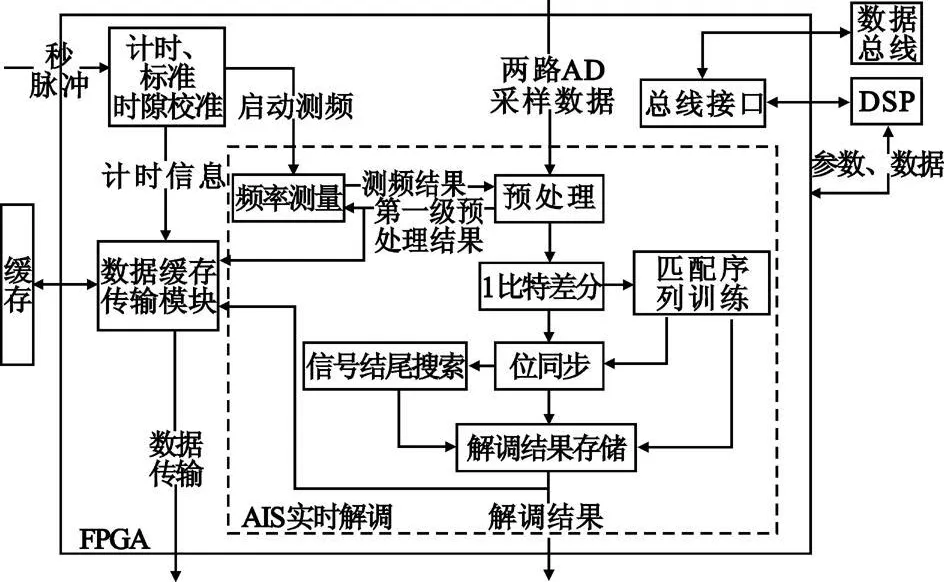

信号处理模块的硬件设计是以AD+FPGA+DSP为基础构建的平台,基于多平台应用、低成本等因素,FPGA选择Xilinx公司的Virtex2-3000系列芯片,DSP选择TI公司的TMS320VC33系列。

在前文的系统构成中可见,AIS侦察接收机的功能集中在信号处理模块实现;而在信号处理模块中,其主要功能基本在FPGA中完成,包括数字解调、数据存储传输、总线接口等。FPGA的数字信号处理设计实现结构如图3所示。

图3 FPGA数字信号处理实现结构Fig.3 Architecture of digital signal processing in FPGA

信号处理对两路AIS信号完成相同的数字信号处理功能。FPGA内的设计按功能可以划分为4部分,即AIS实时解调、计时和标准时隙校准、数据缓存输出、总线接口。

AIS实时解调完成对输入信号的预处理、测频、基带解调、位同步等处理,最终可以实时得到两路信号的解调结果,并提供预处理结果和解调结果两种数据给缓存输出模块,是FPGA内设计的核心部分。

计时和标准时隙校准模块通过秒脉冲和FPGA内部时钟激励计时,利用AIS信号时间上的规律,在每个标准时隙开始时产生测频启动信号,是实时解调模块的关键控制信号来源,并为各种数据的缓存提供高精度的时标。

数据存储输出模块设计时,考虑后续的数字信号处理,选择AIS采样信号或者解调结果作为数据源,同时利用FPGA内的高精度计时,给数据打上时标;再考虑到实际应用中,可能面对的平台数据总线被占用,在本系统无法将实时数据输出时,可以将数据先存储在内部缓存中,事后再通过平台数据总线输出。

总线接口的设计给系统内的AIS侦察接收机提供了一个对外的接口。通过FPGA完成的DSP和数据总线之间数据交互,平台或者后端的控制单元可以完成对AIS侦察接收机的控制和数据交互。

3.3 AIS信号实时解调的实现

对AIS信号进行侦收时,在FPGA内实现的实时解调结构和流程如图4所示。

图4 FPGA内实时解调的实现结构与流程Fig.4 Implementation of real-time demodulation in FPGA

测频模块中,先对该信号进行2倍抽取,再完成FFT运算,测频精度为10 Hz级,得到的测频结果作为第二级预处理下变频的参数。频率测量中需要注意的是测频时间选取原则,详见下文计时、标准时隙校准的实现。值得注意的是,由于FFT测频有较大延时,为达到实时解调的目的,在第一级预处理后增加了缓存模块,并且对后续的第二级预处理和数字解调都采用乒乓操作。利用FPGA工作时钟频率高、处理效率高的特点,以增加资源消耗为代价,提高设计的实时处理能力。乒乓操作的控制主要在测频结果到第二级混频的选择输入和解调结果的选择输出,设置解调标志位作为判断依据,解调标志位在完成单次的AIS信号解调后翻转。

在精测频的引导下,完成第二级预处理后得到基带信号,按照3.1节中的相关算法完成对信号的基带解调得到目标信息比特流;再经由匹配序列训练完成对目标信号的帧头以及最佳采样点的搜索;根据前面搜索到的最佳采样点信息,结合采样率、码片长度等信息,位同步模块完成码元的提取,得到解调数据;再对得到的解调数据进行信号结尾搜索,得到结束标志;最后,利用搜索到的帧头和结尾的时刻,控制对解调数据的存储,将包括帧头在内的完整有效的AIS解调数据存储下来,经过乒乓控制模块选择输出,得到最终的解调结果。

3.4 计时、标准时隙校准的实现

计时、标准时隙校准模块是设计中重要的控制部分,主要工作原理是利用AIS信号发射时间上的特点,根据GPS的标准时计时产生测频启动信号和精确的计时信息,提供给测频模块和数据存储输出模块使用。其实现结构如图5所示。

图5 FPGA内计时、标准时隙校准的实现Fig.5 Timer and calibration for standard slot in FPGA

其中秒计数器和微秒计数器设计均为32位,因为32位的秒计数器能够以某年某月某日零时为起始时刻进行累加,而在若干年内不会溢出;微秒计数器工作时钟为10MHz级,计时精度10 ns级,32位的宽度也保证了微秒计数器在1 s内的计数不会溢出。

标准时隙校准利用AIS信号在时间上的特点:1 min分为2250个标准时隙,以2 s为单位每2 s则有75个标准时隙,依此为基准来判断地面标准时隙时刻。每个时隙长度26.6666 ms,而计时精度为10 ns级,能够精确地找到每个时隙的开始时刻(误差小于等于100 ns,可以忽略),产生测频启动信号,并且利用前面提到的2 s 75个时隙的标准,周期性地校准,避免长期计时可能产生的误差。

3.5 数据存储和传输的实现

FPGA内数据存储和传输的实现如图6所示。其主要功能是,根据外界设置的参数,选择性地将相关数据存储或者通过对外接口输出。输入到本模块的数据有两种:第一级预处理的结果和解调结果。选用第一级预处理而不是采样数据的原因是,信号本身带宽较窄,可以使用采样率较低的预处理数据提供给后端,作为AIS信号侦察的原始数据;同时,使用较低采样率的数据,也有利于后续两路信号数据实时输出的实现。

数据存储时,可以完成同时对两路信号的第一级预处理结果的实时存储,或者两路信号最终解调结果的实时存储;数据传输时,可以完成对两路信号的第一级预处理结果的实时传输,或者对两路信号最终解调结果的实时传输,或者将缓存内数据输出。传输过程中,完成数据选择后,根据系统传数组帧的定义,对数据进行重组,再通过对外接口输出。

图6 FPGA内数据存储和传输的实现Fig.6 Data storage and transmission in FPGA

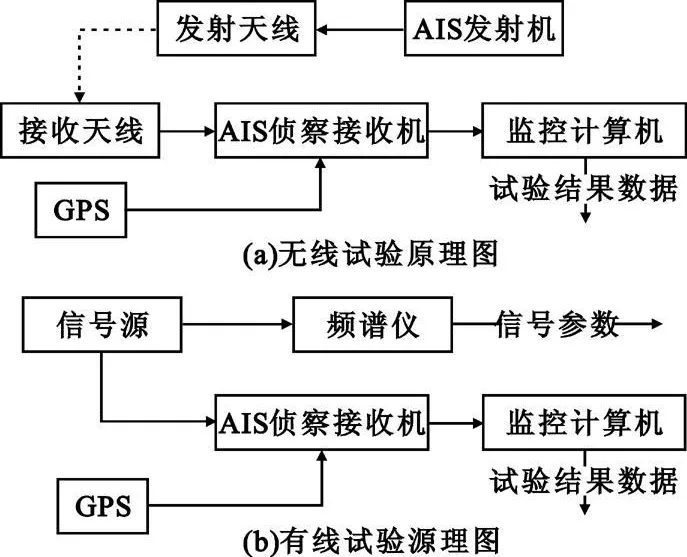

4 试验与结果分析

为验证上述方法实现的AIS侦察接收机效果,进行了无线和有线两种方式的实时侦收试验。无线试验主要验证该系统在实际无线环境中的工作效果,有线试验主要用于各种指标的测试,其原理图如图7所示。两种方式的试验结果数据都在监控计算机中读取,监控计算机通过CAN和LVDS与AIS侦察接收机完成交互数据,并将试验结果数据存储在其中。试验结果数据主要包括实时解调后输出的数据和实时采样后输出的数据,频谱仪读取的信号参数包括频率、幅度等信息。

图7 试验原理Fig.7 Test principle

在有线和无线实验测试环境下,改变信号强度和信噪比的AIS信号,通过对各种实验数据的分析,得到以下实验结论:

(1)本设计实现的AIS侦察数字信号处理能同时完成两路信号的实时解调,解调方式GMSK 9.6 kbit/s;在有线条件下,中频输入较小(不大于-30 dBm)时,解调性能达到误包率不大于20%;

(2)本设计实现的AIS侦察数字信号处理能同时完成两路信号的实时数据存储传输功能,通过特殊数据序列和AIS解调结果数据测试,在较长时间内(大于等于1 h)能保证数据实时、有效存储传输。

5 结束语

根据设计方案实现的AIS侦察接收机,处理能力较强,能同时完成两路AIS信号的实时解调、数据存储传输;可扩展性和通用性强,能实时存储输出带高精度时标的采样数据和解调数据,为后续的各种处理手段提供了有效可靠的数据,可以应用于多种场合下的AIS信号侦察;并且,在实现的结构流程和器件选择方面,综合考虑了成本控制,设计实用性高。

[1]CerveraM A,Ginesi A.Satellite-basedAIS SystemStudy[C]//Proceedings of the 26th International Communications Satellite SystemsConference.San Diego,CA:IEEE,2008:1-6.

[2]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:21-56.YANG Xiao-niu,LOU Cai-yi,XU Jian-liang.Software radio principle and application[M].Beijing:Publishing House of Electronic Industry,2001:21-56.(in Chinese)

[3]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992:262-270.CAO Zhi-gang,QIAN Ya-sheng.Modern communication theory[M].Beijing:Tsinghua University Press,1992:262-270.(in Chinese)