基于边界扫描技术的板级测试分析

2012-02-15朱振军宋月丽

朱振军,林 明,宋月丽

(1.江苏科技大学 电子信息学院,江苏 镇江 212003;2.中国船舶重工集团第723研究所 江苏 扬州 225001)

随着微电子技术、微封装技术和印制板制造技术的不断发展,印制电路板变得越来越小,密度越来越大,复杂程度越来越高,使用万用表、示波器测试芯片的传统“探针”方法已不能满足要求。在这种背景下,早在20世纪80年代,联合测试行动组(Joint Test Action Group,JTAG)就起草了边界扫描测试(Boundary Scan Testing,BST)技术规范,后来在 1990 年被批准为IEEE标准1149.1-1990规定,简称JTAG标准。该规范提供了有效地测试引线间隔致密的电路板上元器件的能力[1]。

边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。边界扫描测试是通过在芯片的每个输入输出 (Input or Output,I/O)引脚附加一个边界扫描单元(Boundary Scan Cell,BSC)以及一些附加的测试控制逻辑实现的[2]。它通过对JTAG接口连接起来的链路施加测试向量,然后读取存在于器件输入输出管脚与内核电路之间的边界扫描单元返回的数据,并进行对比来完成测试。边界扫描技术大大提到了器件的可控性和可视性,可以方便地完成电路板的板级测试。

1 边界扫描技术原理

边界扫描的测试总线一般由4个专用的测试存取通道(Test Access Port,TAP)组成:测试时钟输入线 (Test Data Input,TCK)、测试模式选择线(Test Mode Select,TMS)、串行测试数据输入线(Test Data Input,TDI)、串行测试数据输出线(Test Data Output,TDO)[3]。 IEEE1149.1 标准还提供了一个可供选择的输入信号 “测试系统复位 (Test Reset System,TRST)”,功能是控制测试存取通道控制器的异步初始化。为了保证测试逻辑的确定性,当测试系统复位上施加的信号从0变为1时,TMS在逻辑1上要保持几个TCK时钟周期。元器件与外部通信的信号必须通过TAP。

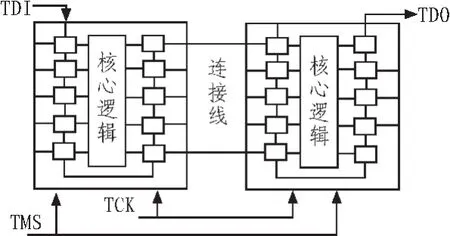

如图1所示,边界扫描技术的工作原理是:在测试时钟信号的基准上,边界扫描测试系统将测试数据以串行方式由TDI输入到边界扫描寄存器中,再通过TMS传送测试控制信息,经TAP控制器译码并控制边界扫描单元完成测试数据的加载和响应数据的采集,再通过测试数据通道将捕获到的数据输出至TDO,最后由TDO送到边界扫描测试系统。边界扫描测试系统将捕捉到的响应数据和期望的响应进行比较即可快速的判断电路的连接状态。边界扫描技术不仅可测试芯片内部的逻辑功能[4],还可以通过控制多个芯片的测试通道而测试芯片之间或电路板之间的连接是否存在故障。

图1 边界扫描测试原理图Fig.1 Schematic diagram of Boundary Scan Testing

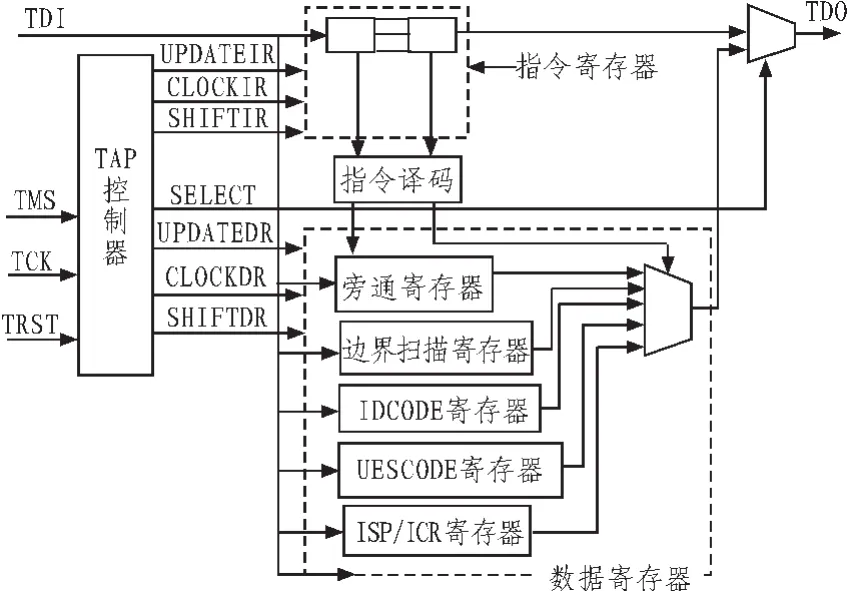

基于边界扫描设计法的元器件的所有与外部交换的信息(指令、测试数据和测试结果)都采用串行通信方式,允许测试指令及相关的测试数据串行送给元器件,然后允许把测试指令的执行结果从元器件串行读出。如图2所示,一个典型的边界扫描系统包含以下硬件组成:1)JTAG接口,一般情况下只需要四个接口即可,即 TDI、TCK、TDO、TMS(TRST 可选,非必需接口);2)TAP控制器,用于控制JTAG进入某种特定状态;3)指令寄存器,用于寄存采样指令(SAMPLE)、外测试指令(EXTEST)等测试模式的指令编码;4)指令译码器,用于译码指令寄存器中的指令编码并作为多通道数据选择器的控制端;5)数据选择器,用于将指令所对应的数据寄存器中所寄存的数据选择输出;6)数据寄存器,包含几种类型:旁路寄存器、边界扫描寄存器、取器件标志指令(IDCODE)寄存器等,用于存放在TDI的激励下产生的各种响应信号数据。

图2 边界扫描的基本结构图Fig.2 Structure diagram of Boundary Scan

2 边界扫描板级测试方法及流程

电路板上各器件之间的连接方式大致可以分为4类:1)JTAG器件之间的互连;2)JTAG器件和 JTAG器件及非JTAG器件均相连;3)JTAG器件和非JTAG器件间的互连;4)非JTAG器件之间的互连。在板级测试中,边界扫描技术可以覆盖到前3类连接关系[5]。对一个含有边界扫描芯片的电路板测试可分为3个大方面。

2.1 边界扫描器件的完备性测试

完备性测试是进行边界扫描其他任何测试之前建议首先进行的测试操作,以确保边界扫描链能正常工作。完备性测试可以检测时钟TCK和模式选择TMS的输入端连接是否正确,所提供的有关信号是否正常;数据输入TDI和数据输出TDO端的连接是否正确,且输入和输出的功能是否正常;内部的指令寄存器工作是否正常;内部的边界扫描寄存器工作是否正常。在这项测试中,首先,通过读取待测板上JTAG芯片的取器件标志指令和用户编码指令来判断芯片的贴装正确与否。其次,通过对TDI输入一串测试向量,在TDO处读取响应来确定扫描链路的长度,并与JTAG器件的边界扫描描述语言(Boundary-Scan Description Language,BSDL)文件中定义的链路长度比对,完成寄存器长度测试和读边界扫描寄存器测试。最后还要进行旁路指令寄存器、读指令寄存器的测试。

2.2 边界扫描器件的互连测试

互连测试指的是对JTAG器件之间的连接关系进行测试。测试的内容包括:器件之间的互连(开/短路),一些透明逻辑及串联在边界扫描单元网络上的电阻如上拉/下拉电阻等。边界扫描的互连测试可以方便的测试与球栅阵列结构的电路板(Ball Grid Array,BGA)封装的芯片相连的网络。

2.3 非JTAG器件的测试

非JTAG器件的测试包括随机存储器 (Random Access Memory,RAM)、闪存(FLASH Memory)等存储器测试和簇测试。存储器测试指的是对板上存储芯片与JTAG器件之间的连接关系进行测试。通常的存储器测试方法包括:存储器直接存取、存储器内建自测试、宏测试。为了支持非边界扫描器件的测试,可以在测试的时候提出两种方案:1)构建JTAG软核,植入待测芯片;2)借助边界扫描器件,搭建测试外壳。总之是通过待测的非JTAG器件周围的JTAG器件提供测试通道,从而完成对非JTAG器件的测试[6]。

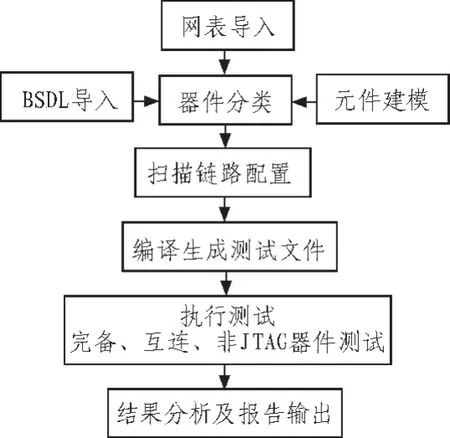

图3 板级测试流程图Fig.3 Flow chart of board-level testing

图3 说明了一个板级测试的主要步骤。首先,创建一个电路板的测试工程,把电路图的网络说明文件导入工程,连接数据库后会生成一个器件列表。列表中根据器件的类型和器件是否在扫描链路上分成了4种类型。有些器件的模型会在边界扫描系统自带的库中找到,没有的器件可以根据器件的手册手动建立模型;JTAG器件可以导入相应的BSDL语言;简单的器件例如电阻、电容等可以统一归类。其次,对器件的模型分类结果进行编译分析,编译通过后就可以进行完备性、互连性及非JTAG器件的测试了。最后,对测试结果进行分析并输出测试报告。

3 边界扫描测试实现

所有的测试过程都是在德国Goepel公司的JULET/Scan Flex硬件平台和CASCON软件平台上完成的。待测板为一块含有JTAG芯片、存储器和部分逻辑器件的开发板,具有测试的通用性。

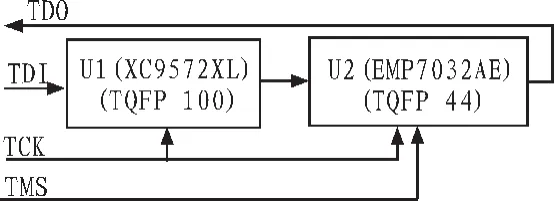

待测板可测性分析:如图4所示待测板有两个JTAG芯片:U1和U2。U1为赛灵斯(Xilinx)公司的XC9572XL芯片,U2为Altera公司的EPM7032AE芯片。

图4 待测板的JTAG链路结构Fig.4 Structure diagram of JTAGlink on the board to be tested

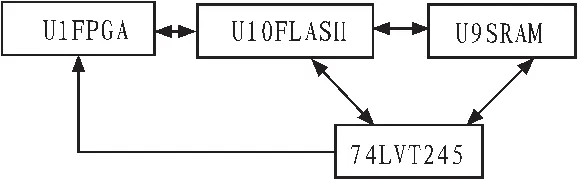

待测板上有两块存储器:U9和U10。U9是SRAM,U10是FLASH。U9通过U10与U1相连。U10的所有数据端D0-D7通过缓冲器U8(74LVT245)连接到U1,地址端的ADR0-ADR14直接连到U1。控制端的OE_F、WE_F都直接与JTAG器件U1相连。而另一控制端CE_F也通过缓冲器U11(74LVC138)转接后与U1相连。存储器的连接如图5所示。

图5 存储器之间的连接图Fig.5 Connection diagram of Memory

下面是通过实际的工程进行测试,而总结的步骤以及测试结果。

1)建立测试工程,测试准备。导入U1和U2相应的BSDL语言,其它器件从库中查找,部分未知器件手动进行仿真建模。

2)扫描链路配置。对器件进行分类处理后,边界扫描系统识别出JTAG链路,软件扫描出待测板只有一条链路。因为U2是最靠近TDO的,固其测试响应最先被检测。

3)JTAG器件之间的完备性测试。主要测试,JTAG器件之间的连接,器件的取器件标志指令。

4)JTAG芯片之间的互连测试。 互连测试没有通过,提示U1的64号管脚没有上拉电阻,

5)存储器测试。测试步骤如下:①执行外测试指令并进入数据寄存器移位状态,测试向量从U1的TDI输入,通过扫描链路将串行加载到U1的边界扫描单元中;②进入数据锁存器刷新状态,将U1边界扫描单元中的数据锁存到输出管脚上,并通过U1、U10之间的相连网络加载到U10的输入端;③执行采样指令并进入捕获数据寄存器状态,U1捕捉U10输出管脚的数据到相应的边界扫描单元;④进入数据寄存器移位状态,U10的测试响应数据从U1的TDO端串行输出。测试结果显示,RAM和FLASH测试都是通过的。

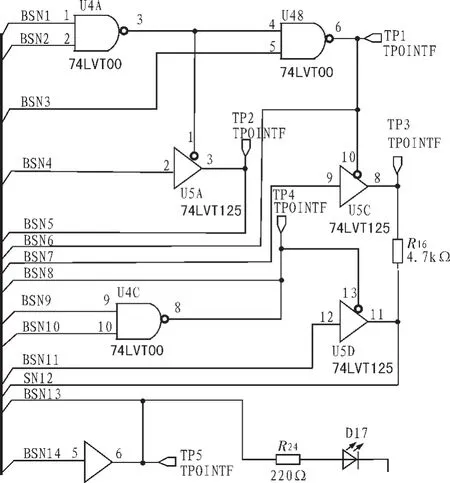

6)二次开发簇测试。虽然在完成完备性测试、互连测试和存储器测试之后基本可以覆盖待测板大部分网络,但是为了进一步提高测试的覆盖率,需要尽可能的把板上所有边界扫描单元能够驱动的网络都测试到,为此我们开发了诸如簇测试之类的测试[7]。以U4为例,其内部逻辑结构和连接关系如图 6所示,输入端由 U2的 BSN1、BSN2、BSN3控制,输出端反馈到U2的BSN6。等效于借助U2的4个BSC为U4构建了一个JTAG架构。需要注意的是,进行簇测试的器件必须是所有使用的输入输出管脚均与JTAG器件相连,否则将无法完整的发送和接收测试向量。

图6 待测部分内部逻辑结构和连接关系图Fig.6 Portion of the internal logic structure and connection diagram

一个可测性设计较好的待测板,在边界扫描的测试中能完成绝大部分网络的覆盖,而剩下的部分未测网络则可以通过诸如飞针测试、针床测试等加以补充。这样对一个电路板的测试可以达到较好的测试覆盖率。

4 提高板级测试覆盖率

一个电路板的测试覆盖率的高低在很大程度上决定于电路板的可测性设计和电路板的复杂程度。然而这两个方面又是相互矛盾的。增加电路板的可测性,势必会增加电路板设计的复杂度。为了达到最优的效果,应该权衡设计复杂最小化问题和可测性改善最大化的问题。

根据目前电路板测试的技术水平 现提出如下方法:

1)改进测试算法,进一步压缩内建自测试中额外的电路和管脚。

2)在考虑可测性设计的的时候,调整硬件电路的设计结构,使其适合内建自测试复杂的测试向量激励和压缩。

3)实现多种测试方法的综合。例如可以将在线测试仪平台和边界扫描测试平台结合在一起。可在测试开始时,首先调用在线测试仪测试程序,通过飞针完成待测板基础性项目测试,而后调用边界扫描测试程序完成板上大部分器件的测试,最后再回到在线测试仪测试平台,对边界扫描未能覆盖到的网络补测,达到覆盖率的最大化。

5 结 论

在当今电路板板生产和制造工艺飞速发展的阶段,电路板的复杂程度也越来越高,这给电路的线路检测、线路板故障检查以及排列球栅阵列结构的电路板封装芯片焊点的好坏带来了麻烦,边界扫描技术解决了这些问题。边界扫描技术已成为了超大规模集成电路的主流测试技术。

[1]Collins.Pete.Extensions to the IEEE 1149.1 Boundary-Scan Standard[S].EDN.2005,9(18):81.

[2]陈光禹,潘中良.可测性设计技术[M].北京:电子工业出版社,1997.

[3]罗涛,林明,邱卫东.边界扫描结构的设计及仿真[J].科学技术与工程,2011,11(2):261-265.LUOTao,LINMing,QIUWei-dong.Thedesign and stimulation of boundary scan’s structure[J].Science Technology and Engineerling,2011,11(2):261-265.

[4]Quiros-Olozabal A,Cifredo-CHacon M A.A new algorithm for the selection of control cells in boundary-scan interconnect test[J].Journal of Electronic Testing,2009,25(2):75-78.

[5]雷绍充,邵志标,梁峰.超大规模集成电路测试[M].北京:电子工业出版社,2008.

[6]陈亮,胡善伟.边界扫描技术及其应用[J].航空计算技术,2009,39(1):128-137.CHEN Liang,HU Shan-wei.The technology and application of boundary scan[J].Aeronautical Computing Technology,2009,39(1):128-137.

[7]雷加,李延平.数模混合边界扫描技术的研究现状与发展[J].计算机测量与控制,2010,18(4):734-737.LEI Jia,LI Yan-ping.Present dituation and development of mixed-siganl boundary scan tec-hnology [J].Conputer Measurement&Control,2010,18(4):734-737.