关于计算机组成原理实验课安排的研讨

2012-02-15时海亮田保慧

时海亮,田保慧

(1.郑州轻工业学院 河南 郑州 450002;2.河南交通职业技术学院 河南 郑州 450005)

《计算机组成原理》是计算机科学与技术专业的主干课程,自2008年起列为硕士研究生入学专业课综合考试全国统一命题重点课程[1],全国各高校对该课程都十分重视。计算机组成原理涉及的知识面宽、跨度大、概念抽象,从而对相应的实践教学提出了很高的要求。

1 传统实验方式分析

传统的计算机组成原理实验大多是在组成原理实验箱上进行,如COP2000实验箱、Dais-CMH+实验箱等。这类实验需要使用众多电子芯片,器件之间的连线较多,容易出错,对于初学者来说查错也比较困难[2],费时费力,影响实验目的的实现,影响教学效果。另外,在实验之前,需要先学习实验箱的相关配置,无异于开设一门新的课程,比较耗时,增加学生的工作量。更重要的是,实验在很大程度上受实验箱的限制,只能做固定的几个实验,修改和扩展都有相当难度,不利于调动学生的自主创新意识。另外,还有现实的问题,购置实验箱的成本比较高,一些大中专院校无力承担这些项目,同时也受场地、空间的限制。

近年来迅速发展的电子设计自动化(EDA)技术,将计算机技术应用于电子设计过程,被广泛应用于电子电路设计、仿真、集成电路版的设计以及可编程器件的编程等各项工作中。各高校也逐渐将EDA技术引入计算机组成原理实验教学中[3-4]。学生先掌握VHDL硬件描述语言,然后利用FPGA厂商提供的软件设计和综合工具进行计算机部件的设计、仿真和调试,完成各组成部件的设计任务。将EDA仿真引入到组成原理实验中,可丰富实验内容,提高实验效率,也可使学生接触到现代电子设计的新方法、新手段。但也存在一定的问题,实验中要使用的EDA环境和VHDL系统庞大、内容繁多,学习本身就相当于开设一门新课程。为了完成计算机组成原理实验,要学习一门新的课程,这无疑代价挺大,凭空增加学生的学习负担。当然,也可有这样一种折中方案,对学生增加一门新的选修课来鼓励学生先行学习这些基础知识。但在学习EDA和VHDL的过程中又会产生如何应用这些知识的问题。当然还可能牵扯学期的安排、与组成原理配合讲述等问题。

所以,在此,笔者提倡使用一种新的方式,既类似于EDA的积木式设计,又无关VHDL,利用Simulink模拟仿真的形式进行实验,使学生着重于对计算机的组成原理的理解。

2 基于Simulink的实验方式

Simulink是Matlab的重要分支产品,是一个结合了框图界面和交互仿真能力的系统级设计和仿真工具。它以Matlab的核心数学、图形和语言为基础,可以让用户毫不费力的完成算法开发、仿真及模型验证的全过程,而不需传递数据、重写代码或改变软件环境[5]。

下面以计算机组成原理课程中的加法器为例来说明利用Simulink进行仿真实验的过程。加法器是算术逻辑运算部件的基本单元,因为在两个二进制数据进行算术运算时,无论进行的是加、减、乘、除中的何种运算,最后都将化作若干步相加运算进行。

1)半加器

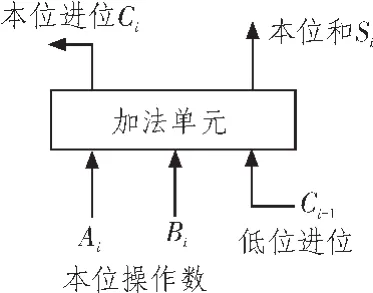

图1为1位二进制加法单元示意图,它有3个输入量:操作数Ai、Bi以及低位传来的进位信号Ci-1,有2个输出量:本位和Si和向高位传送的进位信号Ci。加法器有半加器和全加器之分。

图1 1位加法单元示意图Fig.1 Diagram of 1 bit addition unit

半加器是不考虑进位的加法单元,其本质是进行异或运算。利用Simulink仿真半加器的过程如下:

①打开Matlab,在其命令行方式下输入“simulink”启动Simulink。在菜单栏中选择“File/New/Model”新建一仿真模型。

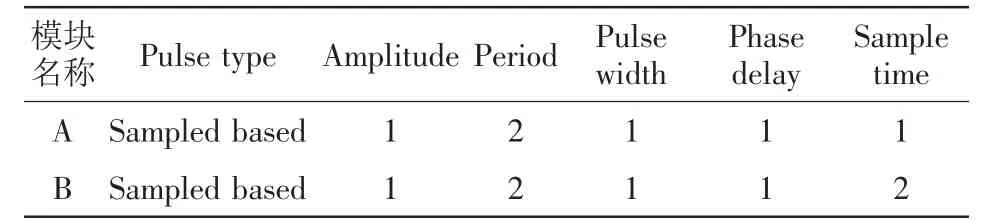

②在所启动的 “Simulink Library Browser”窗口中选择“Pulse Generator”模块作为输入信号A和B,参数设置如表所示,选择“Logical Operator”模块作为半加器,将其“Operator”改为“XOR”,选择“Scope”模块查看输出信号,将其“Number of input ports”属性设置为“3”。将各模块用信号线连接起来,如图2所示。

图2 半加器Fig.2 1 bit half adder

③保存并进行仿真,双击“Scope”模块即可看到结果,如图3所示。

2)全加器

表1 “Pulse Generator”模块参数设置Tab.1 Arguments of“Pulse Generator” model

图3 半加器实验结果Fig.3 Result of 1 bit half adder

全加器[6]是考虑进位的加法器。1位全加器的模型如图4所示(图中用D表示向高位传递的进位,下同),为节省篇幅,略去模型建立过程,其实验结果如图5所示。

图4 1位全加器Fig.4 1 bit full adder

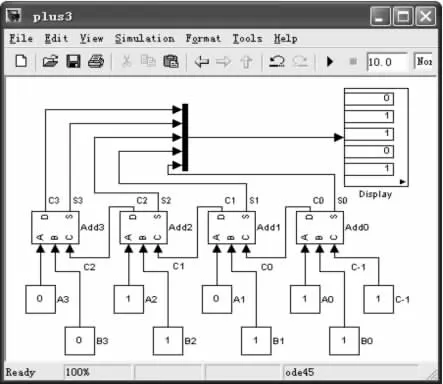

3)并行加法器

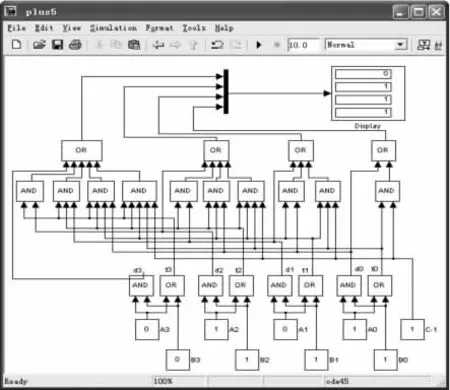

并行加法器[6]由若干个全加器组成。图6所示为由4个全加器组成的4位并行加法器,该加法器采用逐级传递进位的结构(“ADD”模块为由图4所示的1位全加器创建并封装而成的子系统),每个全加器的进位输出是高一位全加器的进位输入。为方便检验实验结果,两个4位加数分别设为“0101”和“0111”,低位进位为“1”,故结果应为“01101”。 从图中右上角的“Display”模块可以看到,结果正为“01101”。

图5 1位全加器实验结果Fig.5 Result of 1 bit full adder

图6 4位并行加法器Fig.6 4 bit parallel adder

4)串行进位链

串行进位链[6]是指并行加法器中的进位信号采用串行传递,图7所示为一个典型的串行进位的4位并行加法器。

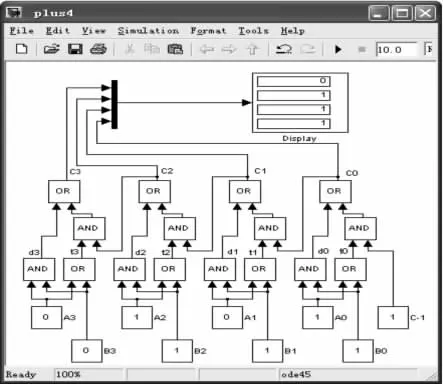

5)并行进位链

并行进位链[6]是指并行加法器中的进位信号是同时产生的,又称先行进位。图8所示为一个典型的并行进位的4位并行加法器。

3 结 论

文中首先分析了传统计算机组成原理实验的不足,提出利用Simulink仿真来模拟进行实验的思路,并以加法器为例说明利用Simulink进行仿真实验的过程。通过这种实验思路,可使学生仅利用少量的新知识便能进行组成原理的相关实验,避免产生类似于组成原理实验箱或Quartus II等EDA软件的缺点,让学生把更多的精力放在对组成原理实验的理解和学习上。同时,近几年的教学经历也充分说明该实验思路是行之有效的。

图7 串行进位链Fig.7 Ripple carry chain

图8 并行进位链Fig.8 Parallel carry chain

[1]戚梅,张鹏.多媒体技术在《计算机组成原理》实验教学中的应用[J].现代计算机,2007(Z1):96-98.QI Mei,ZHANG Peng.Application of multimedia technology in the experiment teaching of computer principles[J].Modern Computer,2007(Z1):96-98.

[2]朴希南.基于EDA技术的计算机组成原理虚拟实验[J].电脑知识与技术,2011,7(7):1707-1709.PIAO Xi-nan.Principles of computer organization virtual experiment based on EDA technology [J].Computer Knowledge and Technology, 2011,7(7):1707-1709.

[3]连晋平.EDA在组成原理课程教学中的应用[J].科技创新导报,2011(15):204.LIAN Jin-ping.Application of EDA in computer principle teaching[J].Science and Technology Innovation Herald,2011(15):204

[4]董再秀,温卫敏,赵亮.计算机组成原理课程教学改革与实践[J].滁州学院学报,2011,13(2):94-96.DONG Zai-xiu,WEN Wei-min,ZHAO Liang.The reforms in teaching of the course computer composition principle[J].Journal of Chuzhou University, 2011,13(2):94-96.

[5]钟麟,王峰.Matlab仿真技术与应用教程[M].北京:国防工业出版社,2004.

[6]唐朔飞.计算机组成原理[M].北京:高等教育出版社,2008.