一种高速低功耗LVDS接收器电路的设计

2012-01-19孙金中谢凤英

孙金中,谢凤英

(中国电子科技集团公司第38研究所集成电路设计中心,安徽合肥 230031)

一种高速低功耗LVDS接收器电路的设计

孙金中,谢凤英

(中国电子科技集团公司第38研究所集成电路设计中心,安徽合肥 230031)

介绍了LVDS系统链路结构及数据传输原理,分析了LVDS标准对接收器电路的需求,文中基于65 nm数字CMOS工艺设计,实现了一种高速低功耗LVDS接收器电路。仿真结果表明,在2.5 V电源电压工作下,该LVDS接收器具有2 Gbit·s-1的数据传输速率,平均功耗为3 mW。

低压差分信号(LVDS);接收器;差分信号;高速

随着高清多媒体处理器、高性能数字信号处理器和网络终端技术的发展,数据传输速率的要求越来越高。集成电路工艺的快速发展使得芯片内部千兆比特每秒数据传输速率成为可能,然而芯片与芯片之间、不同系统终端之间的传统接口电路,成为制约整个系统数据传输速率提高的障碍。

低电压摆幅差分信号(Low Voltage Differential Signal,LVDS)接口,是20世纪90年代提出的一种高速数据传输和接口技术,由美国国家半导体公司率先提出,并于1996年通过为IEEE标准[1]。其核心是采用低电压摆幅高速差分地传输数据,LVDS技术可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。目前LVDS接口电路广泛集成在高速ADC、DSP等芯片内部解决高速数据传输的接口问题[2-4]。

1 LVDS系统链路原理及接收器电路分析

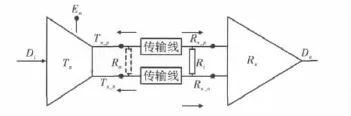

LVDS传输系统原理如图1所示,发送器将输入的CMOS电平的数字信号转换成差分LVDS信号进行通信传输,差分信号通过传输线到达接收器电路,接收器电路将差分LVDS信号转换成CMOS信号供后续数字处理电路处理。在信号传输线的输入和输出端,考虑到高频信号的反射需要阻抗匹配电阻。在LVDS系统中,信号差分驱动输出,在接收端连接一个100 Ω的电路以匹配传输线上单端阻抗 50 Ω[5-6]。

图1 LVDS传输系统原理图

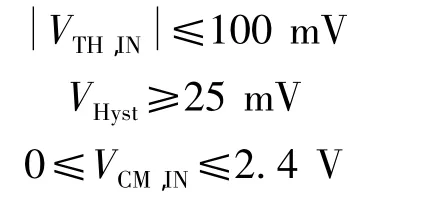

由于发送器和接收器系统间通常距离较远,互连线电阻会引入共模电平变化;而且LVDS为全差分传输,噪声通常以共模噪声的形式耦合到传输线上,为提高噪声容限,IEEE Std.1596.3-1996(LVDS)标准对接收器输入共模电平的变化允许1 V。同时,为了消除输入信号的不确定性,接收器的输入要求有约25 mV的迟滞。因此接收器电路一般包括一个宽共模范围的前置放大器和迟滞比较器[7-8]。根据模拟集成电路设计规则,接收器需要在各种PVT条件下满足LVDS标准对接收电压阈值VTH,IN、输入差分迟滞电压VHyst和输入共模电平VCM,IN的规定如下

2 接收器电路设计

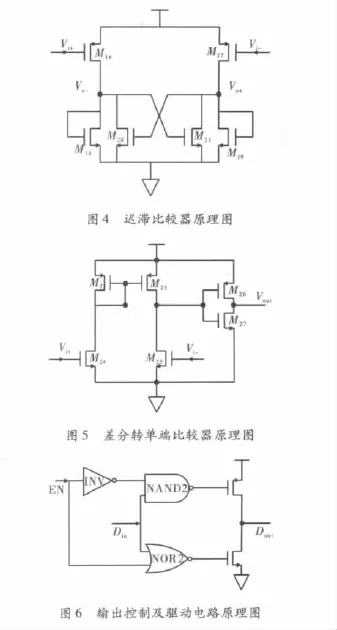

新型低功耗接收器电路原理如图2所示。该接收器电路有Rail-rail前置放大器、迟滞比较器、差分转单端比较器和逻辑控制及驱动电路组成。其中Railrail前置放大器的原理如图3所示,该前置放大器由Rail-rail输入差分对构成的折叠式运算放大器组成;Rail-rail输入差分对保证了宽共模范围的输入,折叠式共源共栅输出阶电路保证了增益需求的同时具有较宽的输入信号带宽,满足高速信号传输的要求;输入差分对的微电流源以及负载电流源偏置由输出共模电压提供,既降低了功耗又简化了偏置电路。迟滞比较器的原理如图4所示,该迟滞比较器由伪差分输入对和二极管负载以及负阻二极管构成。差分输入迟滞电压由二极管负载管M18和负阻二极管M20的尺寸决定。

差分转单端比较器原理如图5所示,该比较器由伪差分输入对和电流镜像负载构成,同时增加了反相器驱动。逻辑控制和输出驱动电路原理如图6所示,当输出控制逻辑EN为高电平时,输出驱动管均关断,输出节点为高阻输出模式;当输出控制逻辑EN为低电平时,输出信号随输入信号的改变而变化。

3 接收器电路版图设计及仿真

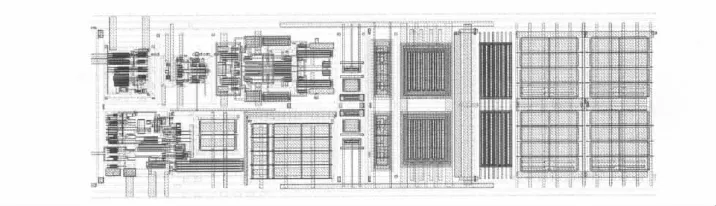

接收器电路采用65 nm CMOS 1P9M Logic工艺进行版图设计,如图7所示,版图大小190 μm ×60 μm,从右到左依次为去耦合电容、ESD二极管、接收器电路等。接收器电路版图主要考虑输入差分对管的匹配、差分信号线的对称走线以及屏蔽等。

图7 接收器电路的版图

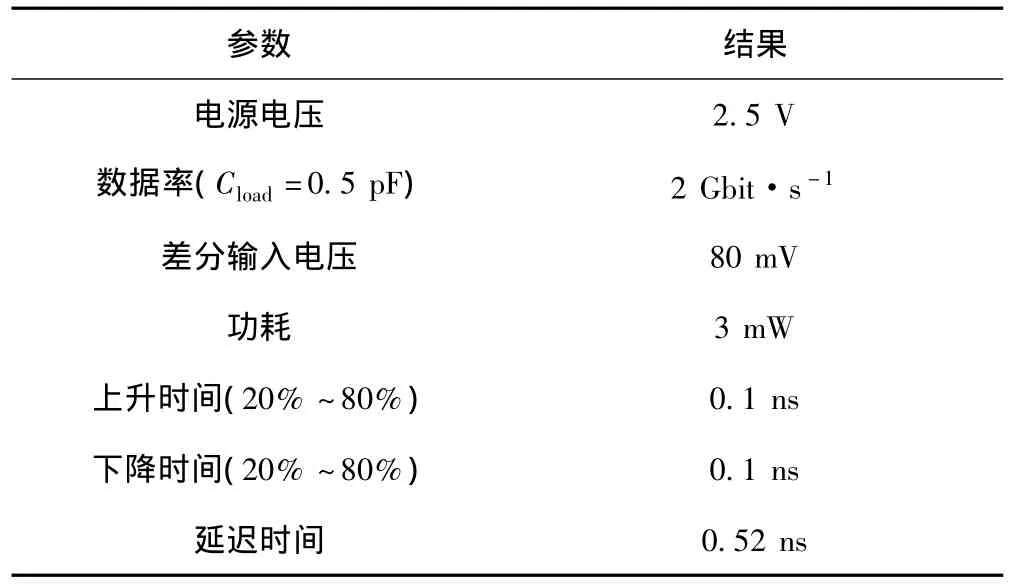

接收器电路的仿真结果如图8所示,图中给出了输入共模电平分别为0 V、1.2 V、2.4 V;差分脉冲电压差80 mV;脉冲信号频率1 GHz。可见,接收器电路在输入共模范围0 ~2.4 V内均可稳定工作在2 Gbit·s-1。接收器电路的具体技术指标概要如表1所示。

图8 输入输出信号的眼图仿真结果

表1 LVDS接收器性能概要

4 结束语

提出了一种符合IEEE Std 1596.3-1996标准的新型低功耗LVDS接收器电路。通过采用Rail-rail前置放大器实现了LVDS接收器电路的共模电平0~2.4 V的要求,通过自偏置折叠放大器、伪差分对等技术有效降低了电路功耗,在2.5 V电源电压,数据传输速率为2 Gbit·s-1下平均功耗仅为3 mW。该LVDS接收器电路可广泛应用于高速低功耗的芯片间数据传输系统。

[1]BOZOMITU R G,CEHAN V,BARABASA C.A VLSI implementation of a 3Gb/s LVDS Transceiver in CMOS Technology[C].UK:2009 15thSIITME,2009.

[2]陈莹,高双成.基于FPGA的LVDS借口应用[J].电子科技,2012,25(1):8 -12.

[3]XU Jian,WANG Zhigong,NIU Xiaokang.Design of high speed LVDS transceiver ICs[J].Journal of Semiconductors,2010,31(7):151 -159.

[4]吴杰.LVDS信号的PCB设计和仿真分析[J].电子科技,2012,25(4):71 -73.

[5]Microprocessor and Microcomputer Standards committee of the IEEE Computer Society.IEEE Standard for Low -Voltage Differential Signals(LVDS)for Scalable Coherent Interface(SCI),1596.3 SCI- LVDS Standard,IEEE Std.1596.3 -1996[S].New York:IEEE StandardsBoard,1994.

[6]宣栋,刘心惟.基于FPGA的LVDS高速数据通信卡设计[J].电子科技,2012,25(2):54 -56.

[7]HUANG Xingfa,LI Liang,XU Kaikai.An 0.35um CMOS 2.4 Gb/s LVDS for high - speed DAC [C].Sydney:2009 IEEE 8thInternational conference on ASIC,2009.

[8]LIN Yingyan,KANG Wenjing,CHEN Xiaofei.A Novel 1.2 Gbit·s-1LVDS Receiver for multi- channel applications[C].CA USA:2009 Proceedings of the 2009 12th international Symposium on Integrated Circuits,2009.

[9]薛隆全,文丰,张时华.基于LVDS总线的高速长距数据传输的设计[J].电子设计工程,2009(2):45 -46,48.

[10]李伟,林志贤,郭太良.LVDS技术在彩色FED中的应用[J].现代电子技术,2007(19):194 -196,200.

A High Speed Low Power LVDS Receiver Design

SUN Jinzhong,XIE Fengying

(IC Design Center,China Electronic Technology Group Corporation No.38 Research Institute,Hefei 230031,China)

LVDS system link structure and data transmission principle,LVDS standard receiver circuit,based on 65 nm digital CMOS process design to achieve a high-speed low-power LVDS receiver circuit.The simulation results show that the supply voltage of 2.5 V,the LVDS receiver with 2 Gbit·s-1data transfer rate,average power consumption is 3 mW.

low-voltage differential signaling;receiver;differential signal;high speed

TN432

A

1007-7820(2012)06-095-03

2012-05-10

孙金中(1983—),男,博士研究生,工程师。研究方向:模拟集成电路设计。谢凤英(1978—),女,工程师。研究方向:模拟集成电路设计。