多核系统中NoC通讯架构的关键技术

2012-01-19赵忠惠王少轩陈亚宁

汪 健,张 磊,赵忠惠,王少轩,陈亚宁

(中国兵器工业第214研究所苏州研发中心,江苏苏州 215163)

多核系统中NoC通讯架构的关键技术

汪 健,张 磊,赵忠惠,王少轩,陈亚宁

(中国兵器工业第214研究所苏州研发中心,江苏苏州 215163)

多核处理器已经成为处理器的主流,并发展成为各种通信与媒体应用的主流处理平台。通讯结构是多核系统中的核心技术之一,核间通信的效率是影响多核处理器性能的重要指标。目前有3种主要的通讯架构:总线系统结构、交叉开关网络和片上网络。总线结构设计相对方便、硬件消耗较少、成本较低;交叉开关是适合用于构建大容量系统的交换网络结构;而片上网络是更高层次、更大规模的片上网络系统,目前可以解决多核体系结构问题,是多核系统最有前途的解决方案之一。文中在分析了NoC结构的基本原理、系统结构和功能的同时,也提供了部分单元的设计实现。

多核处理器;核间通信;总线结构;交叉开关;片上网络

在处理器的发展中,提高处理器主频的实现愈加困难,市场上难以看到芯片主频率高于4 GHz的传统单处理器[1]。以Intel、AMD公司为代表,依靠不断提高处理器频率提升系统性能的时代即将成为过去。究其原因有3点:首先仅依靠提升主频难以大幅度提升CPU的性能,从而减缓了消费者对高频CPU的热衷;其次当CPU主频达到2 GHz以上时,处理器功耗也达到了近100 W,这是目前风冷散热技术的极限;第三,在嵌入式产品领域,传统的单核处理器结构,不能满足呈几何级数增长的计算规模的需求[2-3]。单核模式下,利用局部性能提升整体性能的发展越来越慢,而基于多核的线程级并行技术却为性能提高提供了动力,为达到更高的处理效能,多核处理器体系结构应运而生。

多核处理器是一个芯片内含有两个或两个以上的“执行内核”。多核处理器在进行体系结构的技术研究时,比单核处理器,要面临更多的挑战,诸如核间通讯、存储器体系、低功耗、软硬件协调等[4]。如何实现多核内核之间相互协作和通信,确保提高处理速度、提高芯片处理器性能,是核间通讯结构研究的主要内容。在多核通讯方式中,目前除继续沿用单核SoC中的总线结构,如 AMBA,CoreConnect,Wishbone,OCP,C*BUS等,主要有交叉开关(Crossbar Switch)、片上网络(NoC,Network on -Chip)等结构[5-6]。其中 NoC 结构是更高层次、更大规模的片上网络系统,目前可以解决多核体系结构问题,是多核系统有效的解决方案之一。

1 NoC解决的问题及其优点

随着工艺的进步,产品的性能、面积、功耗以及上市时间的限制,使设计开发的要求越来越高。深亚微米设计带来的问题,使得设计中保证时序收敛更加困难。NoC(Network on-Chip)的出现为深亚微米的SoC带来了持续发展的动力。NoC是更高层次、更大规模的片上系统,是片上的网络系统。NoC技术的核心思想是将计算机网络技术移植到芯片设计中,解决多CPU的体系结构问题。由于网络结构本质就是多CPU系统,因此基于网络的体系结构是多CPU系统最有前途的解决方案之一。片上网络继承了分布式系统与计算机网络的概念,互连结构具有各通信模块之间并行通信,数据的通信带宽高,扩展性好,吞吐量大,并可以在一定程度上改善深/超深亚微米条件下信号传输线延迟等优点,有人称NoC会成为下一代多核的主流互连结构。

1.1 NoC解决的问题

NoC解决的问题主要体现在通讯模块的可重用性和通讯性能的可预测性上。

(1)增加通讯模块的可重用性。一般SoC概念中,可重用性是IP模块的复用。基于模块的设计方法,能够增强设计的可重用性,进而减小制造工艺同设计能力之间的差距。可重用技术的优越性在于以基于模块的设计,搭建整个系统,减少单独开发每个部件的设计时间,同时减少人为设计的出错可能,因此降低了系统的设计和验证时间。但是当制造工艺发展到0.13 μm以下后,模块间的互连延迟成为限制系统整体性能的瓶颈,仅靠IP模块的复用已远不能满足整体性能的需求,片上网络结构正是利用通信部件的可重用技术,将不同资源单元之间的路由连接通过规则的通信部件进行连接,为深亚微米技术带来的问题提供解决方案。

(2)加强通讯性能的可预测性。片上网络因其规则的物理布局和通信网络结构,通信性能变得可预测。从物理性能的角度分析,片上网络结构决定了其版图物理性能的可预测性。除时钟、电源布线外,交换单元间的互连长度以及带宽都是固定不变的,而设计的不确定性和不规则性都限制在资源单元内部,对于其他资源单元没有造成影响;从设计和验证时间角度分析,片上网络基于模块的可重用性使得设计和验证的时间都可预测,由于片上网络结构的规则性,将任务分配等设计问题划分到了资源单元内部,进而将整体应用划分为独立任务。这样使得片上网络系统的设计在较大程度上独立于具体的实现阶段,更好地进行模块化设计,增加了通讯性能的可预测性。

1.2 NoC的优点

NoC设计采用全局异步局部同步的方式解决了整个芯片全局同步面临的问题,有较好的可重用性和可扩展性,平均通信带宽较高。在NoC中,处理核与网络的通讯是通过简单的握手协议来完成的,因此网络与各处理器的电气参数、时钟信号都可以相对独立处理,容易控制。此外网络与处理器间也可以使用异步通讯,这就不需要系统时钟的全局同步,避免了庞大时钟树所带来的时钟和面积问题,而局部时钟线的大量采用可以大幅降低系统功耗。

NoC的各同步单元在遵守通信协议的前提下协同工作,如有NoC系统有扩展的需要,只需增加一个系统中已经存在的通信开关的副本,同时设计一个通信接口,把扩展的功能单元集成到NoC的网络拓扑中就可完成。NoC有可复用可扩展的通信机制,同时改用全局异步局部同(Global Asynchronized Local Synchronized,GALS)方式工作,没有全局的控制信号的干预,所以NoC的可扩展性好。

衡量NoC性能的主要指标就是通信带宽。NoC采用全局异步局部同步的通信方式,虽然得到了一些好处,但缺点也明显,例如实时通信带宽不能达理想高度。但从整个NoC的平均通信带宽上看,全局的平均通信带宽比基于总线方式的平均通信带宽高。总之随着工艺集成度的逐渐提高,NoC在解决全局时钟同步问题、深亚微米效应、扩展性和设计与生产之间的鸿沟上都优于传统设计方法。

2 NoC的拓扑结构

拓扑结构关心的是节点的布局和互连。NoC拓扑结构的选择对系统性能和芯片面积有明显的影响。NoC可根据应用的需要采用不同的拓扑结构,可分为规则结构、非规则结构等。相对于规则拓扑结构,不规则拓扑结构可以提高性能、降低功耗、减小面积,但同时产生版图设计、不均匀的线长等设计问题。拓扑结构的衡量标准通常是以理论上影响路由成本和性能为基础,除了要考虑普通网络中所关心的节点数量、边的数量、网络维度、网络直径、平均距离、对分宽度之外,还要考虑通信模式的嵌入属性,例如消息吞吐量、传输延迟、功耗、芯片面积等。

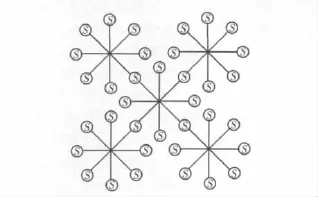

图1是简单的NoC拓扑结构,拓扑结构体现NoC中通讯节点在芯片中的分布和连接。由于系统需求、节点模块的尺寸和位置不同,需要不同类型的拓扑结构,有很多种可供选择的拓扑结构。良好的拓扑结构必须考虑以下因素:路由节点与处理器节点或者路由节点之间的通信带有明显的局部性特征;NoC中资源节点的物理尺寸与通讯节点的物理尺寸相互影响;NoC使用物理连线作为通信信道,因此节点之间的连接不能太复杂,且要具有易扩展性。

图1 简单的NoC拓扑结构

片上网络结构常用的为直接型结构,即网络中每个节点与相邻节点之间以点对点方式或直接互联的方式连接,如网格(Mesh)结构,Mesh结构是规则的NoC拓扑结构,具备硬件实现简单、网络扩展性好等优点,因此做为NoC以最为常用拓扑结构。包括了规则的Mesh结构、不规则的Mesh结构、多层Mesh结构、稀疏的Mesh结构,二维环状Mesh结构,还有胖树结构、八角形网络等。图2所示为采用二维网格结构的片上网络,这是较常用的系统结构。该二维网格结构由资源单元和网络结构构成,其中网络结构包括交换单元、通信通道和资源与网络的接口,资源单元由嵌入式系统或者存储器系统构成。图中S表示交换单元,P与C分别表示处理器单元与缓冲存储器,D表示DSP单元,re表示可配置单元,如FPGA单元。mi表示资源与网络的接口,M表示存储单元。图中每一个方形区域(Region)用于映射不同结构的系统,例如处理器子系统和存储器子系统合成的区域,区域的规模可以大于一般的资源单元,但区域与片上网络其他部分的互连需要通过交换单元进行。

图2 二维网格结构

法国Pierre et Marie Curie大学的Pierre Guerrier等人在2000年提出了称为胖树(Fat-tree)结构的网络结构,如图3所示。r是通讯节点,p是资源节点,其在设计一种可升级、可编程的集成网络时采用了这种结构。与二维网状网络相比,胖树结构中树的深度决定了点对点的延迟,两个资源结点间的通讯最多需要经过3个通讯结点。

图3 胖树互连网络结构

与此同时,F.Karim等人在设计网络处理器时提出了八角形网络结构,如图4所示。类似于胖树网络,该网络中两个资源结点间的点对点的延迟取决于源点与终点的相对位置。任意两个资源结点间的通讯最多需要通过两个内部连线。

图4 八角形互连网络结构

3 NoC的通讯协议

NoC是片上通信基础结构,借鉴网络中的分层思想,NoC设计采用普通的通信分层方法,定义5个协议层:物理层、数据链路层、网络层、传输层和系统层。图5是NoC一个典型的层次结构。

图5 NoC的通讯协议

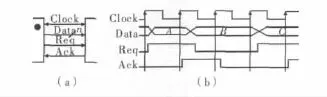

(1)物理层。物理层实现连接处理器资源与网络的链路宽度和链路方向,因此带宽负载能力、数据包大小及在两节点之间的传输延迟等物理信息都是检验物理层设计质量的评估标准。片上网络的物理层通讯采用握手协议完成,而握手协议可以分为同步协议与异步协议两种。图6为同步握手协议的示意图,图6(a)为物理通道信号。与计算机网络多采用串行通讯方式不同,由于片上连线资源丰富,NoC可以使用并行通讯方式。因此同步方式和异步方式的Data信号宽度n,为>1的整数。握手协议需要请求信号Req和应答信号Ack完成通讯双方握手操作,除此以外,同步方式需要时钟信号Clock同步其余信号。

图6 同步握手协议示意图

(2)数据链路层。数据链路层的功能就是将信息的每一个字准确地从一个节点传输到相邻的节点上,定义了资源节点、通讯节点以及两个通讯节点之间的传输协议,保证物理连接之间可靠的信息传输。由于两个相邻的节点可能以异步传输模式工作,因此需要考虑数据的出错检测与纠错外,数据链路层还需要注意硬件同步问题,同时实现数据编码和更好地控制数据传输率以及功耗管理。物理层和数据链路层均与工艺有关,即如采用新工艺,必须重新定义这两个层。

报文格式的定义如图7所示。报文由若干个帧组成。帧可分为头帧、尾帧和实体帧3类。所有3类帧的组成相同,如图8所示,均由头标识位,尾标识位和帧负载位组成。

(3)网络层。负责建立互连链接以及路由策略,因此片上网络中各传输路径的利用情况,在较大程度上取决于网络层的设计结果。不同的链接建立方式在不同的网络拓扑结构中性能各不相同,因此针对不同的应用和片上网络结构,需要制定相应的链接建立方式。

(4)传输层。负责监视网络流量、对数据包进行拆分及组装,因此数据包发送速度、掉包率以及解决方案是衡量传输层设计质量的标准。另外传输层对网络传输路径上的流量控制,直接影响到数据传输的吞吐量,这也是衡量传输层性能的指标。

(5)系统层。该层的重要功能包括信息的同步和管理、接收端数据格式的转换以及一些与应用相关的功能等。

4 路由算法

路由策略的研究是NoC中的一个重要内容,在给定的网络拓扑结构下,决定数据包在网络中的投递路径。其目的是使数据包的网络延时、数据吞吐率、数据包投递所需的功耗和可靠性都达到指标。

NoC路由算法的分类:依照路由结果的计算位置、路径选择方式、路径距离等方法,由算法决定数据包在网络结构中传输的方向,把传输路径集合限制为合理的路径子集。如果消息的路由完全由它的源和目的地址决定,与网络中其他流量无关,这种路由算法称为确定性路由,对于每一个源节点和目的节点之间,采用确定性路由得到一条路径计算结果。而自适应路由算法是允许路径上的其它流量影响数据包的路由策略,对于每一对源和目的节点,算法可根据网络的拥堵状况给出多条的路径计算结果。路由计算模块是一个相对独立的处理单元,通常需要根据不同的算法改变交换节点中的路由计算模块,就可以实现NoC路由算法的改变。

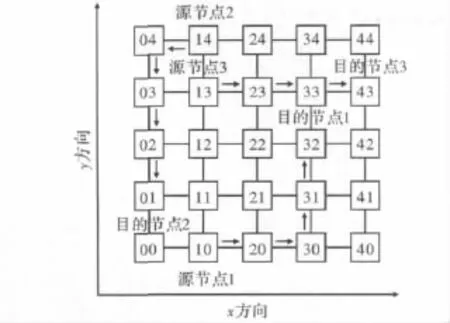

维序路由采用较为广泛的路由算法,应用了确定性路由的方法,数据包无论其路径上的链路是否阻塞都要沿该路径走下去。该算法的思想是数据包先在低维上投递,直至数据包在该维度上相对于目的节点的偏移量为0,然后转移到下一维度以相同的模式进行投递,直到达到目的节点。因此维序路由是分布式路由,也是一种较小距离路由。

图6是二维Mesh网格中维序路由的一种算法,称为xy路由。表示不同源节点、目的节点下维序路由算法得出的路由路径结果以及在二维Mesh网络中,路由路径的可能转向。数据包先在x维度上投递,然后在y维度上投递,直至达到目的节点,该路由算法不会出现死锁现象。

图9 维序路由算法示意图

5 交换技术

交换技术是按照某种方式动态地分配传输线路和接口的资源,是影响网络性能,决定交换节点结构的重要技术。NoC中运用的交换技术可分为两类:面向连接的和无连接的。面向连接的交换方式主要有电路交换,无连接的方式主要有存储交换、虚切通和虫孔交换。

(1)电路交换(Circuit Switching)是一种面向连接的交换机制。在通信之前,要通过信息头按照路由规则选路,然后建立路径,同时预定所经过路径的信道资源。目的端在成功收到此信息头后将沿原路返回一个应答,源节点收到此应答后便开始传输数据。数据传输之前源节点和目的节点之间建立直接的连接路径,一旦数据开始传输,消息的传输不会阻塞。数据部分在网络中传输时将独占此路径中各段链路的整个带宽,无需做路由选择。

(2)存储交换(Store and Forward Switching)是先将数据完全存储,然后进行路由决策,最后再转发到下一节点的一种交换机制。NoC中的存储交换主要以分组为流控单元,每个分组有一个分组头,含有源、目的节点地址以及其它控制信息。路由节点接收到一个分组后,先将整个分组存储在缓存器中,从分组头中获取路由信息,由路由器的路由决策单元选择一条输出通道后,置位交叉矩阵中的内部连接,如果下一路由节点中有足够的空间存放此分组,就将此分组转发到下一路由节点。存储交换的优点是通道只在一个数据包需要传输的时候才被占用。

(3)虚切通交换(Virtual Cut-throuth Switching)将分组进一步划分为更小的片,并按顺序排好,将所需的路由信息放人第一个片中,在无阻塞的情况下,路由节点收到头片后,从中读取路由信息,然后由路由决策单元负责选路,如果输出通道空闲,则将头片转发出去,后续片紧随头片向前路由,从而在较大程度上缩小了存储交换的时延。由于在任何一个节点上都可能有多条消息被阻塞,每一个节点都要提供能存储所要通过他的数据的存储空间。所以每一个节点都需要较大的存储空间。

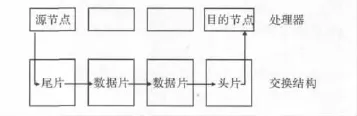

(4)虫孔交换(Wormhole Switching)是目前NoC中的主流交换机制。它和虚切通交换的思想基本相同,只是二者在发生阻塞时所表现出的行为不同。在虫孔交换中,数据包也被细分成片,以流水的方式在网络上传输,并且允许一个分组由一个片组成。头片中包含路由信息,其他数据片都跟随头片在他确定的路径上流动,就像虫子一样。当头片发生阻塞时,分组中的所有片都将停止前进,头片缓存在当前节点,数据片就地缓存在其后的若干个中间节点中。每个路由节点只需提供一个片大小的缓存资源。虫孔交换对数据包大小和路径长度不敏感,资源占用少,实现代价小,且效率高,适合NoC使用。虫孔交换的示意图如图7所示。

图10 孔虫交换原理图

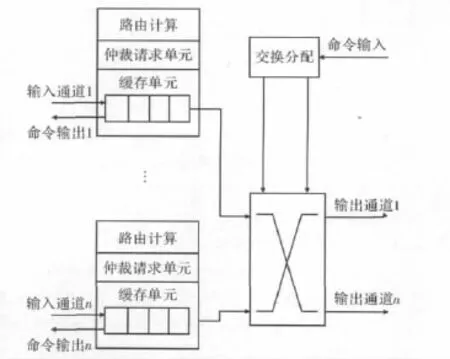

虫孔交换结构的处理过程如下:数据包的片段到达虫孔交换结构,存储在输入通道缓存单元中,并进行路由计算。得到路由信息后,数据包提出传输请求,仲裁器根据请求进行带宽资源分配,一旦该数据片被允许传输,它将被交换到目的端口并投递出去,直到数据包的最后一个片段离开交换节点。根据此处理过程,虫孔交换电路的结构如图8所示,由缓存单元、路由计算单元、仲裁请求管理单元、交换分配和交换阵列5部分组成。

图11 虫孔交换电路结构

在VLSI实现中,NoC交换节点多采用流水结构设计,一般流水处理结构分为路由计算、通道分配、交换分配、数据交换和传输等5级。在NoC设计中,总是希望得到良好的网络性能,从交换节点设计角度考虑,减少交换结构的流水处理级数是缩短网络延时的有效方法,流水处理级数越少,数据包通过交换节点的时间就越短。

不同的NoC交换技术,对应着不同的网络性能和实现代价,要根据实际要求进行选择。

6 片上网络面临的挑战

为提高片上网络的资源单元处理速度,降低通信通路间以及资源单元互连间的通信延迟,片上网络的设计面临以下几方面挑战:

(1)任务分配与调度,片上网络将通信任务分配到合适的处理单元,并且尽量以最佳方式为这些任务进行排序,此步骤是典型的多处理器系统的关键设计步骤。

(2)网络分配,包括处理单元映射与路径分配。处理单元映射对系统功耗起着决定性的影响,路径分配则是对执行性能产生直接影响。

(3)动态网络最佳化路径分配,对静态通信路径分配时,由于对即时性的要求较低,因此只要对现有的最短路径进行确认即可。但对于片上网络的动态通信而言,需要将计算机网络中的动态网络调度算法进行调整,应用到片上网络应用中。

7 结束语

NoC通讯方式是目前多核系统通讯结构中研究最为广泛的结构,也使得NoC成为当前研究热点,部分大学、研究所以及工业界的研究单位正积极从事NoC研究工作,但是NoC依然面临着许多技术挑战。在实际应用中,应根据系统的实际要求,选择合适的拓扑结构和交换技术,避免一味追求最新的技术而带来其他的问题。

[1]孙利荣,蒋泽军,王丽芳.片上网络[J].计算机工程,2005(20):1-2.

[2]闫辉.多核是软件开发行业的迁移目标[J].程序员,2006(9):47-48

[3]马关胜,冯刚.SoC设计与P核重用技术[M].北京:国防工业出版社,2006.

[4]荆元利,樊晓桠.网络互连多线程处理器[J].计算机工程与应用,2005,41(33):51 -53.

[5]欧阳.多核时代改变计算发展历史[J].程序员,2006(9):42-46.

[6]张恒龙,顾华玺,王长山.片上网络拓扑结构的研究[J].中国集成电路,2007,16(11),42 -46.

[7]刘轶,张昕,李鹤,等.一种面向多核处理器并行系统的启发式任务分配算法[J].计算机研究与发展,2009,46(6):1058-1064.

[8]KANGM L,SE J L,HOI J Y.A dis-tributed crossbar switch,switch scheduler for on -chipnetworks[C].IEEE Proceedings of Custom Integrated Circuits Conference,2003:671 -674.

[9]RAKESH K,DEAN M T,NORMAN P J.Heterogeneous chip multiprocessors[J].IEEE Computer Society Press Los Alamitos,2005,38(11):32 -38.

[10]VALDERRAMA C A,CHANGUEL A,JERRAYA A.Virtual prototyping for modular and flexible hareware-software systems[J].Design Automation for embedded systems,1997,2(3):267-282.

[11]HEMANI A,JANTSCH A,KUMAR S,et al.Network on a chip:architecture for billion transisitor era[C].In Proceeding of the IEEE Norchip Conference,2000:711-726.

Study of on-Chip Network Communication Architecture for the Multi-core Processors System

WANG Jian,ZHANG Lei,ZHAO Zhonghui,WANG Shaoxuan,CHEN Yaning

(Suzhou R & D center,214 Institute of China Weaponry Industries,Suzhou 215163,China)

In recent years,Multi-core architectures have been the mainstream design of the processors as well as the mainstream processing platform of various communication and multimedia applications.The communication structure becomes one of the core technologies of Multi-core processors.The efficiency of communication between the inter-core is the key indicator of Multi-core processor performance.There are three main types of communication architecture:Bus system,Cross-bar network and On-Chip Network.Bus structure designs have the advantages of convenience,low hardware consumption and low cost.Cross-bar design is suitable for the switching network structure of building large-capacity systems.On-Chip Network is larger and more sophysicated on-chip network,which can completely solve the problem of Multi-core architecture and therefore becomes one of the most promising solutions for the Multi-core system.The paper discusses the principle,system structure and function of the NOC communication architecture and presents the realization of some units.

multi-core processor;inter-core communication;bus;cross-bar;on-chip network

TN402

A

1007-7820(2012)06-047-06

2011-12-03

汪健(1969—),女,研究员级高级工程师。研究方向:弹载SoC及大规模数字集成电路军用集成电路。