基于FPGA的乐曲演奏电路的设计

2011-10-26施奇毛丽民张笠君陈肖帆

施奇 毛丽民 张笠君 陈肖帆

常熟理工学院电气与自动化工程学院,江苏 常熟 215500

基于FPGA的乐曲演奏电路的设计

施奇 毛丽民 张笠君 陈肖帆

常熟理工学院电气与自动化工程学院,江苏 常熟 215500

本文首先运用Visual Basic 进行上位机琴键控制界面的程序设计,再利用VHDL语言进行演奏电路的设计,并将该模块通过QUARTUS II平台下载到Altera芯片中, 上位机机通过RS232串行口可以直接与FPGA进行通信,完成数据交换工作。该演奏电路通过琴键控制界面输入音调,由RS232通信方式控制发出DO、RE、MI、FA等8个音调,蜂鸣器发出声音,完成演奏功能。

FPGA;Visual Basic;RS232通信模块

FPGA; Visual Basic; RS232 communication module

近几年在数字系统设计领域出现了一种全新的设计技术——数字系统设计自动化(EDA, Electronic Design Automation)技术。该技术具有系统设计效率高、集成度好、保密性强、易于修改、易于实现等优点,因此而成为当今数字系统设计的主流技术,其应用领域也越来越广泛,其中进行电子琴的实现也是一个重要尝试和应用,本文研究了一个基于FPGA乐曲演奏电路的设计方案,利用altera的FPGA芯片,在QuartusⅡ平台下,采用自顶而下的设计思路,结合VB的程序设计,完成乐曲演奏电路的设计。

1 系统设计

1.1 设计要求及功能

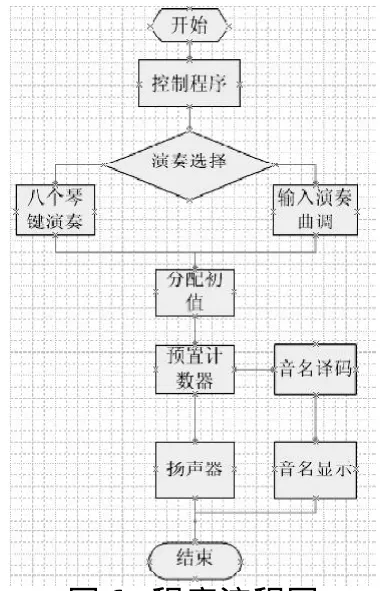

该演奏电路能实现八个音键的控制以及对于编好的音乐进行播放,根据各个音调的频率的差异,来实现按下不同的音键而发出不同的声音。当8位发声控制键输入中某一位为高电平时,则对应某一音阶的初始计数值作为获得该音阶的分频预置值将送入预制数计数器;预制数计数器输出相应的频率同时输出对应该音阶简谱的显示代码;该频率经二分频器后送入扬声器,扬声器就可发出对应音符的声音,同时在数码管上显示该音名。

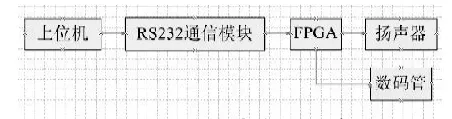

1.2 总体功能示意图

图1 系统功能示意图

2 硬件电路设计

本设计采用A ltera第一代Cyclone系列FPGA EP1C6,该器件基于全1.5V SRAM工艺,容量从2910至20060个逻辑单元具有多达294912bit 嵌入RAM Cyclone FPGA支持各种单端I/O 标准。EP1C6 有4000个逻辑单元(LE),有17个M 4K RAM 块,有两个PLL。主要电路图如下所示:

图2 蜂鸣器电路图

U 3为蜂鸣器当IO134 输出不同频率出来时,U 3 蜂鸣器会发出相应的声音。

根据HBN评分情况进行效果标准评价[3]:(1)治愈,面部症状全部消失,面神经功能完全恢复,面部运动正常;(2)显效,面部症状基本消失,存在轻微功能减弱,静止状态下面部对称,张力无异常,眼睛可完全闭合,口有轻微不对称;(3)有效,明显功能减弱,静止状态下面部对称,张力无异常,抬眉额纹对称,用力可闭合眼睛合,口较明显不对称;(4)无效,面部症状无显著改善,口无力,眼不能闭。总有效为治愈、显效及有效之和。

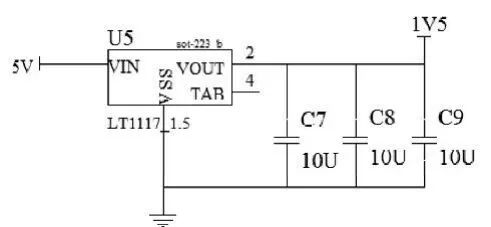

图3 电源电路图

FPGA 核心供电部分采用AMS1117-1.5V LDO 芯片,能提供1.5V 800 毫安的电流。

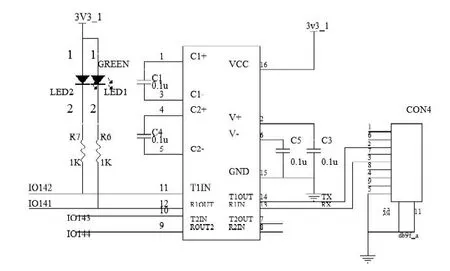

图4 RS232电路图

U 1是MAX 3232,负责将TTL的电平转为2 3 2电平,C 1,C 4,C 5,C 3 均是M A X 323 2所需要的外围电路,LED 1、LED2 是两个LED灯,它们分别在RS232数据接收和数据发送线上, 当有数据发送或接收时,它们会闪烁,表示正在发送或接收数据,可以根据这两个LED 灯判断是否有数据经过。

3 软件设计与仿真

3.1 上位机的设计

在PC机上运用Visual Basic编写上位机琴键控制界面,如下图所示:

图5 琴键控制界面

3.2 电子琴演奏电路的设计

电子琴演奏电路在Quartus II9.0 环境下采用顶层原理图设计。

3.2.1 程序设计流程图如下所示

图6 程序流程图

3.2.2 顶层电路图

图 7系统顶层电路图

(1)COU N T模块

由于设计中RDX输入的数据是以9600b/s传送的,那么需要一个接收同步信号的部分,用12MH时钟信号通过COUNT模块分1250倍频得到9600H z的频率来实现同步接收。

图8 COUNT模块

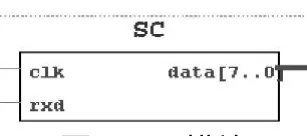

(2)SC模块

SC模块完成接收数据工作,RS232传送一个数据或者字符需要10位,即1位启动位加8位数据位,1个停止位。在SC模块中,通过集数方式来接受一位数据,一旦检测到1位启动位即低电平,就开始接受PC机送出的ASCII码,并开始计算,收到8位数据寄存后开始清零,完成一位数据的接收,输出8位ASC II码。

图9 SC模块

(3)TONETABA模块

TONETABA模块完成ASCII码转换为四位BCD码输出显示,另外控制频率值,来控制SPEAKER的频率发音。

图10 TONETABA模块

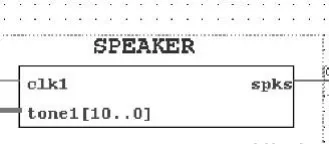

(4)SPEA KER模块

SPEAK ER模块实际上就是一个分频器,通过对12M H z分频产生不同的音符。

图11 SPEAKER模块

3.2.3 仿真结果

在程序设计完成及编译成功后,对系统进行了仿真,得到如下的图形。

图11 仿真电路图

4 总结

本设计进行了系统的调试和功能验证并利用QuartusII9.0软件生成.sof文件,下载到A ltera EP1C6T144C8N中,实际结果表明本系统设计的电子琴及硬件播放的音乐全部技术指标和功能很好地符合设计的要求,发声准确,满足了设计要求。

[1]邹益. FPGA/CPLD技术实用教程[M].北京:中国石化出版社.2010

[2]黄秋元,陈适. FPGA应用技术基础教程[M].北京:电子工业出版社.2009

[3]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社.2008

[4]曹瑞,卢印举. EDA技术与CPLD/FPGA开发应用简明教程[M].北京:清华大学出版社.2007

Music performance circuit design based on FPGA

Shi qi Mao Limin Zhang Lijun Chen Xiaofan

School of Electrical and Automation Engineering,Changshu Institute of Technology,changshu 21500,china

This paper design the Keyboard control interface using Visual Basic,then design performed circuit using VHDL Language,download the module to the Altera chip through the QUARTUS II platform, PC communicate with the FPGA via RS232 serial port to exchange the data .The performance circuit input tone through Keyboard control interface,The DO,RE, MI, FA, etc. 8 tones is controlled by the RS232 communication ,make the buzzer sounds,complete the Music performance

TP316

A

10.3969/j.issn.1001-8972.2011.10.076

施奇(1 9 8 9-),男, 汉族,江苏南京人,常熟理工学院电气与自动化工程学院。