直接隧穿栅电流对CMOS逻辑电路的影响

2011-10-12胡仕刚吴笑峰席在芳

胡仕刚,吴笑峰,席在芳

(湖南科技大学信息与电气工程学院,湖南湘潭411201)

0 引言

由于MOS器件的栅氧化层厚度随器件几何尺寸的不断缩小而变得越来越薄,超薄栅氧化层的可靠性也相应变得越来越重要[1,2]。当器件尺寸减小到亚微米和深亚微米量级,特别是当栅氧化层的厚度小于3nm后,为保证器件正常工作,外加电压也相应减小。在较小的栅电压下,栅氧化层中将会存在明显的载流子隧穿电流,而且该隧穿电流也明显不再符合FN隧穿漏电流的规律[3],被称为直接隧穿(DT)电流。即使在工作电压下,超薄栅氧化层中也存在明显的直接隧穿漏电流。这种漏电流将会对器件的功耗、逻辑电路的驱动能力、存储器的存储能力以及器件的可靠性等产生极其不利的影响。本文基于可靠性理论和电路级仿真深入地研究了直接隧穿电流对CMOS逻辑电路的影响。仿真工具为HSpice软件,MOS器件模型参数采用的是BSIM4,LEVEL 54。栅氧化层厚度是1.4nm,工作电压为1.2V。

1 MOS器件直接隧穿理论

如图1所示的MOS器件,直接隧穿栅电流由几部分组成,Igso和Igdo是穿过栅对源、漏交叠区的寄生漏电流、Igc是栅对反型沟道的隧穿电流,Igc由流向源极的Igs和流向漏极Igd组成[4]。由图可知,穿越MOSFET栅氧化层的隧穿电流不仅存在于反型沟道内,也存在于栅—源、栅—漏覆盖区的积累层内。这种栅源和栅漏交叠区之间发生的隧穿就称为边缘直接隧穿(EDT)。随着沟道长度的缩小,覆盖区所占的比例增大,穿越覆盖区的隧穿电流的影响将变得更加显著。穿越栅氧化层的边缘直接隧穿电流增加了电路的泄漏电流,从而增加了电路的静态功耗。

图1 栅隧穿电流组成

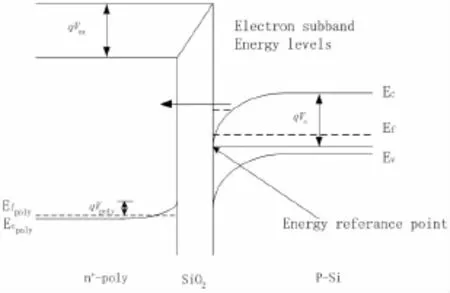

图2 NMOS结构强反型时能带图

图2给出了n+多晶硅/SiO2/p-Si NMOS结构反型时的能带图。直接隧穿电流密度可近似由下式表示[6]:

其中,Eox是氧化层的电场强度,b是Si-SiO2势垒高度,Vox是氧化层上的电压降,A和B是依赖于电子有效质量和Si-SiO2势垒高度等因素的系数。

其中,ψs是表面势,Vgs是外加栅电压,Vfb是平带电压,Vpoly是由于多晶硅效应引起的电压降。

其中,tox是氧化层厚度。

由于表面势ψs随着漏端偏置和衬底偏置会发生变化,所以漏端偏置和衬底偏置也会改变栅电流密度。

对于理想NMOS-FET,强反型,即ψs>2f时

式中的V的是电子准费米势,范围从源端Vsb到漏端Vds。考虑漏端偏置的影响,则ψs,drain=ψs(Vds+Vsb),ψs,source=ψs(Vsb)。当漏偏Vd>0时,栅电流(Ig)由栅—源电流(Igs)和栅—漏电流(Igd)两部分组成。Igd由一定漏偏下的表面势ψs,drain决定。Igs和Igd可以分别计算。当漏端电压增加,漏端的表面势随之增加,这就促使漏端附近氧化层上的压降减小,Igd减小。栅电流也随之减小,甚至变为负值。

将MOS管的背接触或体相对源加反向偏置是一种调整阈值电压的方法。这种电学调整方法出现在离子注入技术之前,利用的就是所谓体效应和衬偏效应。考虑衬底反向偏置时,衬底中的耗尽区变厚,耗尽层电荷增加,从而在栅压相同情况下,衬底表面的表面势增大。表面势的增加,使得栅氧化层上的压降减小,从而使栅隧穿电流减小。

2 逻辑电路中MOS器件的栅泄漏

CMOS数字逻辑电路中,MOS器件的工作状态主要有四种。图3给出了CMOS逻辑电路中NMOS管常见的四种工作状态。

图3 CMOS逻辑电路中NMOS管的四种工作状态

本文将这四种工作状态分别定义为线性区、饱和区、亚阈区和截止区。当NMOS管工作于线性区时,栅电压为高电位“1”而其它端电压均处于低电位“0”。沟道反型层电子和源漏区积累的电子都将向栅极发生直接隧穿,隧穿电流沿沟道可看成近似均匀分布;当NMOS工作于饱和区时,栅和漏端同为高电位,尽管沟道反型层电子和源漏区积累的电子都将向栅极发生直接隧穿,但由于漏端偏置的影响很大,饱和区的栅隧穿电流将比线性区的栅隧穿电流小很多;当NMOS工作于亚阈区时,栅电压为低电位“0”而漏端电压为高电位“1”,其它端电压均处于低电位“0”,栅漏交叠区中多晶硅栅极的电子将向漏端发生边缘直接隧穿;当NMOS工作于截止区时,所有端电压均为低电位,无隧穿电流。此外,若衬底端实际电压小于源端电压时候,由于衬底偏置的影响,栅电流将会减小。

CMOS逻辑电路中PMOS管的常见工作状态与NMOS类似。在同一工作状态下,与NMOS管的工作状态相比,各端电压电位相反,发生隧穿的载流子主要是空穴。此外,若衬底端实际电压大于源端电压时候,由于衬底偏置的影响,PMOS栅电流将会减小。

3 CMOS反相器静态栅泄漏研究

CMOS反相器电路由两只增强型MOS-FET组成,其中一个为N沟道结构,另一个为P沟道结构。为了电路正常工作,要求电源电压VDD大于两个管子开启电压绝对值之和,即VDD>(VTN+|VTP|)。驱动提供的静态功率是PIN,电源提供的静态功率PDD,反相器提供给负载的功率是POUT,反相器静功率损耗是

当静态输入电压为VIN,输入电流为IIN,电源电压为VDD,电源电流为IDD,静态输出电压为VOUT和输出电流为IOUT时,有

在图4所示的CMOS反相器中,栅电流将产生输入电流IIN,从而对静态功耗产生影响。电路中由于器件源端和衬底端是接在一起的,这两端之间的电压VBS=0,所以衬底电流产生的功耗为0,可以忽略。

在图4(a)中,输入电压近似为0,输出电压等于VDD。NMOS-FET偏置于亚阈区,而PMOS-FET偏置于线性区。NMOS-FET的栅隧穿电流路径局限在栅漏交叠区,其方向是从输出节点指向输入节点。PMOS-FET的栅隧穿电流分布于沟道和源漏交叠区,其方向是从电源节点、沟道和输出节点分别指向输入节点。当反相器偏置于这种条件时,IIN小于0,IDD和IOUT都大于0。从而有PIN小于0,PDD和POUT都大于0。

在图4(b)中,输入电压近似为VDD,输出电压等于0。PMOS-FET偏置于亚阈区,NMOS-FET工作于线性区。PMOS-FET的栅隧穿电流路径局限在栅漏交叠区,其方向是从输入节点指向输出节点。NMOS-FET的栅隧穿电流遍布于沟道和源漏交叠区,其方向是从输入节点分别指向输出节点、沟道和零电位节点。当反相器处于这种偏置条件时,IIN和IDD都大于0,IOUT小于0。从而有POUT小于0,PIN和PDD都大于0。

定义VDD=1.2V,利用HSpice对CMOS反相器进行仿真。PMOS器件尺寸W/L=5.5μm/1μm,NMOS器件尺寸定为W/L=2.5μm/1μm。

图4 存在栅隧穿时CMOS反相器中电流路径

图5(a)给出了VIN从0V到1.2V直流扫描时CMOS反相器的栅泄漏电流。随着VIN正向增加,IIN从负值向正值正向增加。VIN≈0.53V,IIN≈0,但这个区域并非反相器件工作区域。VIN接近0时,IIN小于0,PIN小于0;VIN接近1.2V时,IIN大于0,PIN大于0。所得结论与上面分析一致。IGP是PMOS-FET的静态栅电流,IGP随着VIN正向增加,从负值向正值沿正向增加,在VIN接近0时与总的输入电流IIN几乎相等,此时PMOS-FET的空穴隧穿电流占主要成分。IGN是NMOS-FET的静态栅漏电流,IGN随着VIN正向增加,也从负值向正值沿正向增加,在VIN接近1.2V时与总的输入电流IIN几乎相等,此时NMOS-FET的电子隧穿泄漏占主要成分。

图5(b)给出了VIN从0V到1.2V直流扫描时电压源VDD提供的电流IDD。VIN接近0时电压源VDD提供的电流要比VIN接近1.2V时提供的电流大三个数量级。这说明,VIN接近0V时,器件静态功耗将主要由电源VDD提供;而VIN接近VDD时,器件静态功耗主要由输入驱动VIN提供。从图5(b)可以看出,在VIN≈0.5VDD=0.60V时IDD达到峰值,电源提供的静态功率最大;

在VIN接近0V或者接近1.2V时IDD是比较小的,电源提供的功率相对较小。

图5 CMOS反相器中VIN从0V到1.2V直流扫描特性

4 结语

本文基于可靠性理论和电路级仿真深入地研究直了接隧穿电流对CMOS逻辑电路的影响。文中的仿真结果符合理论分析,器件氧化层厚度越小,栅漏电流的影响越严重,甚至电路的正常工作性能也受到干扰。文中的理论和实验数据将有助于以后电路设计。

[1] Hu Shigang,Hao Yue,Ma Xiaohua,et al.Study on the degradation of NMOSFETs with ultra-hin gate oxide under CHE stress at high temperature.Chinese Physics B,2009,18(12):5479-5484.

[2] 陈卫兵,徐静平,邹晓,小尺寸MOSFET隧穿电流解析模型.北京:物理学报,2006,55(10):5036-5040

[3] Choi C H,Nam K Y,Yu Z P,et al.Impact of gate direct tunneling current on circuit performance:a simulation study.IEEE Trans.Electron Devices,2001,48(12):2823-2829

[4] Cao K,Lee W C,Liu W,et al.BSIM4 Gate Leakage Model including Source-Drain Partition.In IEDM Technical Digest.,December 2000:815-818

[5] Ranuarez J C,Deen M J,Chen C C.A Review of Gate Tunneling Current in MOS Devices.2006,Microelectronics reliability,46(12):1939-1956