低压三级放大器的密勒

——前馈频率补偿

2011-10-12侯俊芳翟向坤

侯俊芳,翟向坤,孙 涛

(1.天津轻工职业技术学院,天津市 300380;2.埃派克森微电子(上海)有限公司,上海市 201203;3.天津市科学技术信息研究所,天津市 300074)

低压三级放大器的密勒

——前馈频率补偿

侯俊芳1,翟向坤2,孙 涛3

(1.天津轻工职业技术学院,天津市 300380;2.埃派克森微电子(上海)有限公司,上海市 201203;3.天津市科学技术信息研究所,天津市 300074)

论文将极点分离、前馈补偿和密勒支路补偿技术相结合,采用0.5um工艺设计CMOS放大器,M iller-Feedthrough Compensation(M FC),分别驱动120p F/25KΩ和1200p F/25KΩ负载,实现增益带宽积14.7M Hz和3.3M Hz。

密勒支路补偿;前馈补偿;极点分离;低压放大器

一、引言

低压便携式设备的广泛应用,对片上集成的低压低功耗设计提出更高的要求[1]。可驱动大电容负载的高增益、高带宽放大器作为便携式设备中低压降电压调节器的误差放大器,如图1所示。功率管的栅极寄生电容,在0.5um工艺中大约处于100p F数量级。随着工艺的更新和电源电压的降低,单级共源共栅结构不再适应高增益、高带宽的设计需要;必须采用低压、多级放大器,经过频率补偿后实现对大电容负载的驱动。由于多级放大器潜在严重的闭环稳定性问题,因此它对频率补偿技术的要求通常是比较高的[2][3][4][5][6]。

多级放大器的频率补偿架构中,网状密勒补偿(NMC)[7]在低压情况下,不适于驱动大电容负载,因为它的单位增益带宽随着放大器级数的增加而减小。补偿电容的尺寸随着负载的增大而增大,不适合高度集成的要求。NMC放大器稳定性的改善是通过消除或移动右半平面零点实现的。放大器带宽的明显改进,是在衰减因子补偿(DFCFC)[5]等技术出现后实现的。它们通过较小的补偿电容,在保证系统稳定的情况下提高系统的带宽。但是,这些技术的共同缺点在于,补偿电容的大小强烈依赖于负载电容的大小。随着负载电容增大,补偿电容的增大所引起的芯片面积消耗,严重限制上述技术的应用。为克服上述问题并进一步改善带宽,单密勒电容前馈补偿(SM FFC)[4]等技术逐步被报道。这些补偿技术虽然改善了系统的带宽,但是在单位增益频率处,系统相位的下降趋势陡峭,不良的工艺偏差很容易造成系统的振荡,降低产品的良率。此外,它们所涉及的补偿电容仍然与负载电容的大小是相关的;当负载电容进一步增大到纳法数量级时,补偿电容仍需要消耗较大的芯片面积。

结合已有的补偿技术,本文提出了一种密勒技术和前馈技术相结合的补偿结构,称为M FC(M iller-Feedthrough Compensation)放大器,如图2所示。

图1 典型的LDO结构

图2 M FC放大器的拓扑结构

二、M FC放大器

M FC放大器的主通路由gm1、gm2和gm l构成。电容CC1产生极点分离的作用。gmf1完成前馈补偿,形成一个低频的LHP零点和一个高频的RHP零点。高频RHP零点对系统稳定性的影响可以忽略;而低频L HP零点则可以起到频率补偿的作用。gmf作用在于形成推挽输出级,增大输出电压的摆率。gmpc和电容CC2是根据文献[8]的补偿原理引入的补偿支路,在系统的单位增益频率位置处,引入补偿的零极点。文献[5]也采用这种补偿结构;其作者根据补偿支路对系统传输函数的影响,将其命名为DFC补偿技术。但是,按照文献[13]的叙述,补偿支路是利用密勒作用,在传输函数中引入补偿的零极点。这一点可以在本文传输函数的推导中得到证实。因此,本文只将它称为密勒支路补偿技术。

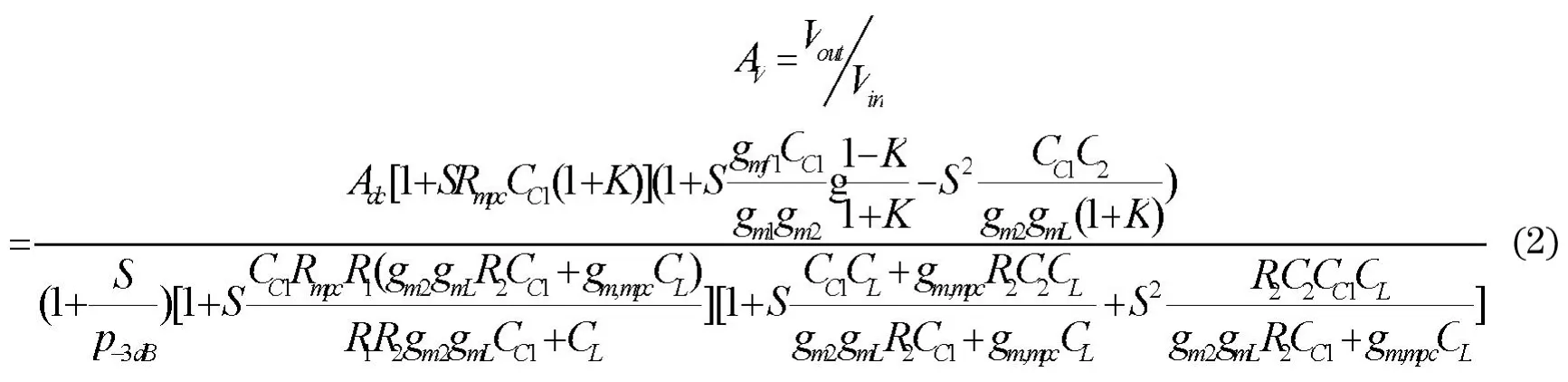

分析基于以下假设条件:每一级的增益都大于1;寄生电容远远小于补偿电容CC1和CC2以及负载电容CL;负载电容为100p F数量级;补偿电容CC1和CC2相等。系统的传输函数为

其中Adc=gm1gm2gmLR1R2RL,P-3dB=gm2gmLR1R2RLCc,K=(gm,mpcgmf1)/(gm1gm2)。从传输函数中可以看到,系统存在三个非主极点和三个零点。当驱动电容负载为纳法数量级时,传输函数应该修正为

电容CC1通过极点分离产生-3dB主极点;前馈补偿产生一个精确补偿的零极点;密勒支路补偿在单位增益频率处引入补偿的零极点对;同时,两种补偿技术共同形成复数零点和复数极点,构成复数零极点补偿。

为了明确密勒支路补偿的作用,验证前文的论述,采用M atlab绘制图2结构中M PC模块加入前后的根轨迹,如图3所示。此处忽略了150M Hz以上的零极点。仿真的结果表明,密勒支路补偿后系统增加了零点Z3和极点 P3,推动 P1’和 P2’相遇产生复数极点对 P1和 P2,并推向高频段;而且,M PC补偿将零点Z1‘和Z2’也推向高频段,形成Z1和Z2。补偿前后的根轨迹,证明了前文论述的正确性。同时,仿真显示出gmf1产生的L HP零点与极点相消的情况。

图3 密勒支路补偿前后系统的根轨迹,(a)作用之后 (b)作用之前

三、设计与验证

根据图2的架构,采用CSMC 0.5μm CMOS工艺设计具体的电路结构如图4所示。晶体管M 3和M 4构成前馈通路;M 17、M 18和CC2构成密勒支路;M 19形成gmf通路。

图4 M FC实际电路图

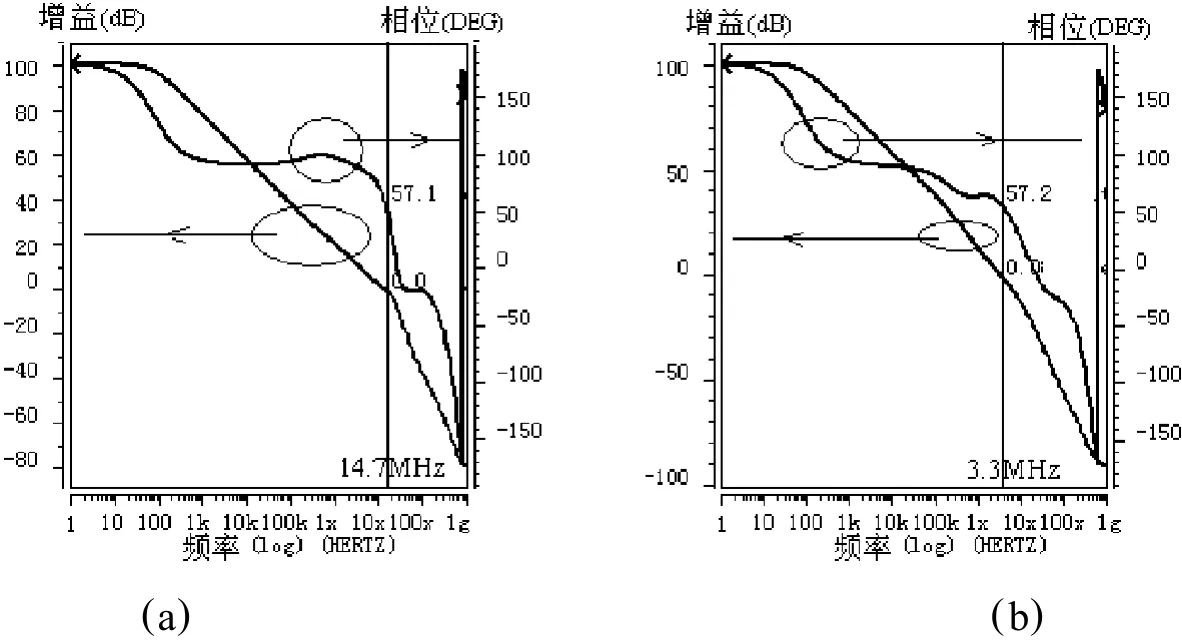

选取补偿电容CC1=CC2=3p F,负载电容为120p F,其频率特性如图5(a)所示;为驱动更大的负载,在不改变晶体管的尺寸和偏置的情况下,选取补偿电容CC1=CC2=3p F,负载电容为1200p F,其频率特性如图5(b)所示。仿真结果表明,密勒支路补偿的加入,使单位增益处的相位变化趋于缓慢;在负载120p F和负载1200p F的情况下,分别实现相位裕度为57.1°@14.7M Hz和57.2°@3.3M Hz。需要注意的是,驱动1200p F时,密勒支路的补偿作用更为明显。在没有增大补偿电容的情况下,实现了对更大负载电容的驱动,并且单位增益带宽处的相位变化更缓慢。M FC放大器的基本特性总结为表1。通过仿真验证,M FC结构是可以用于低压低功耗设计的,并且在驱动纳法级负载具有显著地优势。

图5 M FC在不同负载条件下频率响应特性,(a)120p F(b)1200p F情况

表1 M FC放大器的仿真结果

将本文的工作、文献[4]的SM FFC和文献[5]的DFC进行比较,如表2所示。为了综合比较放大器的驱动能力,选择两个常用的优值 FOMS和 FOML,其单位分别为 M Hz p F/mW和 V/μs p F/mW。前者衡量运放小信号的综合性能,后者衡量运放大信号的综合性能。其定义分别为:从比较的结果可以看出,M FC结合了SM FFC和DFC的优点,采用小的补偿电容,拓展了系统的带宽。

表2 不同电路结构及补偿方法下三级运放的性能比较

四、结论

本文将极点分离技术、密勒支路补偿和前馈技术相结合,设计低压应用的MFC放大器。设计中使用总共6p F的电容实现对放大器的频率特性进行补偿,实现驱动100p F数量级和纳法数量级电容负载能力。同时应当指出,密勒支路补偿在系统中引入补偿零极点,并推动非主极点向高频移动的特性,可以广泛应用于放大器的频率补偿中。只是它对零极点的控制能力有限,往往需要牺牲较大的功耗。所以,在多级放大器设计中,单独的MPC补偿是不能发挥优势的,必须和其他补偿技术相互配合。

[1]Gabriel A lfonso Rincon-Mora.Current efficient,low voltage,low drop-out regulators:[Thesis for PhD].Geor2 gia Institute of Technology.1996.

[2]De Cremoux,G.Christoforou,Y.van Loo.I.A new method for multip lying the M iller capacitance using active components[voltage regulator examp le]].Custom Integrated Circuits Conference,2003.Proceedings of the IEEE 2003.Sep t.2003:697-700.

[3]Chia-Chun Tsai,Chin-Yen Lin,Yuh-Shyan Hwang,et al.A multi-mode LDO-based Li-ion battery charger in 0.35/sp l mu/m CMOS technology.Circuits and System s 2004,Proceedings of 2004 IEEE Asia-Pacific Conference.Dec.2004,1:49-52.

[4]Xiaohua Fan;M ishra,C.;Sanchez-Sinencio.Single M iller capacito r frequency compensation technique for low-power multistage amp lifiers.IEEE Journal of Solid-State Circuits,Mar.2005,40:584-592.

[5]Leung K N,Mok P K T.“Three-stage large capacitive load amplifier w ith damping-facto r-control frequency compensation.IEEE Journal of Solid-State Circuit,2000,35(2):221-230”.

[6]G.A.Rincom-Mo ra,“Active capacitor multip lier in M iller compensated circuits”,IEEE J.Solid State Circuits,vol.35,no.1,pp.26-32,Jan.2000.

[7]R.G.H.Eschauzier,L.P.T.Kerklaan,and J.H.Huijsing,“A 100 M Hz 100 dB operational amplifier w ith mul2 tipath nested M iller compensation structrue”,IEEE J.Solid State Circuits,vol.27,no.12,pp.1709-1717,Dec.1992.

[8]Yang H.C.,A llstot D.J.Modified modeling of M iller compensation fo r two-stage operational amp lifiers.Cir2 cuits and Systems,1991,IEEE International Sympoisum.June 1991,5:2557-2560.

A bs tra c t:A new CMOS amp lifier,M iller-Feedthrough Compensation(M FC),is p roposed and designed using 0.5 um CMOS technology.It com bines poles sp litting technology,feedthrough technolo2 gy and m iller path technology in order to compensate frequency characteristic.Sim ulation results show that it has achieved Gain Band W idths of 14.7M Hz and 3.3M Hz,driving loads of 120p F/25 KΩand 1200p F/25KΩrespectively.

Ke y w o rd s:m iller path compensation;feedthrough compensation;poles sp litting;low voltage amp lifier

M iller-Feedth rough Com pensation for L ow V oltage Th ree-stage Amp lifiers

HOU Jun-fang1,ZHAI Xiang-kun2,SUN Tao3

(1.Tianjin L ight Industry Professiona l Technica l College,Tianjin 300380;2.A pexone M icroelectronics(Shanghai)Co.L td.,Shanghai,201203,China;3.Tianjin Institute of Scientific&Technical Information,Tianjin 300074 China)

TN72

A

1673-582X(2011)02-0050-05

2010-10-10

侯俊芳(1982-),女,汉族,河北工业大学工程硕士在读。主要研究方向集成电路及信号处理;翟向坤(1981-),男,汉族,电子科技大学硕士研究生,电子薄膜与集成器件国家重点实验室。主要研究方向功率半导体及其集成电路;孙涛(1981-),男,汉族,河北工业大学硕士研究生。主要研究方向电子信息与互联网应用开发。