一种适合硬件实现的低复杂度MAD预测算法

2011-09-04殷海兵周冰倩

王 佳,殷海兵,周冰倩

(中国计量学院信息工程学院,浙江杭州310018)

0 引言

码率控制算法是在码率受限的条件下通过动态的调整编码参数来优化视频质量。假如没有进行码率控制,当通过有限的信道带宽传送压缩的比特流时缓冲区就会上溢或者下溢。在视频编码标准中,有几种码率控制算法已经被推荐作为参考算法,比如MPEG-2的TM5、H.263的TMN8、MPGE-4的VM8、H.264AVC的G012。一些MPEG-2或H.263的码率控制算法已经有人提出了硬件实现方案[1]。对如H.264/AVC,它的码率控制算法参考提案G012更为复杂,其直接硬件实现需要大量的门电路[2]。对如H.264/AVC视频编码器来说,G012的硬件消耗是非常大的,针对硬件实现的特点提出了一种适合硬件实现的码率控制算法[3]。本文在H264/AVC编码器Zig-zag宏块编码顺序和宏块级流水结构的基础上,利用时域和频域的相关性,提出了一种新的低复杂度MAD预测算法,解决了硬件实现时的数据依赖问题。

1 码率控制硬件实现

通常硬件编码器的实现面临着两个问题,数据吞吐和存储带宽。为了提高数据处理效率硬件编码器通常采用Zigzag宏块顺序,宏块级流水结构。两者的结合导致码率控制算法实现时复杂的数据依赖关系。并且G012算法MAD预测模块的高复杂度会消耗大量的硬件资源。

1.1 Zig-zag宏块编码顺序

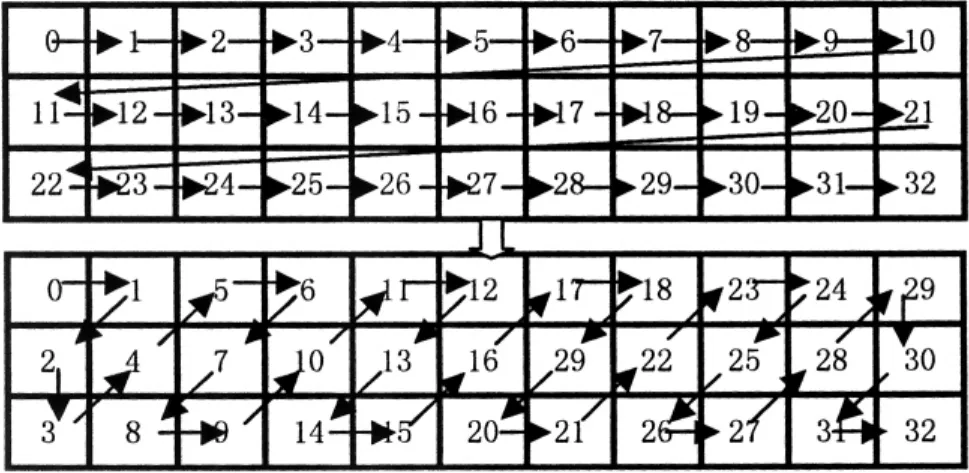

硬件编码器为了实现数据的水平和垂直复用,通常采用Zig-zag[4]宏块编码顺序代替软件实现时的光栅扫描顺序。编码顺序的改变导致数据的水平和垂直的依赖关系改变,如图1所示,每3个宏块行采用Zig-zag宏块编码顺序。

1.2 宏块流水结构

通常情况下,H.264/AVC硬件编码器宏块级通常采用3级或者4级的流水结构。如图2所示,在宏块流水开始前,通过码率控制(RC)模块获取Qp,依次经过整象素运动估计(IME),亚象素运动估计/帧内预测(FME/INTRAL),熵编码/去块效应滤波(EC/DB)3级流水[3]。

图1 每3个宏块行的Zig-zag宏块编码顺序

图2 3级宏块流水结构

1.3 G012码率控制算法MAD预测

H.264/AVC的码率控制算法G012中,采用线性预测的方法计算MAD:

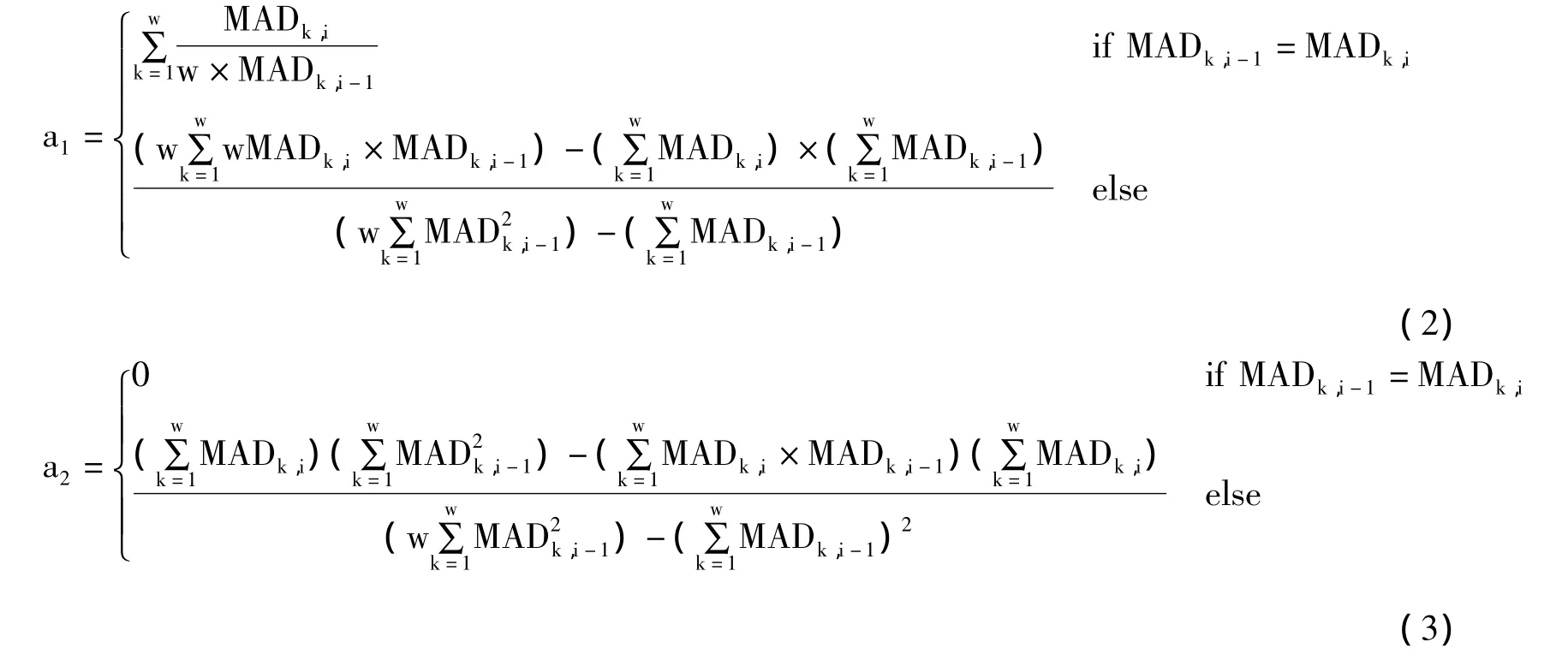

式中,两个参数a1和a2采用线性回归的方法进行更新。参数a1和a2的计算如下所示[3],计算复杂度很高,直接采用硬件实现,会消耗大量的硬件资源。

2 改进MAD预测算法

针对Zigzag宏块编码顺序和宏块流水结构所产生的数据依赖问题,以及MAD线性预测参数更新的高复杂度,提出了一种利用时域和空域相关性来预测当前编码宏块MAD值。如图3所示,当前编码宏块MB(n,i),MB(n-1,i)为前一帧相同位置宏块,MBU和MBL分别当前编码宏块上方和左边宏块,MBA、MBB和MBC位置依次如图3所示。由于每3个宏块行采用Zigzag宏块编码顺序的特殊性,当前编码宏块只有上方和左边已编码宏块可以用来进行预测。根据观察和数据分析,MBL和MBU已经前一帧相同位置MB(n-1,i)的相关性最大,可以直接采用这3个已编码宏块来预测当前宏块值。综合考虑3级宏块流水结构和边界情况,具体MAD预测流程如图4所示,其中w1和w2的值为7/8和3/4,。

图3 当前预测宏块和周围宏块

图4 MAD预测流程图

3 实验结果

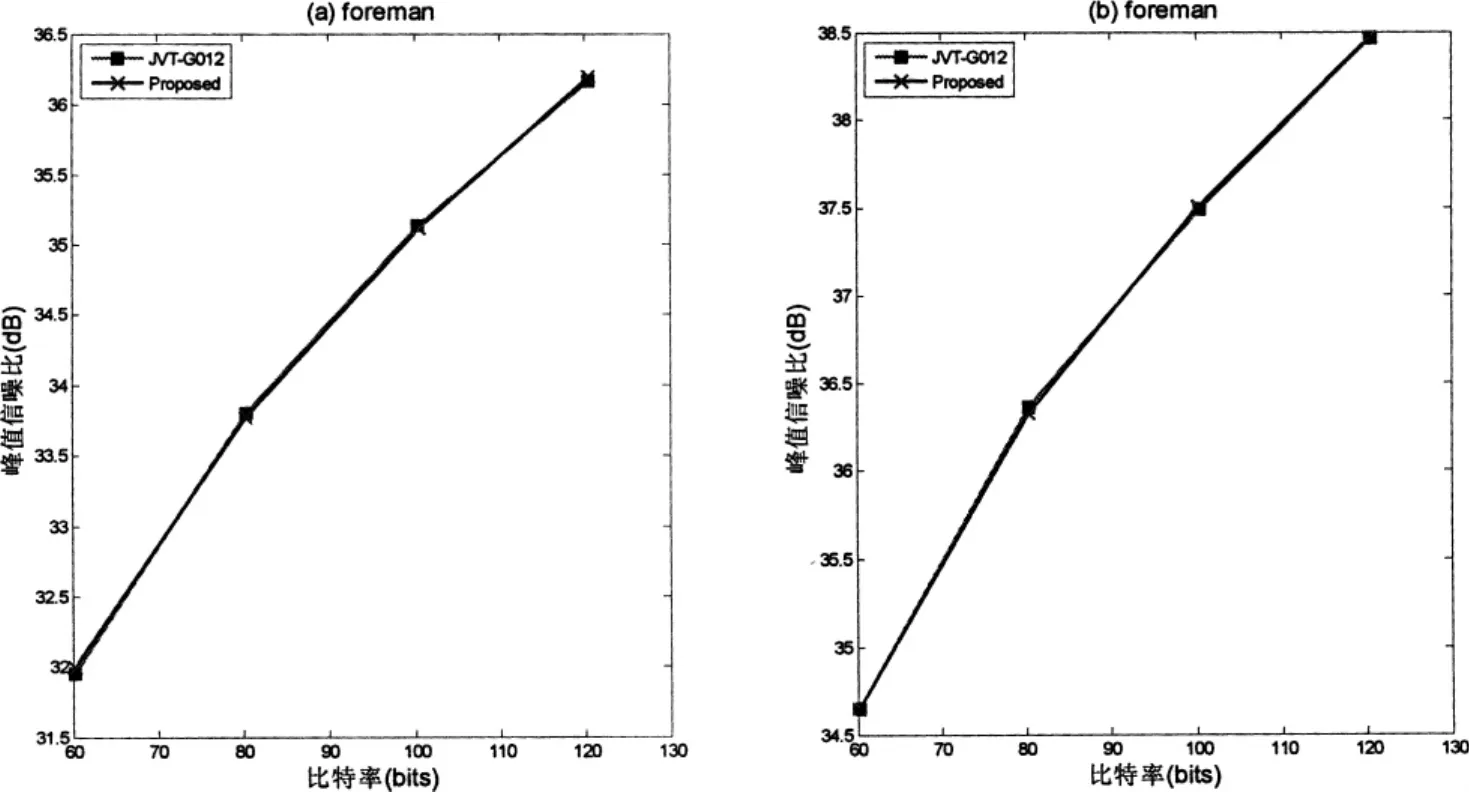

本次实验基于JM10.2参考模型,改变宏块编码的光栅扫描顺序为每3个宏块行的Zigzag编码顺序,然后进行码流重排,并仿真本文提出的低复杂度MAD预测算法。测试序列分别为低速运动序列“News”,高速运动序列“Foreman”和“Carphone”,复杂序列“Mobile”。测试码率分别为 60,80,100,120kbps。实验结果如表1,图5所示。

表1 实验结果对比

4 结束语

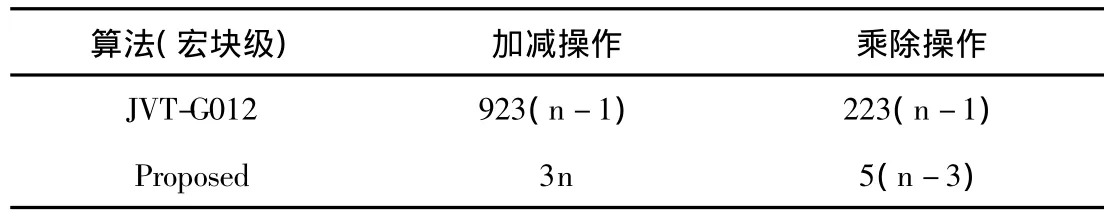

表1、图5中,在相同的码率条件下可以保持与G012相同的PSNR,视频质量没有降低,但MAD预测部分复杂度大大降低。如表2所示,其中n表示一帧中的宏块数目,与原始算法G012相比,Zig-zag编码情况下MAD预测部分复杂度降低了92%,并解决了数据依赖问题,适合硬件实现。

图5 Foreman和Carphone测试序列率失真曲线

表2 算法复杂度对比

[1] ChenChing-Yeh,Huang Chao-Tsung,Chen Yi-Hau,etal.Level C+Data Reuse Scheme for Motion Estimation With Corresponding Coding Orders[J].IEEE Transactions on CSVT,2006,16(4):553 -558.

[2] Chang Hsiu-Cheng,Chen Jia-Wei,Su Ching-Lung,etal.A 7mw to 183mw dynamic quality-scalable H.264 video encoder chip[C].San Francisco:IEEE International Conference,2 007:280 -603.

[3] Kuo Chih-Hung,Chang Li-Chuan,Fan Kuan-Wei,etal.Hardware/Software Codesign of a Low-Cost Rate Control Scheme for H.264/AVC[J].IEEE Transactions on CSVT,2010,20(2):250 -261.

[4] Wu Ping-Tsung,Chang Tzu-Chun,Su Ching-Lung,etal.A H.264 basic-unit level rate control algorithm facilitating hardware realization[C].Las Vegas:IEEE International Conference,2008:2 158 -2 188.

[5] Yin Hai bing,Qi Hong gang,Jia Huizhu,etal.Efficient Macroblock Pipeline Structure in High Definition AVS Video Encoder VLSI Architecture[C].Paris:IEEE International Conference,2010:669 -672.