基于TMS320DM6467的高清晰视频接口的硬件设计

2011-08-09杨明极吕鑫淼吕鑫磊

杨明极,吕鑫淼,吕鑫磊,2

(1.哈尔滨理工大学测控技术与通信工程学院,黑龙江 哈尔滨 150080;2.中国石油天然气集团公司大庆石化分公司,黑龙江 大庆 163714)

责任编辑:任健男

0 引言

随着人们生活水平的提高,对高清视频的质量与效果提出了更高的要求。因此,由TI公司研制生产的基于达芬奇技术的高性能TMS320DM6467(简称DM6467)数字媒体处理器孕育而生,它具有ARM+DSP的双核结构,简化了系统总体的设计难度[1-2]。其强大的控制与运算功能,配合高清视频解码器TVP7002与高清/标清视频编码器ADV7343使用,满足了高清视频开发的要求。

1 高性能达芬奇处理器

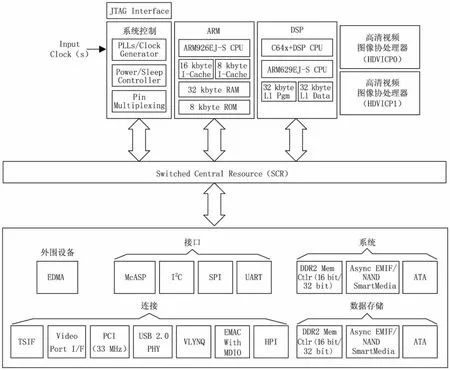

DM6467充分利用了TI的达芬奇技术,以满足网络媒体的编码和解码处理的下一代数字媒体需求的嵌入式设备。DM6467具有双核架构,包含TMS320C64x+DSP内核和ARM926EJ-S内核,提供丰富而又强大的DSP和精简指令集计算机(RISC)技术。ARM926EJ-S是32位RISC处理器内核,执行32位或16位指令和32位,16位或8位数据程序。该内核采用流水线技术,使处理器和内存系统的所有部分都可连续工作。系统框图如图1所示。

2 硬件系统设计

TMS320DM6467数字媒体处理器包括2个可编程的高清视频图像协处理器引擎,VPIF视频接口有4个通道Channel0,Channel1,Channel2,Channel3。2 个输入采集通道Channel0和Channel1为2路8 bit标准清晰度视频或同为1路16 bit高清晰度视频。2个输出显示通道Channel2和Channel3为2路8 bit标准清晰度视频或同为1路16 bit高清晰度视频。

2.1 视频输出系统设计

ADV7343是TI公司生产的一款高清标清兼容的视频编码器。它适用于高清和标清视频信号的DA变换。ADV7343 共有24 bit数字视频输入接口 S[7-0],Y[7-0],C[7-0],支持 4∶2∶2 YCbCr(SD,ED,HD),4∶4∶4 YCbCr(ED,HD),4∶4∶4 RGB(SD,ED,HD)的数字视频输入;共有6路模拟视频输出通道,可以输出CVBS,YPbPr,RGB格式的模拟视频信号。ADV7343的工作模式由I2C对其内部寄存器编程实现。

VPIF视频接口作为标清视频输出时利用Channel2输出8 bit的4∶2∶2 YCbCr数字视频信号,与解码器ADV7343 的 S[7-0]引 脚 相 连,VPIF 的 时 钟 引 脚VPIF_CLKOUT2与 ADV7343的 CLK_INA相连,提供27 MHz的时钟。该部分为标清视频输出扩展,针对高清视频可去掉。VPIF视频接口作为高清视频输出时利用Channel2和 Channel3 输出16 bit 4∶2∶2 YCbCr(Channel 2作为8 bit亮度信号Y,Channel3作为8 bit色差信号CbCr)数字视频信号,与解码器ADV7343的Y[7-0]和C[7-0]引脚相连,VPIF 的时钟引脚 VPIF_CLKOUT2和VPIF_CLKOUT3分别与ADV7343的CLKIN_A和CLKIN_B相连,提供74.25 MHz的时钟。标清与高清视频输出复用采用TI公司的SN74CBT16214与SN74CBTLV3384芯片。这2种芯片的使能是通过TMS320DM6467通过I2C总线控制CPLD实现的。视频输出系统硬件连接如图2所示。

图1 DM6467处理器系统框图

图2 TMS320DM6467与ADV7343的硬件连接示意图

DM6467通过I2C总线控制CPLD使VIDOUT_S0和VIDOUT_OEn为高电平。VIDOUT_S1为低电平时,SN74CBT16214的A与1B导通,SN74CBTLV3384不使能,此时系统是标清视频输出;当CPLD使VIDOUT_S0和VIDOUT_OEn电平为低,VIDOUT_S1为高电平时,SN74CBT16214的A与2B导通,SN74CBTLV3384使能,此时系统是高清视频输出。

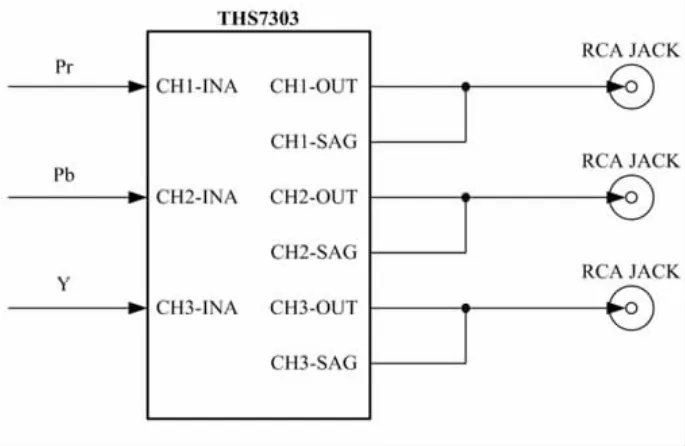

经ADV7343解码输出的模拟视频信号需要经过视频信号放大器才能与显示设备相连。高清视频放大器采用TI公司的THS7303,标清视频放大器采用THS7314。放大器硬件连接如图3、图4所示。

图3 THS7303的硬件连接示意图

图4 THS7314的硬件连接示意图

2.2 视频输入系统设计

TVP7002是TI公司的一款高清视频解码器,用于高清视频信号的A/D变换。

TVP7002共有30 bit数字视频输出接口R[9-0],G[9-0],B[9-0],支持480i,576i,480p,576p,720p,1080i,1080p等多种视频标准,支持带有嵌入式定时基准码的20 bit4∶2∶2 输出,支持RGB/YCbCr4∶4∶4 和YCbCr4∶2∶2 输出模式,支持RGB到YCbCr色度空间变换。TVP7002的工作模式由I2C对其内部寄存器编程实现。

高清视频采集系统中 TVP7002 的 G[9-2]和 B[9-2]分别与VPIF的视频采集通道Channe 2和Channel3相连接。通过I2C总线对其内部寄存器进行控制,使G[9-2]和B[9-2]输出8 bit亮度信号Y和8 bit色差信号CbCr。TVP7002的 DATACLK引脚 VPIF_CLKIN0相连,提供74.25 MHz的时钟。标清采视频集系统采用TVP5147M1,支持NTSC,PAL,SECAM等多种彩色制式,使用简单方便。

该部分为扩展功能,针对高清视频研究可去掉。标清与高清视频输如复用采用2个SN74CBT16214芯片。该芯片的使能是通过DM6467通过I2C总线控制CPLD实现的。视频输入系统硬件连接如图5所示。

图5 DM6467与TVP7002的硬件连接示意图

DM6467通过I2C总线控制CPLD使VIDINL_S1和VIDINH_S1为高电平,VIDINL_S0和VIDINH_S0为低电平时,SN74CBT16214的A与B2同时导通,此时系统是高清视频输入;当CPLD使VIDINL_S1和VIDINH_S1为低电平,VIDINL_S0和VIDINH_S0为高电平时,SN74CBT16214的A与1B导通,此时系统是CVBS标清视频输入与SVideo标清视频输入。

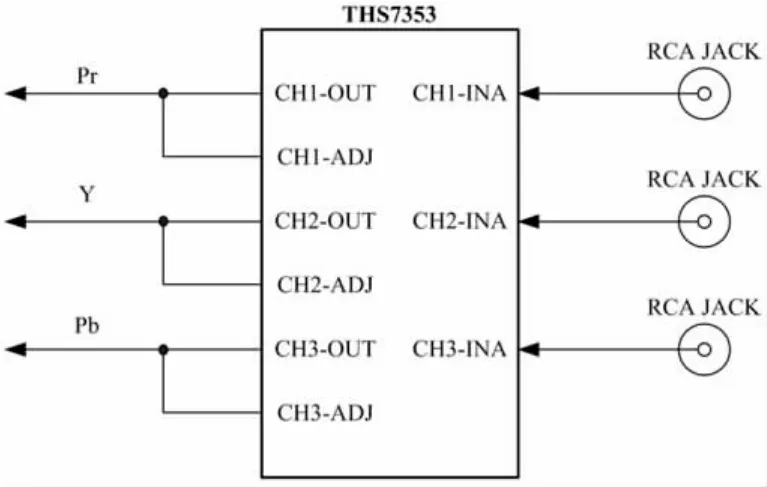

模拟视频信号进入TVP7002之前,需经过视频缓冲器进行滤波与增强。视频缓冲器采用TI公司生产的THS7353。缓冲器硬件连接如图6所示。

图6 THS7353的硬件连接示意图

3 小结

本文着重介绍了DM6467处理器的VPIF视频接口,并选用了高清视频解码器TVP7002和高清/标清视频编码器ADV7343设计出视频显示采集系统。该系统实现了模拟高清视频输出YPbPr,模拟标清视频输出CVBS和S-Video;标清模拟视频输入 NTSC,PAL,CVBS,高清模拟视频输入YPbPr,在数字视频服务与监控领域有着广阔发展。

[1]达芬奇处理器实现实时高清视频转码[EB/OL].[2010 -10 -20].http://article.ednchina.com/CE/20080101074500.htm.

[2]Texas Instruments.DaVinci technology background & specifications[EB/OL].[2010-11-20].http://focus.ti.com.cn/cn/general/docs/lit/getliterature.tsp?literatureNumber=sprt401a&fileType=pdf.

[3]成嘉,张文雄,李善劲.基于达芬奇技术的H.264视频编码器的实现[J].电视技术,2007,31(12):34 -36.