4×4单元面阵自适应天线系统的设计与实现

2011-07-31汪万维胡铁乔

汪万维,胡铁乔,夏 冬

(中国民航大学天津市智能信号与图像处理重点实验室,天津 300300)

平面阵列是实际应用最广泛、最有效的天线阵列,相对于线阵和圆阵来说,其相对面积较小,一次采样的数据量大,受频率漂移的影响小,数据失真小。但由于计算量大及模型的复杂等原因,一般来说都用线阵模型来进行研究。随着大容量高速计算机的出现,为科学研究提供了有效的工具,计算量已经不再是主要问题。

自适应天线在天线阵列的基础上,为移动通信系统设计提供空间信号处理的自由度,从而可使系统性能得到显著提高。它利用阵列天线波束的方向性,通过自适应波束控制,使波束对准目标方向,自动跟踪用户目标的移动,使零陷对准干扰方向,并可自适应电磁波环境的变化,优化天线阵列方向图,从而增强有效信号,抑制同信道干扰和多址干扰,达到显著提高信干比,增强通信系统容量的目的。自适应天线技术的核心是自适应波束形成算法,考虑目前硬件水平和相关算法硬件实现的难易性,本文选用基于训练序列的LMS[1]算法,实现在需要的通信方向接收信息,同时在干扰方向形成波束零点,实现抗干扰通信。

1 天线阵列模型及自适应算法

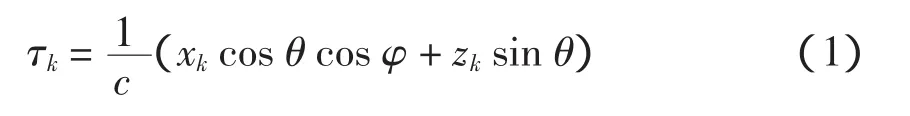

系统天线阵列由M×M个阵元组成,几何关系如图1所示。以阵列左下角的阵元为参考点,x、z轴上分别有M个间距为d的均匀线阵。另假设信号入射方位角为φ,俯仰角为θ,其中方位角表示与x轴的夹角,则信号s(n)入射到第k个阵元上引起的与参考阵元间的时延[2](下式中c为光速)为

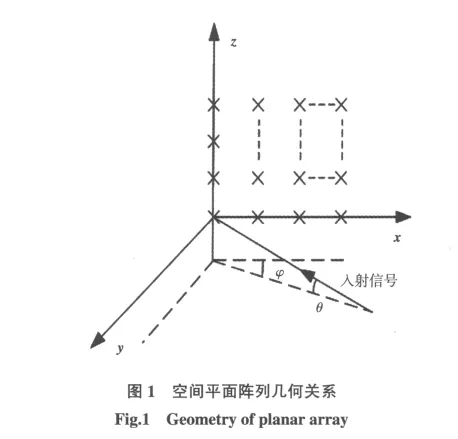

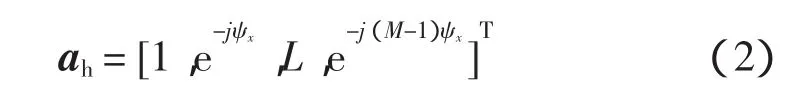

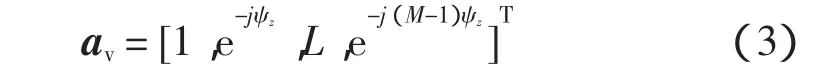

阵列水平方向导向矢量为

竖直方向导向矢量为

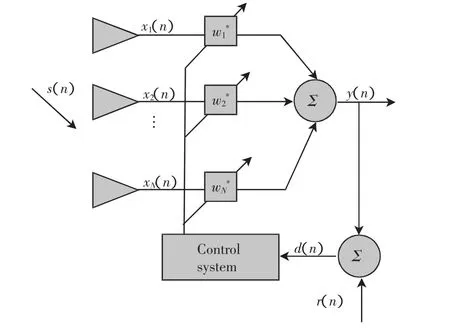

自适应阵列结构如图2所示,设阵列输入量为

式中N=M×M,自适应加权系数为

阵列输出为

LMS算法基于最小均方误差准则,r(n)为期望信号,d(n)为误差,μ为迭代步长,其迭代公式为

图2 自适应阵列系统结构图Fig.2 Structure chart of adaptive array

2 系统设计

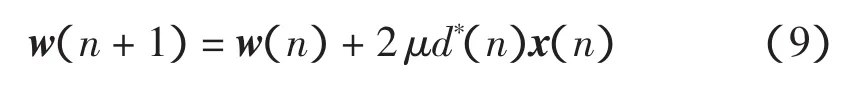

4×4单元面阵接收16路射频信号经过下变频处理后到50MHz中频,再经过40MHzA/D采样到10MHz中频后进入搭载Ti公司TMS320C6416 DSP芯片[3]和Xilinx公司XC4VSX55 FPGA芯片[4]的处理板卡,主要编程语言为C和Verilog。信号处理流程如图3所示。

为了保证本地载波与发射频率一致,在FPGA中采用二阶Costas环对载波频率进行跟踪,然后进行滤波抽取。DSP中采用FFT变换[5]寻找参考信号同步头的起始位置,再通知FPGA中的LMS算法更新权矢量,该矢量即反映了信号及干扰的来向。16路数据在权值作用下合成1路信号,并在FPGA中完成解扩后送入DSP,在DSP中完成误码率检测。为了便于结果输出和系统工作状态监视,将同步头位置、功率以及误码率通过与DSP相连的串口进行输出。PC机通过此串口接收DSP发送过来的数据,通过VC编程实现界面将结果进行实时显示。下面将对系统实现关键技术进行详细阐述。

图3 系统信号处理流程图Fig.3 Flow chart of signal processing

1)位同步头检测

接收数据采用扩频体制结构设计,用户数据和参考信号采用不同扩频码,因此它们之间的互相关很低。将接收到的数据流对训练序列求相关得大值所对应的位置即为同步头位置。由于相关计算量太大,硬件采用FFT变换实现。

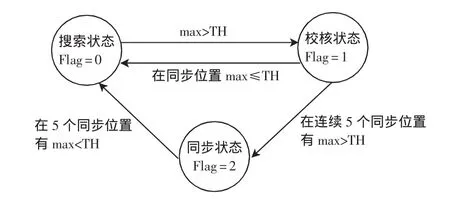

为了实现可靠位同步,用变量Flag来标识位同步状态。Flag为0时标识搜索状态,若相关值max大于门限值TH,表明已搜索到同步头,则将变量Flag置1,进入校核状态,若连续5次在相同的位置收到训练序列,则说明该同步头有效,Flag置2,进入同步状态,如图4所示,同时通知FPGA调整位同步进行LMS算法更新权值。

图4 位同步状态转换示意图Fig.4 Bit synchronous state conversion diagram

2)载波同步

考虑环路性能和硬件实现难易性,系统采用二阶Costas环[6]。环路主要由 NCO(数控振荡器)、LPF(低通滤波器)、PD(鉴相器)及环路滤波器(LF)组成。为了降低噪声对环路系统的影响,降低FPGA芯片的功耗,本文对环路数据依次进行了2倍移位抽取和4倍抽取,其原理结构如图5所示。

图5 数字Costas环结构图Fig.5 Structure diagram of digital Costas

本地NCO采用基于查找表的DDS[7](直接数字频率合成)设计原理,频率控制字计算如下

系统参考输入时钟频率fclk=40 MHz,相位累加器位宽N=32,为了得到10 MHz中频频率,控制字Δθ′=1 073 741 824,同时LF输出控制字为ΔΦ,NCO输入控制字为Δθ=Δθ′+ΔΦ。ΔΦ控制NCO的输出频率不断向减小跟踪误差的方向调整,直至跟踪上10 MHz中心频率的输入信号。

3)LMS算法实现

FGPA收到DSP传送的位同步调整参数后,实时调整DPRAM读地址计数器以达到数据头对齐以便进行权值更新。LMS为递推算法,若读取数据x(n)的时钟选取20 MHz,则完成一次完整迭代估计需要10个时钟,为了保证在下一个同步头到来之前计算出权值w,计算时钟应为读数据时钟的10倍,即200 MHz。用如此高的频率来运算,实现风险较大,而且没有必要。故将数据读取时钟变为2 MHz,而运算时钟则采用20 MHz,这样在10个数据块时间后即可得到权值w,满足系统要求。

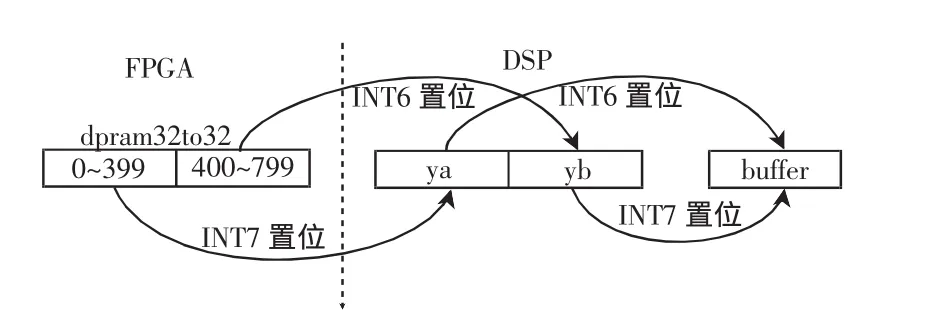

4)DSP与FPGA之间数据交换

高速 64位宽度的 EMIF-A和 16位宽度的EMIF-B扩展存储器接口,最高吞吐能达到1064MB/s。多达64个独立通道的EDMA数据传输控制器。DSP的EMIF接口通过64位的数据总线与FPGA和SDRAM交换数据。系统中FPGA映射在DSP的256M大小的ACE3空间,SDRAM映射在ACE0空间,NOR FLASH映射在BCE1空间。为了提高工作效率,系统采用乒乓方式传输y(n)数据,如图6所示。FPGA中使用1个深度为800、32位宽的DPRAM保存y(n)数据,前一块(0~399)填充满后,向 DSP发出中断 7,则DSP利用EDMA将该块数据搬移到内容缓冲区ya中,同时将yb中的数据传输到缓冲区buffer中,准备进行其中的数据进行圆周相关。在DSP从FPGA读取第一块数据的同时,FPGA继续向FPGA的第二块缓冲区(400~799)写入数据,DSP将yb中的数据搬移到buffer中(利用DSP_blk_move函数)。

图6 DSP与FPGA采用乒乓方式交换数据示意图Fig.6 Data exchanging diagram with ping-pong of DSP&FPGA

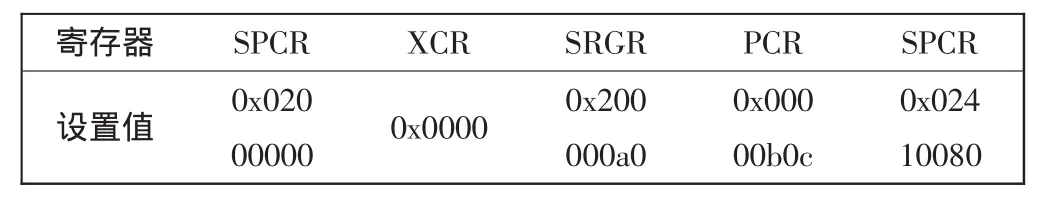

5)异步串行通信

DSP中利用片上多通道缓冲串行接口(McBSP)和增强型直接存储器存取(EDMA)实现异步串行通信。将误码率、位同步头位置、第一路权值以及合成一路后信号功率等参数通过串口送出,以便PC机接收显示。异步串行通信采用起止式格式,起止为扩展为0x0000,停止位扩展为0xFFFF。中间数据位为0时扩展为0x0000,为1时扩展为0xFFFF。待发送数据帧格式为:3 字节同步头(0xE1,0x5A,0xE8),2 字节误码率,2字节合成功率,4字节第一路权值实部和虚部,2字节同步状态,共13字节大小,串口传输速率为115.2 kbps。McBSP相关寄存器的设置值如表1所示。

表1 McBSP相关寄存器的设置值Tab.1 Register settings of McBSP

3 系统测试

1)位同步头检测测试

参考信号与数据采用不同的扩频序列,因此它们之间的互相关很低,对收到的数据流对参考求相关求得最大值如图7所示:每60个点一个峰值,每个峰值对应一个参考信号。

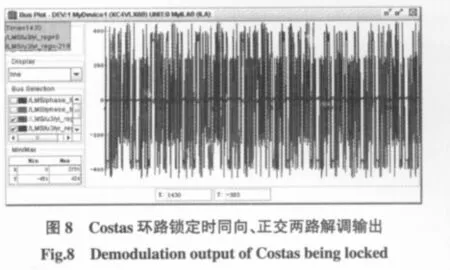

2)载波同步测试

二阶Costas环路锁定时,蓝线所表示的同向支路幅度远大于红线所表示的正交支路幅度,如图8所示。

3)系统性能测试

系统从波束跟踪、抗干扰、误码率等三个方面验证其性能。测试环境为装有吸波材料的暗室,发射信号天线和接收信号天线正对,距离为7.2 m。干扰为单载波干扰,信干比SIR=-10 dB,与信号夹角为30°。由于实验条件有限,目前只考虑水平方向干扰抑制情况。

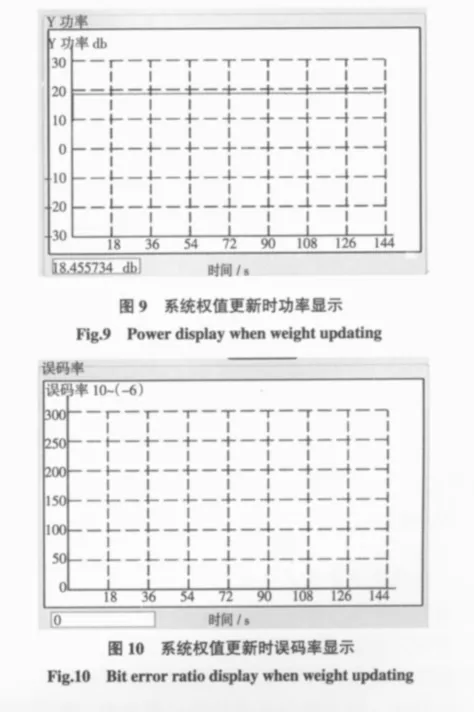

跟踪测试时,算法实时更新,接收天线置于转台上,以约1°/s的速度从-90°转至90°。实时记录误码率以及系统进行算法更新后合成1路信号功率。

由图9可以看出,信号来向发生变化时,系统输出功率恒定,表明系统实时跟踪上发射信号。同时系统误码率为零,如图10所示。

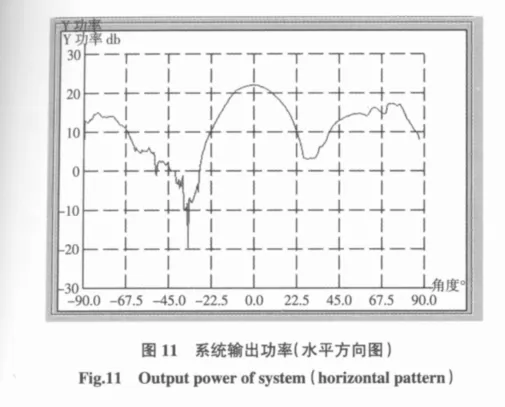

系统抗干扰性能测试时,发射信号和干扰,接收天线正对发射信号,系统权值实时更新,通过修改DSP中参数设置,使得在某一时刻系统停止权值更新,保留最后时刻权值,同时去掉干扰。接收天线在转台上以约 1°/s速度从-90°转至 90°,观测系统输出功率。

由于实测过程中,转台转速存在一定误差,故图中横坐标会与实际信号和干扰所对应的角度会有一定的误差。在0°左右方向形成主波束,在-30°左右形成零陷,系统达到设计要求。

4 结语

系统为一套完整接收系统,中频信号经过数字下变频后变为零中频信号,为了实现可靠位同步,采用FFT变换寻找位同步头。根据算法及FPGA特点,通过合理选择信号处理时钟来使系统达到最优处理性能。根据LMS算法特点及其硬件实现难度,系统采用目前流行的DSP&FPGA架构平台,既满足系统对实时性的要求,又能实现零误码率通信。

[1]龚耀寰.自适应滤波——时域自适应滤波和智能天线[M].北京:电子工业出版社,2003.

[2] 王永良,陈 辉,彭应宁,等.空间谱估计理论与算法[M].北京:清华大学出版社,2004.

[3] 卞红雨,纪祥春,乔 钢,等.TMS320C6000系列DSP的CPU与外设[M].北京:清华大学出版社,2007.

[4] 薛小刚,葛毅敏.Xilinx ISE 9.X FPGA/CPLD设计指南[M].北京:人民邮电出版社,2007.

[5] 郑君里,应 启,杨为理.信号与系统[M].北京:高等教育出版社,2003.

[6] 张安安,杜 勇,韩方景.全数字Costas环在FPGA上的设计与实现[J].电子工程师,2006(32):18-20.

[7]Xilinx技术手册[G].2005.