Sip协调设计和PI分析(5)

2011-07-30蔡积庆编译

蔡积庆 编译

(江苏 南京 210018)

1 PDN研究方法

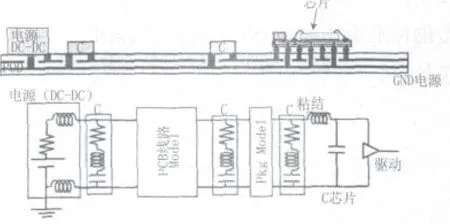

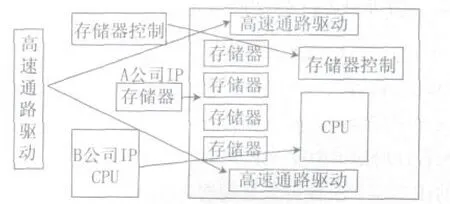

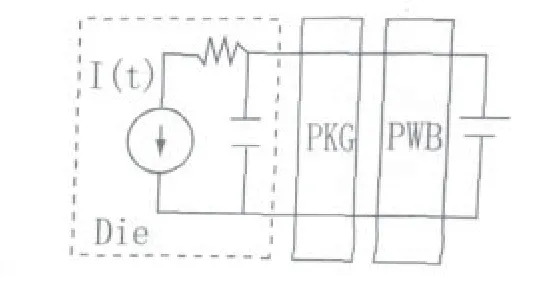

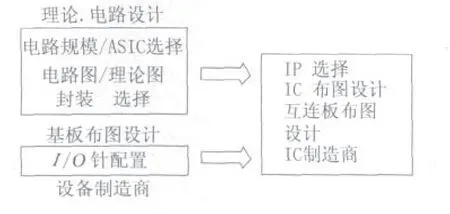

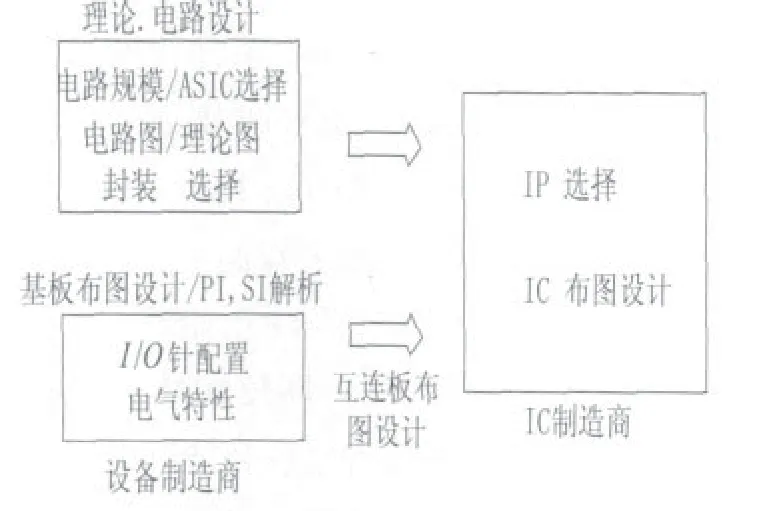

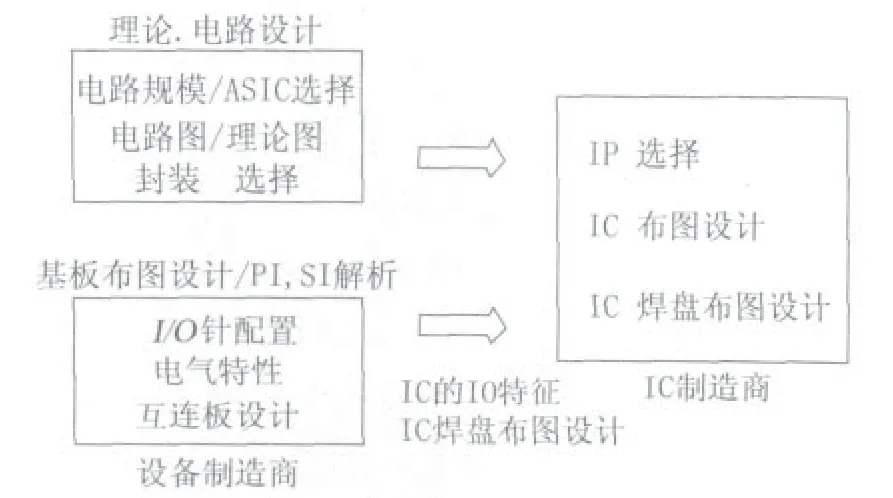

如图1所示的电源供给网络(PDN,Power Delivery Network)中,在各种情况下都有C和L成分,C和L分散存在于PCB封装和IC芯片中。这样的PDN解析必须整体的解析电源,PCB,封装和芯片。而微小的L成分随着版图设计的大小或者发生场所而变化。PDN分析跨越布图设计和分析,电源,PCB,封装和芯片,所有大的协调设计是不能解决的。包括基板(PWB),封装(PKG)和芯片(Die)的全部布图设计中,采用相同的数据库的整体分析虽然是理想的(图2),但是现实存在许多障碍而不容易实现。对于IC的内部信息来说,它是高度机密性的知识产权(IP)信息,是不能流出外部的。尤其是IC制造商在许多情况下是协调设计不可缺少的信息。大多数的系统IC或者ASIC,如MPC或者DDR接口(Interface)或者各种功能块(Block),都是购买由其他公司设计的具有知识产权(IP)的IC功能块而组合成LSI,如图3所示。关于这些功能块,设计成IP的各个公司拥有知识产权或者详细的内部信息,系统IC制造商是不能获得内部的详细信息。IC的消耗电力甚至连各种IP的工作模式(Model)的消耗电流都不能正确把握。

图1 PPN(Power Delivery Network)

图2 相同数据库化

图3 系统IC是由不同公司的IP构成的

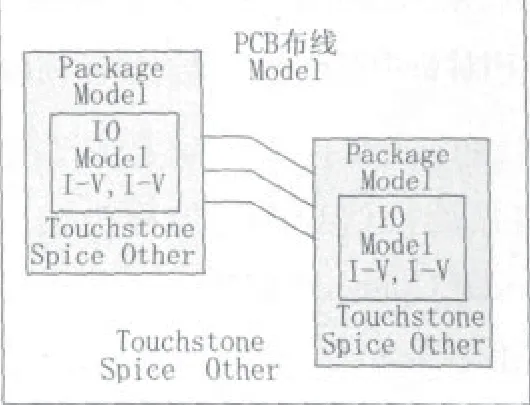

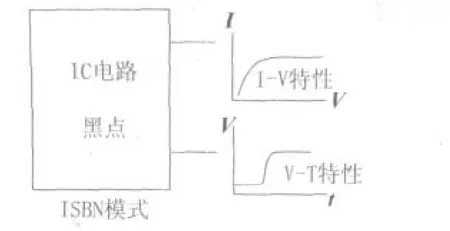

同样,至连板的布图设计信息或者封装技术的信息如果属于IP,那么它们也是不能向外部流出的信息。现在包括至连板的设计在内的封装的方法或者技术都含有高度机密性的技术。在这种情况下,IC,至连板和PCB往往由不同的公司进行设计,在协调设计中存在着各公司的利弊或者知识产权的问题,难以简单共享各种详细信息。在这种环境下,PI分析如果没有以布图设计为主的层构或者粘结/线的信息等许多内部信息,则无法进行高精度分析。如果信息的共享是由IP的障碍产生的,则难以获得实效的PI分析。但是今后SSO的问题日益重要,因此PI分析的必要性日益增加。一方面要保护布图设计信息等知识产权,另一方面要共享旨在PI分析的信息的业界标准还在开发中。现在开发了IBIS模式,在信号完整性(SI,Signal Integrity)分析中既没有展示IC内部信息又可以获得SI分析所需要的信息。实际上即使对于继SI解析之后的PI分析中,以IBIS共同体为中心的标准已经发展为PI分析用的信息的标准化。IBIS对于业界分析模式的标准化具有很大的影响力。高速传输电路分析的封装模式或者PWB的模式所使用的S参数的标准形式(Touchstone Fileformat),图5ibis制成了如图4所示的格式。

图4 检查标准规格(IBIS)

2 协调设计标准化的动向

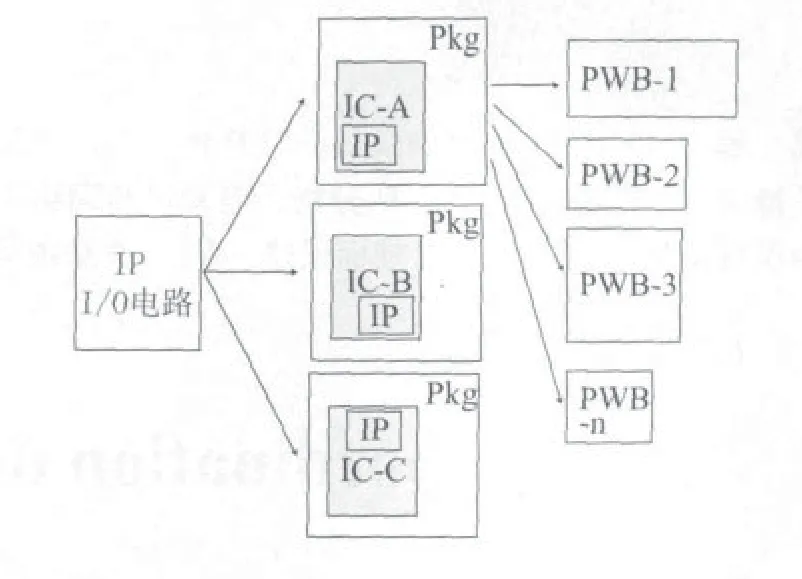

为了分析PDN,需要许多信息,这些信息包括PWB(PCB)设计,封装内基板设计,IC的I/O电路或者电源电路设计各种领域。以原封不动的保持各种设计的知识产权(IP)且共享PI分析用的必要信息的IBIS为首的各种工具制造商等进行了数据的标准化。与SI分析同样,PI分析也是最终的系统设计者进行的业务。IC或者封装是从球(Ball)到芯片焊盘(Die Pad),从芯片焊盘到芯片(Chip)内部电路的分析,而从电源到球的PWB上的电源供给线路是由系统设计者设计。另外,芯片或者封装作为部件是数个系统共同使用的,但是PWB上的每个系统有所不同,因此分析也是在每种PWB上进行。如图5所示。

图5 许多PWB使用同样的IP或者IC

PI分析用的数据或者格式(Format)的共同化目的旨在把芯片的信息和封装的信息传达给PSW设计者(解析担当者)。如果芯片或者封装布图设计有不清楚的,系统设计者把正确实行PI分析用的信息传达到IBIS委员会或者工具制造商进行研究。IBIS一直致力于以SI分析为目的模式的标准化,而最近积极推进PI和EMI解析的模式的标准化。

3 IC的信息

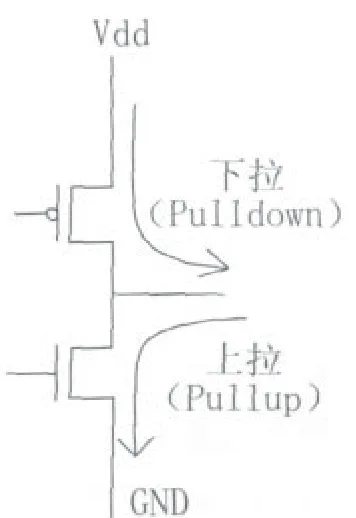

IBIS格式仅仅定义SI分析用的驱动器和接收器(receiver)的特征而没有电路信息在原理上如果使用这种IBIS定义,还要分析驱动器的同时开关电流变化,如图6所示。然而大多数实际的IC的驱动电路不仅具有采用IBIS定义的驱动器,而且还含有旨在驱动那个驱动器的另一级驱动电路,如图7所示。有时还附加其他电路。

图6 I-V特性中看出了驱动电流 I-V特性中看不出第1级的电流

图7 2级的驱动电路

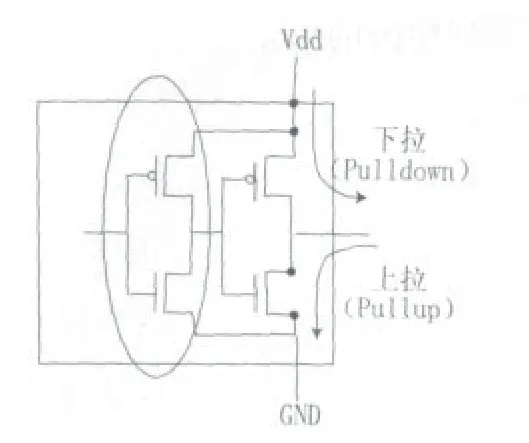

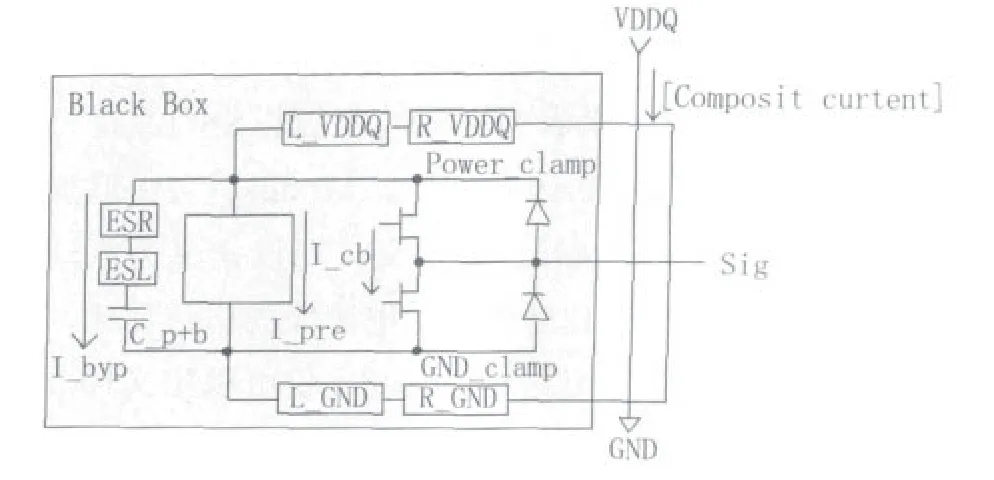

具备这些附加电路的驱动器中,采用IBIS的驱动特性分析的结果表明更多的电流以SSO流过。因此,IBIS的最新Version5.0中,Model是文中追加(Composite Current)这种定义,可以定义为驱动器的“V-T”特性变化时流过IC电源线的电流变化,如图8所示。如果使用这种定义,不仅可以定义10,而且还可以定义包括负载电路的IC的消耗电流的变化。虽然没有记述IC的内部电路,但是IC的消耗电力的变化可以传达给PI分析者。

图8 [Composit Current]定义

PDN分析中IC的歌驱动器上附加的小型旁路(By-pass)电容(On-Die Capacitor)效果很大。如图9所示,在IC的内部可以制造数nF程度的小型电容(On-Die C)作为驱动电路的一部分。这种On-Die C作为分析是外付的元件虽然可以简单的附加,但是由于IC,有结合的有附加的,因此有各种值等。

图9 On Die C

4 互联板的信息

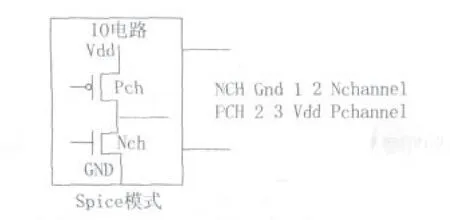

没有互联板的布图设计信息,传输电路分析用的信息定义的格式可以采用标准化的R.L.C等效电路或者S参数。PI分析的模式也可以原封不动的使用这些模式记述。IBIS,采用两种模式记述加上Spice记述正在极力的标准化。IBIS和Spice是相反的考虑,最初Spice模式还没有问世就制定了以半导体制造商为中心的IBIS模式,因此IBIS不同于Spice格式。图10表示了正确理解的IBIS模式定义。IBIS之所以研究Spice模式,只是因为封装或者等效电路模式这种抽象的模式。制定IBIS的另一个理由是Spice模拟器已有数种产品,还有许多“方言”。即使Spice模式的模拟器之间也没有互换性,同样的模式不能采用不同的Spice模拟器进行分析,分析结果不同,鉴于这种状况;制定了没有“方言”的IBIS格式。此后采用IBIS制定的Spice格式准备了许多没有方言的Spice。

在信号分析情况下,基本上把IC的芯片焊盘与PWB布图设计的针(球)对的连接,在电源和GND(地层)的情况下,IC芯片和PWB的元件针都有许多芯片焊盘和针在同一电路上并联连接。作为更为复杂的问题,由于针位置或者芯片焊盘位置而使线路途径或者连接的对象很少,有相同的,如图11所示。PI分析中,通常的电路明细单(线路连接信息)那样的全部GND或者全部电源作为共同连接的同一电路来处理,如图12所示。PI分析中,每种线路途径或者每面上各种特性不同,布图设计中连接的电源和GND有必要分析每种路线途径的特别特性,如图13所示。

图10 IBIS的模式定义

图11 即使连接电流也采用其他途径流动

采用线路途径单位来区别具有许多针的同样电路,并制作连接信息的功能称为模式连接草案(MCP,Model Connection Protocol),电路记述格式出现标准化动向。美国PI模拟器制造商Siglity公司提倡MCP,采用归纳许多针之间的连接信息定义的格式,其他EDA(Electric Design Aualysis)制造商也开始支持这种格式。

5 电流模式

采用IBIS新定义的[复合电流]([Compsite Current])与[V-I]特性同步,定义IC的电流电源对于时间的变化,如图14所示。定义这种电流的模式称为电流模式。对于时间轴的电流的定义或者对于时间轴的电压的定义使用Spice模拟器中电流源或者电压源的定义。如果使用这样的电流模式来定义IC的消耗电流或者它的变化,那么不仅SSO分析而且IC的热分析或者电源设计都是非常有效的。这种的电流模式如果作为知识产权(IP)信息赋予IC内部的各种IP块(Block),那么系统IC设计者就可以非常有效的进行IC的省能设计,正确把握IC的消耗电力,如图15所示。这种电流模式虽然没有展示IP或者IC内部的电路或者布图设计和技术的信息,但是公开了IP或者IC的正确消耗电流的信息。为此定义IP块或者IC的消耗电流的电流模式的标准格式计划的活动正在展开。基本上是Spice的电流模式定义,但是附加怎样的附带信息还有不少混乱。例如IBIS中作为PI解析的附着功能只是追加了一部分SI分析用模式,没有消耗电力解析用的。另外IBIS是系统设计者用的,而IC内部的设计者并不太熟悉。

图14 [Composit Current]定义的电流

图15 IC的电流模式

IC用EDA制造商Apache公司附加了成为CMP(Chip Power Model)的电流模式格式或者连接信息等的信息,提出了LPM(LSI Power Model)等若干格式。关于IC的消耗电流,电流模式的讨论日益增多,旨在要求增加模式的标准化。正确掌握PI解析,省电设计和电源设计等IC消耗电力的活动及其标准化的活动正在加速。模式的标准化,流动和协调设计的普及仍然是今后设计的潮流。

6 SOL和互联板设计

IC在以MCP或者存储器,芯片单元为首的标准部件的时代中,作为IC部件的IC封装和IC芯片视为1个整体。当然IC用户的设备制造商还没有考虑IC封装的设计等。此后考虑SOC的多起来了,设备制造商设计了ASIC,但是毕竟还是理论设计,IC的布图设计或者封装设计是IC制造商的工作。在这个阶段中,设备制造商是从基板设计的安排到IC的针排列的布图设计要求,但是互联板的布图设计是IC制造商的工作,如图16所示。此后由于系统IC的增加,信号的高速化和IC消耗电力的增加,基板与封装有必要进行整体的分析研究。这就是如图17所示的协调设计。结果使设备制造商一直关心到封装内的互联板的设计。今后降低了设备制造商的互联板设计上的篱笆,与基板设计同样,互联板的设计也是由设备制造商进行,进行互联板和基板的整体设计和整体分析,如图18所示。

图16 ASIC的设计

图17 协调设计

图18 互连板设计由设备制造商进行

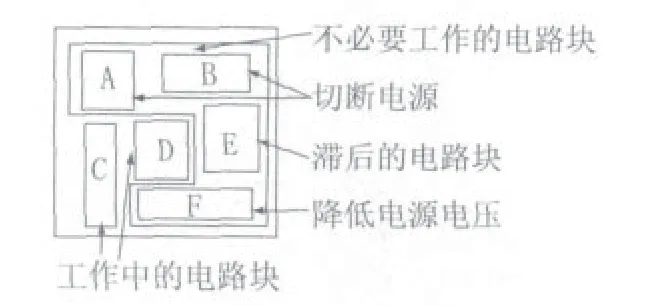

现在ASIC的集成度不断提高,ASIC容纳的电路规模日益增大。然而如果全部电路都工作,则会增大IC的消耗电力和发热,从而增大互联板的设计或者封装的热对策的费用。因此致力于IC的省电设计的普及。使那些IC没有工作的电路停止工作,从而降低IC的电力消耗,如图19所示。

图19 IC的省电设计

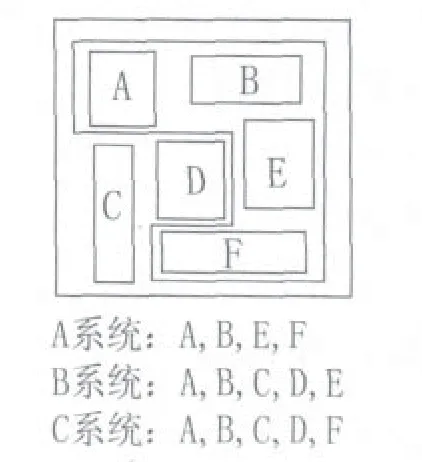

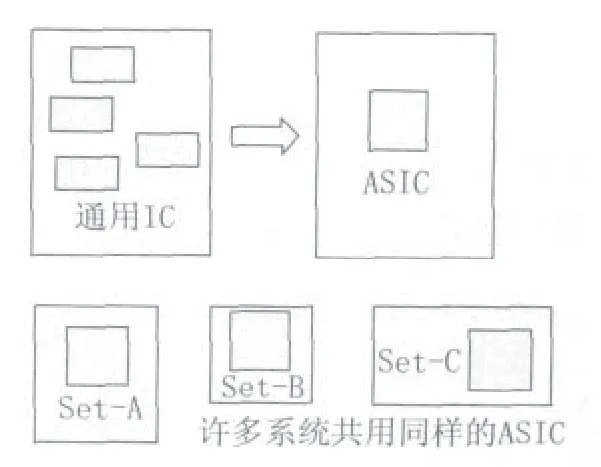

另外,IC的集成度提高,ASIC所容纳的电路规模增大到系统所需要的电路规模以上。由于速度或者IP而需要使用最新的ASIC,但是会白白浪费了电路容量。因此把类似的其他系统使用的功能一块儿纳入ASIC中,数丁系统共用同样的ASIC。

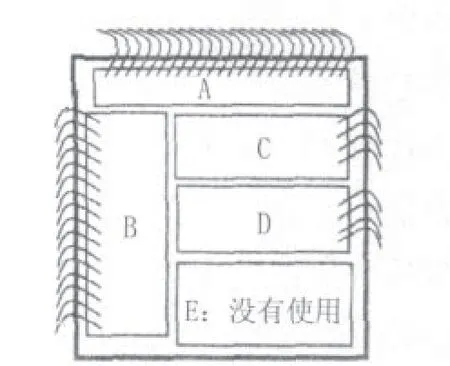

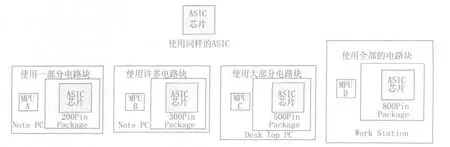

由于IC芯片的设计化费很大费用,把全部功能一次设计成增剂的IC,根据系统使用需要的功能块,不要的功能块不使用,如图20所示。如果制造这种通用ASIC,一个ASIC可以为许多系统所共用,由于大量使用同样的ASIC,因此可以降低每个ASIC的开发费用或者制造成本。由于没有使用电路块的信号没有必要与基板连接,因此可以减少封装的针数,如图21所示。还在从特定系统最佳化的ASIC到数个系统共用的ASIC的思想转变,如图22所示。

图20 根据系统区别使用的电路块

图21 去除那些不使用的电路块的信号针

图22 ASIC从专用到共用

如果提高ASIC的集成度,则是与省电设计实用化相反的思想。如果是这种ASIC,设备制造商使用通用ASIC,由互联板和基板组合成各种设备,可以设计成许多系统,如图23所示。这种设计中互联板的设计当然是由系统制造商完成。中规定了信号针的配置,而ASIC等系统IC中,因为随着基板布图设计而变化,所以有必要与基板设计

图23 变更同样芯的封装基板

7 BGA封装的设计

BGA封装的设计有很多要素,而主要的要素是PI(电路供给电路,PDN),热,针布图设计和信号线路等。其中使用消耗电力大的BGA大规模LSI中PI是一个特别大的问题。

互联板的线路怎么稳定的进行电源供给在某种程度上取决于电源/GND的针数和互联板的层数。另外,电源/GND的稳定度对于线粘结安装或者倒芯片安装或者芯片的安装方法也指出了方向。尤其是针数和针节距决定了封装的大小,如图24所示。同样还从LSI的消耗电力来进行热设计的研究。当然倒芯片安装的芯片散热特征优良。许多情况下根据芯片的消耗电力来考虑芯片的散热性,在芯片的设计阶段取决于线粘结安装或者倒芯片安装。在封装的设计阶段进行封装的针数和针节距以及封装尺寸的研究。如果规定了封装尺寸,散热器或者密封,因为根据封装规定散热量,因此也可以根据消耗电力决定散热片的设计。互联板的设计也是电源/GND供给途径的重要事项,而信号线路当然重要。为了信号线路,必须预先规定信号针配置。在存储器或者MPU和图解控制器(Graphic Conltroller)等通用IC协调。如果规定了针配置或者某种程度上规定了信号线路,则可进行电源/GND的平面设计。为了使平面设计的信号回路通路(Return Path)稳定,信号线路的正下方必须没有切断或者端面。

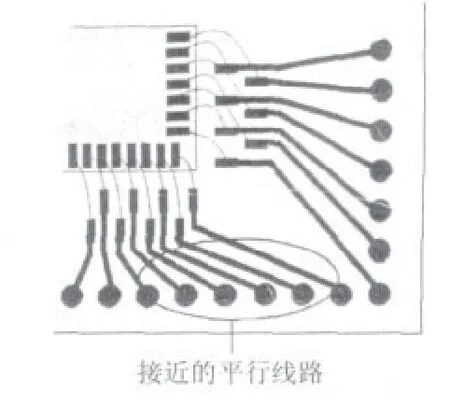

图24 针数和针节决定了封装的尺寸

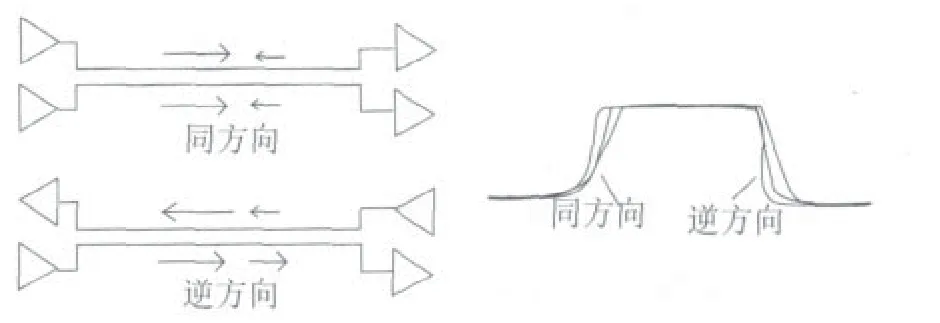

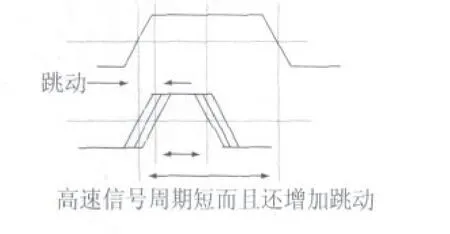

互联板的线路设计应当注意始终(Clock)信号等高速的重要信号线路,即使DDR存储器的总线(Bus)信号等高速并联信号也必须注意串联噪声。因为互联板内线路短而微细。即使平行线路,串联噪声也没有什么大的影响而无须注意,但是随着DDR3等信号的高速化,互联板内线路中发生的串联噪声不可忽视,如25所示。串联噪声在高速信号中表现跳动(Jitter),如图26所示。如果信号变成高速,因为定时安全系数(Timing Margin)小,尤其由于串扰噪声而使跳动变大,往往发生了重定时问题,如图27所示。因此,不仅对于PCB线路而且对于互联板线路都必须充分注意串扰噪声的适应性。

图25 必须注意互连板线路的串扰噪声

图26 串扰噪声表现出跳动

图27 高速信号中定时的重要性

8 模拟器和模式

模拟时分析使用的模式是决定精度的最重要问题。传输线路模拟器使用的模式大致分为(1)IC的驱动器,接收器模式的IO模式;(2)以终端电阻为主的分立元件模式;(3)PCB和互联板的线路图形模式。称为IO模式的IC的驱动器,接收器模式一般使用称为IBIS模式的模式形成和称为Spice模式的模式形式。IBIS模式中驱动器和接收器的电路作为黑点(Black Spot)定义为输入输出的电流-电压特性(I-V特性)和输出波形的上升边,下降边特性(V-T特性),如图28所示。Spice模式中驱动器,接收器的内部电路采用原来的定义,如图29所示。

图28 采用特性定IO模式

图29 采用电路定义IO模式

IO模式是IC制造商提供的,PCB的线路模式由于PCB的完全不同而必须由设备制造商设计PCB。为此传输线路模拟器附加了简便的模拟PCB线路模拟分析功能的模拟器功能。使用这种简线路模式分析功能,模拟器一边模拟化各次的线路一边分析进行这种PCB线路图形的模式化的软件称为场解算器(Field Solver)。

BGA封装内的互联板线路或者PCB的线路图形的模式到现在尚未严密的定义。但是IC的消耗电力日益增大,SSO的问题日益重要,信号的高速化与PCB或者互联板的线路模式的误差时解析结果的影响很大。因此传输线路模拟器附录的简单场解算器难以适应PCB或者互联板的模式,需要使用专用的场解算器。

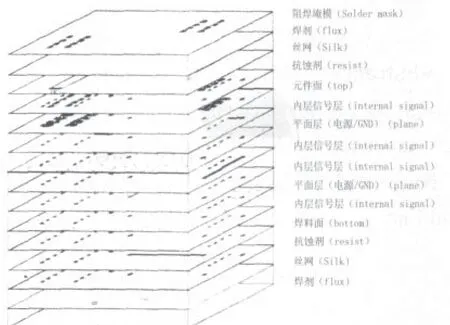

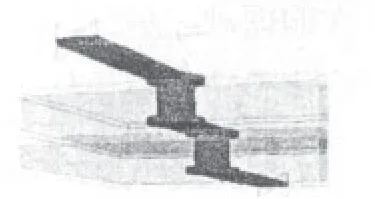

迄今的场解算器与高精度场解算器的最大不同在于三维分析功能,在PCB或者互联板的设计中,普通的基本上每层具有二维数据的构造中只有层的积层序号和层的厚度信息。这样的PCB或者互联板的布图设计CAD作为二方向的信息,由于只有层信息而称为2.5维数据,如图30所示。线路具有严密的蚀剂变形或者导通孔等而为构造,在2.5维的数据构造中线路的特性抽出时产生细小的误差,如图31所示。非常高速的信号传输线路解析时由于这么细小的误差成为解析误差的原因,因此需要三位场解算器而不是2.5维解算器,如图32所示。另外由于平面层的划痕或者导通孔等原因线路特性会微妙变化。为了解析线路导通孔的3维关系,抽出正确的线路特征,必须使用PCB的正确的三维信息和三位场解算器。

图30 PCB数据2维数据十层结构

图31 导通孔3维构造

图32 3维解算器

[1]前田真一. Sip协调设计こPI解析满座[J]. ェレヶトロニヶス实装技术, 2011,2.

[2]前田真一. Sip协调设计こPI解析满座[J]. ェレヶトロニヶス实装技术, 2011,3.