基于SOPC的嵌入式数据记录仪设计

2011-06-13张娟娟蒲南江

张娟娟,蒲南江

(中北大学 仪器科学与动态测试教育部重点实验室 山西 太原 030051)

0 引言

本文介绍一种基于FPGA的嵌入式数据采集系统的控制电路、数字信号处理模块、信号的显示模块以及接口电路的设计。这样可以将一个数据采集系统做成一个灵活完整的可编程片上系统SOPC,与以前的专用集成电路(ASIC)相比,SOPC具有更大的灵活性,基于SOPC的设计可以充分满足数据采集器高可靠性、灵活性、前端智能化的要求,同时降低了成本,拥有广阔的市场前景[4-5]。

1 整体系统框图

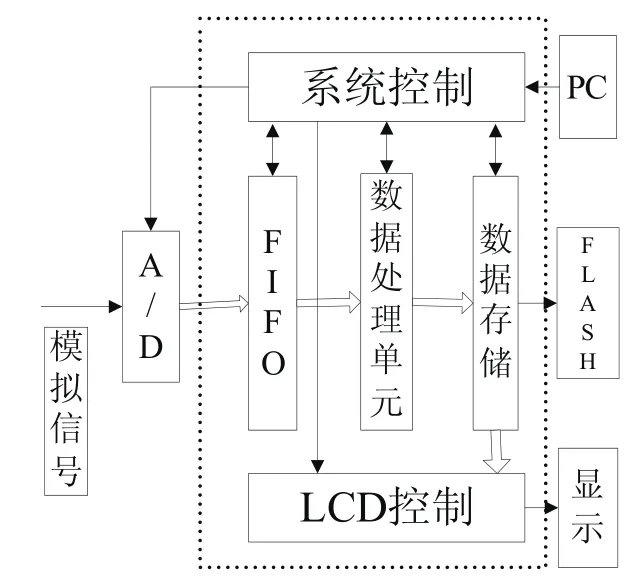

以FPGA为载体构建SOPC系统作为控制平台,其外围电路由调理单元、控制单元、存储单元、显示单元组成。框图如图1所示。

图1 系统原理框图

控制器控制前置调理电路、AD采集模块、FIFO数据缓存模块、Flash存储器在各自时序下工作,完成对每次试验数据的采集与存储。

前置调理电路:信号调理在数据采集系统中很重要,不同的输入信号,所需的前端预处理技术不尽相同,通常包括放大、过滤、隔离、激励、线性化等,本电路主要完成对数据采集通道和各通道信号相应放大倍数选择,满足AD采集模块模拟信号输入要求。

A/D的控制:控制器根据AD的工作时序,控制AD在不同采样频率下工作,完成数据的采集。

FIFO缓存控制:配合前端AD采集电路,控制缓存器工作时序,对数据缓存,之后对数据的进行处理。

数据处理单元:控制器控制时序、将FIFO中的数据进行FFT运算,将结果存入存储单元,以供后续单元的使用。

显示单元:将处理过的数字信号进行频谱显示,观察其频谱特征和其他的一些特性,以进行一些控制措施。

2 系统工作原理与功能实现

2.1 数据处理模块设计

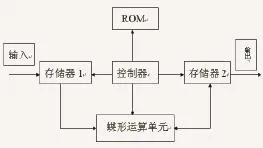

XILINX公司的Spartan 3E 系列的XC3S500E FPGA芯片内嵌20个硬件乘法器,可以实现FFT算法用以满足基于FPGA的数字信号处理的设计方法。FFT的硬件实现结构如图2所示。

图2 FFT实现流程

图2是FFT的总体结构框图主要包括4部分:存储器、蝶形运算单元、控制器、ROM。图中,蝶形运算单元选为基2或者基4运算,ROM中存储的是N点旋转因子。控制模块产生所有的控制信号以及存储器1和2的读写地址、写使能、运算模块的启动信号及ROM的读地址等信号。存储器1作为当前输入标志对应输入N点数据的缓冲器,存储器2作为中间结果存储器。采用两个存储器可实现数据的流水线操作,即在向存储器2中写入数据的同时,可以从存储器1中读出下一组的输入数据。

整个系统的工作流程是:外部输入数据在时钟的控制下,写入存储器1中,当控制器接收到存储器1准备就绪的信号后,控制器使能存储器1和旋转因子存储器的读取信号,读出存储器1中相应地址的数据与ROM中的旋转因子数据进行蝶形运算;每一级运算的中间结果都写入存储器2中,在图中各种使能信号和数据的紧密配合下,最后将FFT计算结果输出。蝶形运算单元是FFT处理器的基本单元,基2蝶形运算单元是由一个复数加法器、一个复数减法器和一个旋转因子复数乘法器组成,所以在FFT中设计一个高效的乘法器可以提高FFT的计算速度,提高运算效率。采用一种高效乘法器算法来设计实现旋转因子复数乘法器,由于XILINX公司的FPGA内置有高速乘法器模块,选用其内置乘法器来完成乘法运算单元的设计,调用CORE Generator核生成器,可以进行FFT的设计。经过处理的数据通过FPGA控制显示被采集的信号的频谱特征曲线或者其他特征数据。

2.2 显示单元

为了能够对采集的信号的频谱进行实时显示,需要将经过处理的数据直接送入液晶进行显示。一般采用单片机进行控制,而且现在大多数液晶的控制器支持复杂的指令,也更适合在单片机下使用。但是液晶的读写本身就受时序的控制,这就为使用FPGA控制提供了方便,也就是说,无论哪种类型液晶,只要明白了液晶控制的时序,就很容易控制它。对于液晶显示方式,先计算出波形在液晶屏幕的位置,通过对液晶的操作时序,将所需显示的像素点一个个显示到液晶屏上,当一屏显示结束时就有完整的波形显示出来。本设计中采用分辨率为320×240的单色液晶显示屏就可以达到设计中显示所采集的信号频谱曲线的目的。

显示单元采用分辨率为320×240一种单色液晶模块可以用来进行频谱显示。由于本设计中FPGA所要控制的外设LCD不是较为常用的外设器件。因此,在EDK集成开发环境中,Xilinx并未提供与其相应的外设控制IP核。这就要求设计员自己开发满足设计需求的外设IP核,使FPGA内的MicroBlaze处理器软核通过总线能够实现对外部芯片的控制和读写数据。

2.3 应用程序设计

传统的嵌入式系统在程序设计上一般采用的是前后台方式或超循环方式。对于简单的应用,这种前后台方式是可以满足需求的,但是随着应用的复杂化,系统可能要同时监测/控制多个外部设备,要求较高的实时性,有多个任务要处理。如果在系统软件设计上仍然采用上述的传统方式,就会出现两个比较突出的问题。一是中断响应,一般为了保证某一项重要任务的实时性,就必须在ISR中进行较为复杂的处理,这样一来就要考虑代码重入、系统硬件堆栈溢出等问题。二是任务多,要考虑的各种可能性也多,各种资源调度不当就会造成共享数据的不一致,降低系统的可靠性,同时程序量也加大。

解决这些问题的最好方法就是使用嵌入式实时操作系统RTOS。使用RTOS可以有效的对多个任务进行调度,对各个任务赋予不同的优先级可以保证紧急任务得到及时响应。RTOS也体现了一种新的应用程序设计思想和开放的框架,降低了程序的复杂度和开发周期。系统采用uC/OS-II实时操作系统。

3 实验结果分析

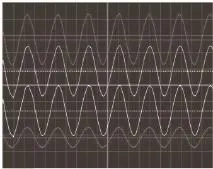

实验过程由信号发生器产生信号,系统对信号的采集图像如图3所示。实验验证得到系统最高采样速度能达到12MB/s。且能够将测量数据无失真还原,并实现了四通道波形同时显示,分别控制的功能。该模块能更方便、更直观的完成波形的比较。

图3 实验波形

4 结论

本文介绍了一种基于FPGA的嵌入式数据记录仪的实现方法,该记录仪能有效进行高速高精度存储测试,能够方便、可靠地实现对武器系统参数的测试,充分发挥存储测试技术所具有的无需引线、抗干扰能力强的优点,是解决高温、高冲击、高压环境下参数测试的先进手段,值得大力推广应用。

[1]谭斌,雷宏.基于FPGA的数据记录器数据源的研究与实现[J].电子测量技术,2006(6):4-5.

[2]刘文怡,张彦军,李海宏,谭秋林.全覆盖型弹载数据记录器的研究与实现[J].电测与仪表,2008(1):1-2.

[3]李春,吴世通,邓黎.航天器空投试验用大容量数据记录器的研究[J].航天返回与遥感, 2006(1):2-4.

[4]谭斌.数据记录器的研究与数据源的实现[D].北京:中国科学院,2006:34-37.

[5]王玲,焦新泉,甄国涌.弹载数据记录器的设计与应用[J].飞航导弹, 2010(4): 3-4.

[6]赵玉印,白玉贤,张泽宏.一种弹载数据记录器的设计[J].兵工自动化, 2004(2): 2-3.

[7]胡云峰,陈虹,刘明星,许芳.基于FPGA/SOPC的预测控制器设计与实现[J].仪器仪表学报,2010(6):1-2.

[8]于晓洲,周军,周凤岐.基于SOPC技术的阵列信息处理技术实现研究[J].西北工业大学学报,2009(2).