数字视频采集回放系统的SoPC设计

2011-06-07杨翠军曹云鹏

杨翠军,钱 敏,曹云鹏,朱 静

(苏州大学 微电子系,江苏 苏州 215021)

0 引言

由于大规模集成电路(VLSI)、计算机和通信技术的迅速发展与结合,促进了视频技术的进步与广泛应用[1]。作为逐渐取代模拟视频的数字视频越来越受到人们的关注,日益成为一种广泛应用的媒体,而其中数字视频图像采集是进行数字视频处理技术的关键[2]。本文采用SoPC技术设计了一种嵌入式数字视频图像采集方案。可编程片上系统(System on Programmable Chip,SoPC)是Altera公司提出来的一种灵活、高效的SoC解决方案,是一种新的软硬件协同设计的系统设计技术。它将处理器、存储器、I/O口、LVDS、CDR等功能模块集成到一个可编程器件上,构成一个可编程的片上系统[3]。本文利用该技术在FPGA芯片上配置NiosⅡ软核处理器及相关接口模块来实现硬件平台,并利用Altera公司的软件集成开发环境NiosⅡIDE进行软件设计,控制整个采集流程,实现了数字视频图像的高速A/D转换、存储及显示等功能。

1 PAL制数字视频图像

目前,世界上采用的电视信号制式主要有PAL制、NTSC制和SECAM制3种,中国采用的电视信号是PAL制。PAL电视制式规定,场扫描频率为50 Hz,每帧图像的扫描行数为625行。PAL制电视信号如图1所示[4-5],图中H为行同步信号的周期,标称值为64 μs。

PAL制电视信号转化为数字视频信号后,数据格式一般符合ITU 656 YUV 4∶2∶2标准,其主要特征有:

1)25 f/s的帧率,每帧分为奇数场和偶数场。每帧扫描625行,其中有效图像数据572行,每行采样864个像素,其中有效像素720个。

2)有3个正交分量。亮度分量Y、色度分量U(Cb)和V(Cr),Y表示明亮度(灰度值),Cb和Cr表示色度(色彩及饱和度)。其中亮度分量Y每行采样864次,色度分量Cr和Cb每行采样432次。

3)8 bit或者10 bit的PCM编码。量化时0和255用于同步;1~254表示采样结果的PCM码;对于亮度分量Y,16表示黑色,235表示白色;对于色度分量Cb/Cr,128表示没有色度。

4)有3个信号用于同步输出的数据。行同步信号、场同步信号和像素同步信号[6]。

2 采集模块工作原理及硬件平台构建

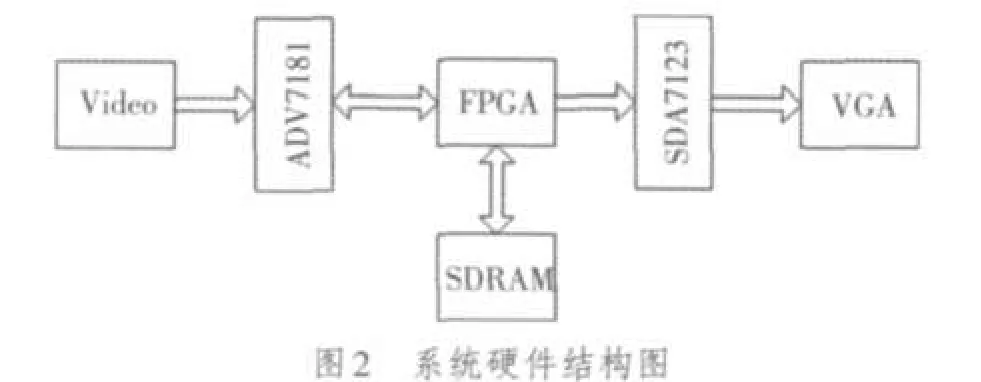

工作原理为:由视频信号源输出PAL制模拟信号,采集开始。首先由I2C配置好后的视频解码芯片ADV7181将输入的模拟视频信号进行解码,输出8 bit格式为YCbCr 4∶2∶2复合视频数字信号,接着利用视频图像处理模块对视频数字信号进行4∶2∶2到4∶4∶4的格式转化,YCbCr到RGB色彩空间的转换等处理,再通过视频编码芯片SDA7123进行D/A转换,最后在VGA监视器上显示出来。

本文选用Altera CycloneⅡ系列EP2C35型号的FP⁃GA芯片。该芯片具有33 216个逻辑单元、475个用户自定义I/O接口、35个嵌入式乘法器和4个锁相环。在FP⁃GA中设计了以下模块:PLL、NiosⅡ嵌入式软核处理器、挂接在Avalon总线上的JTAG UART,PIO,Timer,System ID,SDRAM Controller,Flash(CFI)Controller等内核以及用户定制的逻辑外设模块freedev_i2c,serial_segment,freeedev_bt656,freedev_sram。在FPGA外围有视频解码芯片ADV7181,用于存储的SDRAM,视频编码芯片SDA7123等。图2为系统硬件结构图。

在系统硬件平台中,嵌入到FPGA的处理器和各接口模块是设计的关键。利用Altera公司的QuartusⅡ软件中集成的SoPC Builder开发工具来创建设计基于处理器、外围设备和存储器的嵌入式系统将大大缩短整个设计周期。下面主要对NiosⅡ软核处理器、ADV7181及其I2C配置、视频图像采集模块、视频图像解码及颜色转换模块等几个关键模块的设计进行介绍。

2.1 NiosⅡ软核处理器

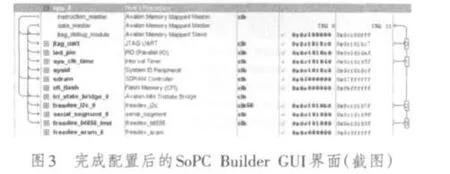

NiosⅡ处理器是Altera公司推出的第二代用于可编程逻辑器件的可配置的软核处理器。由于处理器是软核形式,具有很大的灵活性,因此,可以在多种系统设置组合中进行选择,达到性能和成本的要求[7]。NiosⅡ处理器系列包括三种内核:高速内核(NiosⅡ/f)、经济内核(NiosⅡ/e)、标准内核(NiosⅡ/s)。本文采用的CycloneⅡ系列的EP2C35芯片逻辑资源十分丰富,加上采集系统实时处理对CPU的性能要求较高,因此选用了高性能的NiosⅡ软核作为本系统的CPU。接着再完成其他外设模块的添加,即完成了嵌入式系统的设计。图3为完成配置的SoPC Builder GUI界面。

2.2 ADV7181及其I2C配置

本文采用ADV7181芯片来完成模拟视频信号的A/D转换。ADV7181是Analog Device公司推出的一款高性能的集成视频解码芯片,能自动检测并转换标准NTSC,PAL和SECAM制式的电视信号为8 bit或16 bit的YCb⁃Cr 4∶2∶2复合数字视频。

ADV7181支持I2C串行总线接口,通过I2C接口对芯片内部相关控制寄存器进行配置。图4为I2C总线传输时序。本文中的freedev_i2c模块是用户自定制逻辑实现的,编写verilog代码,实现I2C协议,并通过Avalon总线接口与NiosⅡ软核处理器相连。

2.3 视频图像采集模块

freeedev_bt656模块对ITU-R BT.656 YCrCb 4∶2∶2格式的数字码流进行采集处理,并作为用户自定义外设挂接在Avalon总线上。因此,模块的端口要符合Avalon接口规范,分为主端口和从端口。主端口为发起传输的Avalon信号类型的集合,从端口为响应传输请求的Ava⁃lon信号类型的集合。freeedev_bt656模块通过slave port来设置模块工作参数和模式,视频采集部分以输入视频时钟采集数据并缓存到视频FIFO中,master port部分读视频FIFO中的数据,并支持突发式传输将数据存放到内存中,从而实现视频图像的采集与存储。

2.4 视频图像解码及颜色转换模块

本文中的Tv_to_VGA模块完成视频图像的解码及颜色转换功能。从ADV7181输出数字码流的格式为ITU-R BT.656 YCrCb 4∶2∶2,即每采4个亮度信号,就各采样2个色差信号。因此在颜色变换之前,采用“nearest neighbor”[8]像素缩放方法,即通过复制相邻采样点的色差信号的方法将其格式转化为YCrCb 4∶4∶4。视频图像输出部分的设计采用了SDA7123视频D/A转换器,实现数字RGB转换为模拟RGB(VGA)信号输出的功能,因此在Tv_to_VGA模块中也要完成YCrCb到RGB颜色空间转换的功能,输出8 bit的数字RGB信号、行场同步信号和VGA时钟及消隐等信号,将这些信号送给SDA7123芯片进行D/A转换,最后送给VGA监视器。

3 采集模块的软件设计

系统的软件设计是在NiosⅡ集成环境下完成的,NiosⅡ集成开发环境(IDE)是NiosⅡ系列嵌入式处理器的基本开发工具。设计中以C语言的形式并利用IDE集成环境提供的硬件抽象层(HAL)的函数来完成软件程序的编写。

在采集系统启动后,首先初始化视频I2C控制器,对ADV7181进行配置初始化以及清空FIFO缓冲器等,接着写命令寄存器,启动采集。在采集过程中,通过读FIFO的状态,并利用printf函数输出就可以在IDE界面的Con⁃sole控制台中查看采集过程中FIFO的即时状态,程序中几个主要部分如下:

1)按照PAL的设计要求对ADV7181B相关寄存器进行配置。

2)在SDRAM中开辟视频缓存空间,定义其大小,并将其初始化为0。

3)写命令控制寄存器,禁止采集和存储,并清空FIFO。

4 采集系统测试及结论

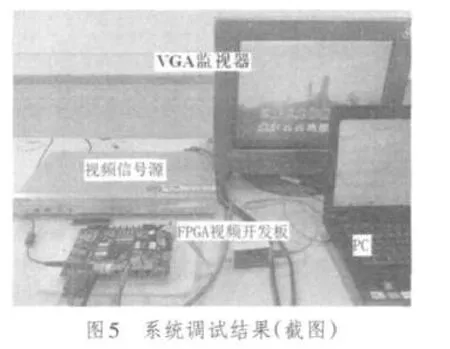

在实验室条件下对系统进行测试。启动系统,开启视频源进入视频采集处理过程,并最终在VGA监视器上显示出稳定清晰的视频图像,图5为系统调试结果。

在采集过程中使用Altera SignalTapⅡ嵌入式逻辑分析仪对FPGA信号及状态进行检测,图6为SignalTapⅡ检测波形,其中A处的YCrCb 4∶2∶2码流为连续的80h10h,表明此时段正处于视频消隐阶段,B处表明在消隐阶段解码后RGB输出00h,C处表明一个行同步信号的使能,分析得到检测波形符合设计的要求。

本文采用SoPC技术,通过在CycloneⅡFPGA芯片上配置NiosⅡ软核处理器及相关接口模块来实现硬件平台,并利用Altera公司的软件集成开发环境NiosⅡIDE进行软件设计来控制整个采集流程。实现了数字视频图像的高速A/D转换、存储及显示等功能。由于采用SoPC技术,模块具有设计灵活、采集速度快和扩展升级性好等优点。

[1]黎洪松.数字视频技术及其应用[M].北京:清华大学出版社,1997.

[2]聂飞,冯宗哲,郭宝林,等.嵌入式视频采集系统的实现方法研究[J].电视技术,2003,27(8):46-49.

[3]周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006.

[4]宋承杰,王景存.基于FPGA的视频字符叠加的设计与实现[J].电视技术,2009,33(12):24-27.

[5]刘韬,楼兴华.FPGA数字电子系统设计与开发实例导航[M].北京:人民邮电出版社,2005.

[6]钱敏,李富华,黄秋萍,等.基于HDL的PAL制数字视频图像采集控制器设计[J].微电子学与计算机,2007,24(12):191-194.

[7]王晓迪,张景秀.SOPC系统设计与实践[M].北京:北京航空航天大学出版社,2008.

[8]JACK K.Video demystified[M].Burlington:Newnes,2005.