基于FPGA的VGA图像动态显示控制器的设计与实现

2011-06-07廖永清丁旭昌付建国陈舜儿刘伟平

廖永清 ,丁旭昌 ,付建国,陈舜儿 ,刘伟平

(1.暨南大学 电子工程系,广东 广州 510632;2.光电信息与传感技术广东普通高校重点实验室(暨南大学),广东 广州 510632)

0 引言

随着电子技术和集成工艺水平的不断提高,微处理器的运算与控制能力也有了显著的提升,由于越来越多的电子产品对功耗有着苛刻的要求,导致目前微处理器的带负载能力比较弱,通常输出电压为mV级,这也制约了它们在显示应用领域的发展。目前,在数据采集和显示控制领域,FPGA正好弥补了微处理器带负载能力弱的缺点,且它在VGA(Video Graphics Array)信号处理中也有着大量的应用[1]。

VGA是由IBM公司制订的一套视频传输标准,它在显示领域中得到了广泛的应用[2-3]。目前国内外一般采用VGA显示卡来实现VGA图像的动态显示和控制,但显示卡价格一般比较高,且增加了系统的体积与复杂度,给系统今后的维护和升级带来诸多不便。针对这种情况,笔者研究并设计了一种基于FPGA的VGA图像动态显示控制器,该控制器采用Verilog HDL实现相关的控制功能,这大大提升了系统的实时性和可靠性,在大规模嵌入式系统设计中具有较高的工程价值和很好的应用前景。

1 系统设计方案

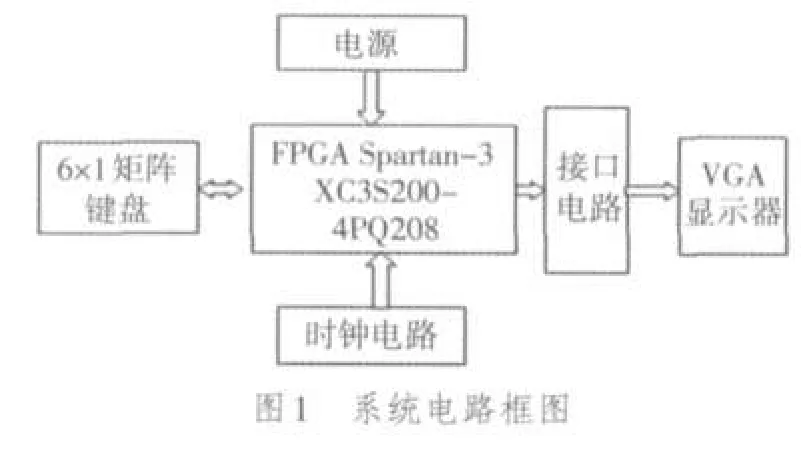

VGA图像动态显示控制器主要由基于Spartan-3系列XC3S200-4PQ208的FPGA、时钟电路、系统电源、接口电路、6×1矩阵式键盘和VGA接口的显示器,其系统电路框图如图1所示。其中FPGA是整个系统的核心部分,通过对其编程可输出红、绿、蓝三基色信号和HS(Horizon Synchronizing)、VS(Vertical Synchronizing)行场扫描同步信号。当FPGA接收时序信号后,内部的显示控制模块根据控制信号选择相应的图像信息模块并输出图像信号,与行场扫描时序信号一起通过VGA接口电路送入显示器,在VGA显示器上便可看到相应的动态图像。

2 系统软件设计

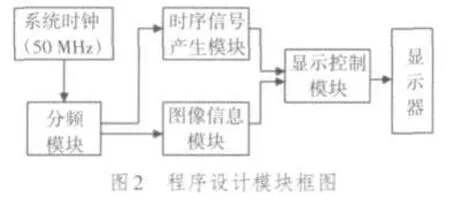

VGA图像动态显示控制器的软件实现采取的是自顶向下的方式,由系统整体设计方案规划相应的软件框图,将其划分为分频模块、时序信号产生模块、图像信息模块和显示控制模块。再运用Verilog HDL设计各个子模块,同时对各个子模块分别进行仿真与调试,最后将所有调试成功的子模块集成为一个整体的系统,程序设计模块框图如图2所示。要实现VGA图像动态显示在软件实现上有两个关键点:第一是要实现VGA的时序,使得VGA信号严格遵守协议要求的行、场同步时序;第二是实现图像控制[4],本设计的难点是实现图像信号的动态显示控制。以下介绍程序各个子模块的设计与实现。

2.1 分频模块

系统为FPGA提供的主振频率是50 MHz,本设计要实现VGA显示模式是640×480@60 Hz,按照VGA协议传输标准这种显示模式的时钟频率要求为25.175 MHz,所以在分频模块中首先要对时钟信号进行2分频,在误差尤许的范围内分频后的时钟频率可满足该显示模式下的时序要求。

2.2 时序信号产生模块

要实现VGA的显示与控制关键是要实现它的时序关系,即产生的行同步信号和场同步信号符合VGA传输标准协议的要求,该模块的作用就是把系统时钟分配到各个模块并产生相应的同步信号。要形成一幅完整流畅的图像,首先要确保行、场同步,因为二者的同步就确定了一行和一帧图像的开始和结束时间[5]。VGA的协议传输标准给出的参考显示时序如图3所示,由图可知,虽然行频和场频在数值上相差比较大,但二者在时序上是一样的。

2.3 图像信息模块

图像信息模块包括传输图像数据和图片在显示屏幕上的定位两个部分,利用行场同步信号的计数器可以对图片进行定位,在图像显示的有效区域内按照显示模式和图片的大小确定行和列的起点坐标和终点坐标。对于图片数据的传输,这通常取决于字库提取软件的相关设置以及图片的大小与形状,本文采用的是PC⁃toLCD2002字模软件,取模方式选择列行式,取模走向选择逆向,字模软件的相应配置就决定了图片的一个像素点就对应着字节的数据。这里特别注意的是在行同步信号到达图片定位的位置时,必须将相应的数据信息全部送出,否则将会出现画面不流畅或失真等。

2.4 显示控制模块

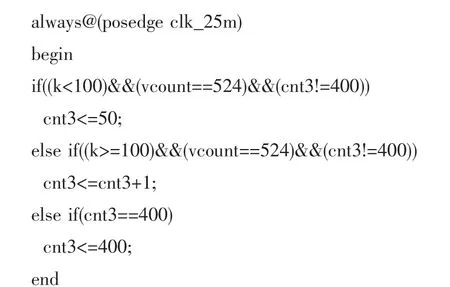

VGA图像动态显示是基于动画帧的思想,当场计数器每计到524时,屏计数器k加1,用屏计数器控制画面显示的先后顺序,在快速扫描时,要实现流畅的动画显示,每秒至少应该显示24幅图片。在实际应用过程中,k的值不能是无限大的,应该根据设计中定义的寄存器的大小来锁定某一个值,否则之前出现过的图片又会重现。本设计实现屏计数器的代码为:

动态显示的过程当中,显示流畅的图像的同时也应该避免不同图像的重叠现象,因此要能看到不同图像错落有致地显示,对要显示的每一幅图像都应该定义其动作,这也是设计的一个难点,以下是本设计实现其中一幅图像动作的部分代码。当屏计数器k<100时,图像的位置不变;当k>100时,图像的位置随着k的增加开始发生变化,在屏幕上图像表现为一个下落的过程。具体代码为:

3 系统仿真和联调结果

3.1 仿真结果

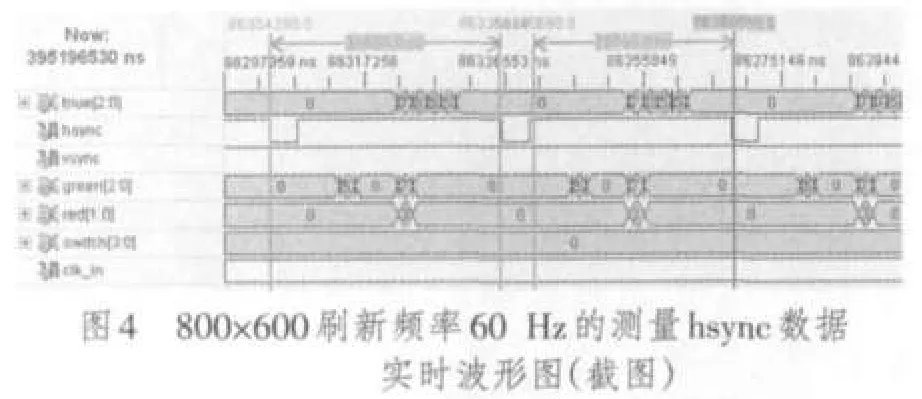

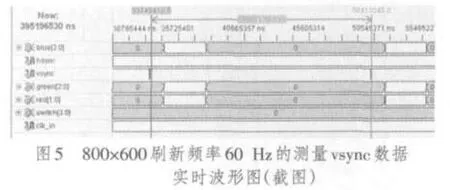

时序信号产生模块是本设计的关键,本文对其进行了严格的仿真和验证。本设计利用Xilinx ISE 7.1i ISE仿真工具Simulator,通过Verilog HDL语言编写Test⁃bench,最后的仿真结果如图4和图5所示。

利用Simulator ISE仿真工具可以实时监测到行时序和帧时序的实时波形,从仿真图可以看到,显示模式为640×480@60 Hz时,每一帧的时间是16.6 ms,每一行的时间是31.66 μs,仿真结果完全符合该显示模式下VGA接口的协议。

3.2 联调结果

在Xinlinx ISE 7.1i中建立项目后,输入各模块的Verilog HDL程序代码,并进行逻辑综合、布局布线、时序分析后生成编程文件,再将编程文件下载到FPGA中并通过VGA接口与显示器相连。通过联调可以看到,显示器上能错落有致地动态显示图片,并在OSD选单中选择模式,此时显示器上显示了640×480@60 Hz的显示模式,显示器上显示的部分画面如图6和图7所示,达到了设计的预期目标,验证了设计的准确性。

4 小结

本文设计的VGA图像动态显示控制器是基于FPGA上实现的,采用Verilog HDL语言在Xilinx ISE 7.1i软件环境下完成软件设计,并对整个系统都进行了调试,最终在硬件平台上实现了动态显示图像。与传统实现方案相比,本系统具有以下优点:1)系统采用了Verilog HDL语言编写,这样可以使软件程序简洁且执行效率高,减少了开发工作量、降低了设计难度;2)系统是基于FPGA上实现的,增加了系统驱动能力、可靠性和设计灵活性,对嵌入式系统的实现具有较高的工程价值;3)系统采用FPGA芯片作为控制核心,可以在不使用VGA显示卡和计算机的情况下实现VGA图像的动态显示和控制,大大减少了电路板的尺寸,节约了成本并扩展了应用范围。

[1]刘威,石彦杰,高博.基于FPGA的VGA显示模式识别[J].计算机工程与科学,2008,30(4):152-155.

[2]王恒心,熊庆国.基于FPGA/CPLD的嵌入式VGA显示系统[J].微计算机信息,2008,24(9):146-148.

[3]陈晓辉,刘峰.基于TMS320DM355的VGA信号实时监控系统[J].电视技术,2010,34(3):25-27.

[4]谢昭莉,蒋涛,刘亮,等.基于ARM嵌入式系统的VGA接口的研究与设计[J].液晶与显示,2007,22(6):761-764.

[5]段磊.基于FPGA的VGA显示系统[J].世界电子元器件,2007(9):102-103.