基于ADSP2106X的制导雷达信号处理方法*

2011-06-07刘富强

贺 珍 刘富强

(91404部队 秦皇岛 066001)

1 引言

为满足对新型电子对抗装备检验、鉴定的需要,须对试验保障设备进行研制和改造,制导雷达系统作为检验电子对抗效果的重要设备[1],在研制过程中,力争能将国内外已有的末制导雷达的功能集于一身,使系统具有功能强、技术先进、集成度高、可靠性强的特点,能在较长时间内保持使用价值,延长使用周期。为此,系统采用全数字信号处理技术,为满足大数据量和高速实时处理的要求,关键是合理设计数据处理系统,核心是选择数据处理芯片[2],经过充分论证,决定采用 ADSP2106X作为系统的核心处理芯片。

2 末制导雷达系统信号处理需求

系统作为检验新型电子对抗装备的设备,主要包括制导雷达及控制设备,不仅要具备末制导雷达的正常功能,而且要具备一般设备的可操作性、可控性和显示功能,能够灵活地选择雷达参数,控制雷达工作方式,达到试验检测对不同雷达选择的要求。因此,系统必须具备以下功能[3~4]:1)完成对目标的搜索;2)实时处理在雷达搜索范围内的目标信息,完成信号检测;3)完成对目标信号的跟踪;4)对雷达的控制,包括参数设置、工作方式选择等;5)雷达工作状态显示;6)目标参数显示;7)雷达与控制设备间的通讯;8)雷达回波信号视频重组和回放。

为完成以上功能,系统的信号处理能力必须很强,不仅数据处理量大,而且要求处理速度高、实时性强[5]。在实现雷达信号的数字脉冲压缩和两维检测,完成目标的方位、距离、速度搜索、检测和跟踪工作的同时;完成雷达回波视频信号的处理,提取目标信息;处理雷达和控制台间的通讯,接收控制台的控制命令和参数,控制雷达的工作方式和工作流程,输出目标参数等[6]。

3 ADSP2106X的技术特点

AD公司的ADSP2106X系列是一种高性能32位浮点DSP[7],不仅具有很强的处理功能,而且有大容量的片内RAM,是高速信号处理设计的首选。它的基本特点[8]有:1)最高工作频率为40MHz,时钟周期25ns;2)数据线有48根,地址线有32根,地址范围4G;3)所有指令都是单周期指令,指令长度均为48bit;4)32-bit IEEE浮点运算单元,内含乘法器、ALU和移位器,支持40bit的扩展精度浮点运算;5)10个 DMA通道;6)4Mbit双口片内存储器;7)有两个同步串口和六个连接口;8)支持多处理器共享总线。

ADSP2106X提供了强大的实现多处理器并行处理的能力,任何一片ADSP2106X都可以访问其它ADSP2106X的片内存储空间。由于片内SRAM为双口存储器,因而这种访问并不中断被访问处理器的正常工作[9]。另外ADSP2106X还具有六个4bit的连接口(Link Ports),每个连接口可以两倍于系统工作时钟的速率传送数据,因此每个连接口在一个时钟周期内能够传送一个8bit数据。在不增加辅助电路的条件下,ADSP2106X通过其它六个连接口实现处理器之间点到点的通信。ADSP2106X的运行速度非常快,其指令周期为25ns,即每秒能处理四千万条指令,并且单周期内可以乘法、加法、减法三操作并行,计算一个1024点的复数FFT只需0.46ms,而计算浮点倒数的时间只需150ns。

4 硬件设计

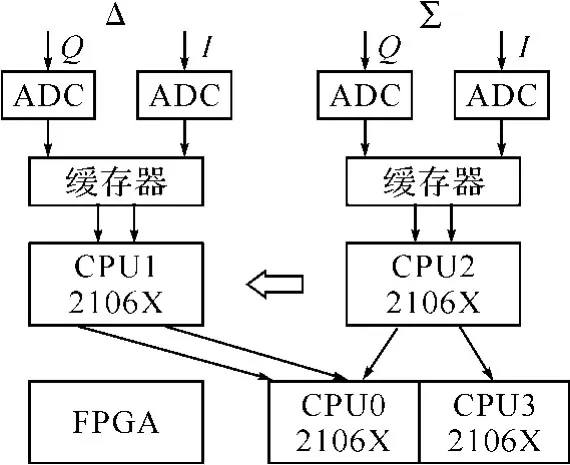

根据ADSP2106X的性能特点[12],结合系统功能需求;系统设计由四片ADSP2106X(CPU)芯片和一个FPGA组成数据处理的核心。其中两片分别完成和/差两路信号的脉冲压缩、相参积累、两维恒虚警检测和目标参数的提取;一片完成工作模式和流程的控制,并完成与控制台的通讯;一片完成脉冲压缩后回波信号重组输出前的数据处理;FPGA完成系统时序控制。数字处理系统实现框图如图1所示。

图1 系统组成框图

系统核心芯片数字信号处理器DSP的运行速度与前端A/D转换器的运行速度往往是不同步的。在单通道情况下,DSP处理数据的能力超过了A/D转换器采集数据的能力,而多通道同时采集的情况下,又会出现相反的状况。为了协调、控制它们之间的工作,需要在两者之间加入数据缓存器。

各CPU的工作如下:

CPU0:作为主CPU,完成系统的管理、工作模式的选取、目标信息的提取、与前端和微机信息的传输、接口电路的管理等。

CPU1:完成差路的脉冲压缩和相参积累。

CPU2:完成和路的脉冲压缩、相参积累、目标检测。

CPU3:完成脉冲压缩后数字回波的整理输出。

系统的时序由FPGA控制,完成系统中所需各种脉冲的产生;完成DSP地址信号的译码和片选信号的产生;时钟的驱动和控制线的逻辑;产生DSP的DMA时序逻辑,配合DSP以DMA的方式完成数据的输入和输出。

系统数据流程:在DMA请求到来时,CPU1和CPU2分别读入“差路”和“和路”A/D变换后输入的I、Q信号。CPU1/CPU2完成脉冲压缩、谱分析、平面CFAR后通过链路口将目标结果传送到CPU0,同时CPU2将和路脉冲压缩后的I、Q两路数据通过链路口传输到CPU3。CPU3的工作也由DMA请求触发,每当DMA请求到来时,CPU3就将CPU2传来的I、Q两路数据整合成一路D/A输出数据,通过控制AD转换成模拟信号输出。

5 软件设计

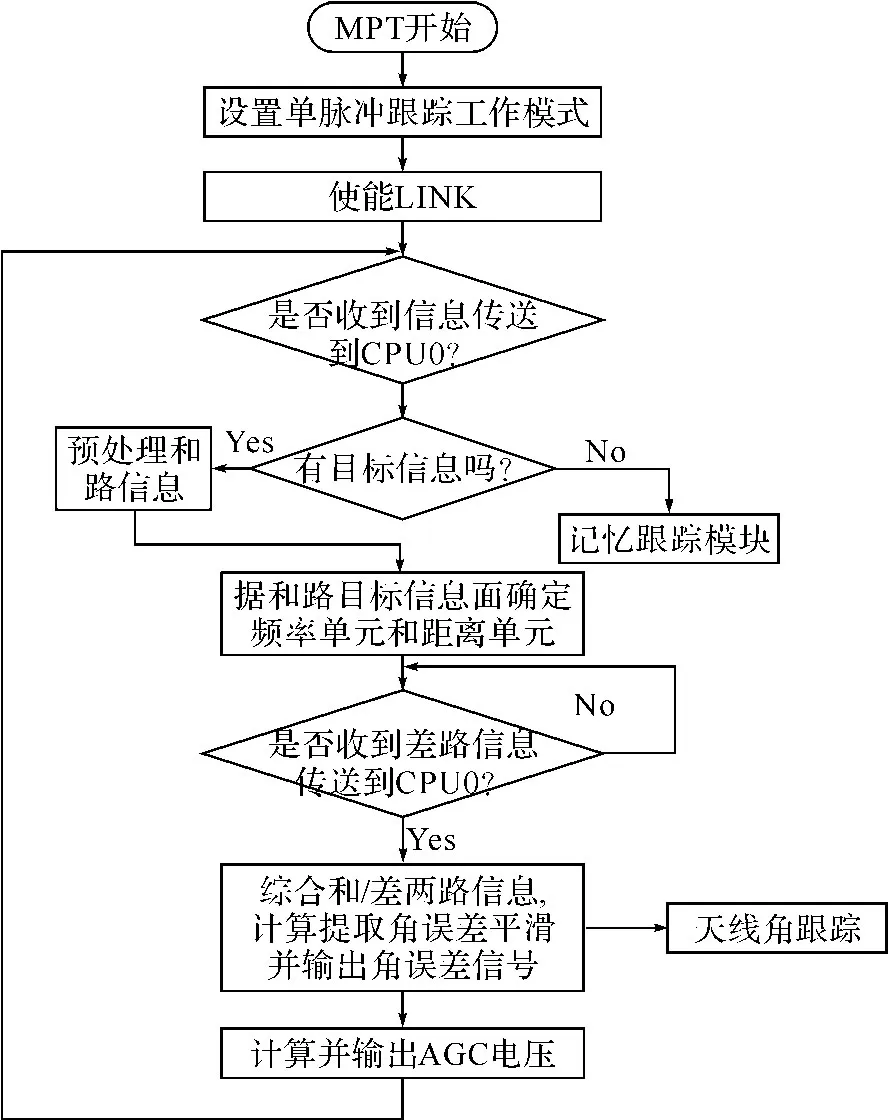

系统软件设计根据4个CPU的功能要求分别实现。下面以CPU0为例描述系统软件,软件工作流程图如图2、图3所示。

功能:

1)目标搜索、截获、跟踪,系统工作模式的控制。

图2 搜索截获软件工作流程

图3 跟踪软件工作流程

2)提取并输出角误差信号,输出AGC、方位搜索、俯仰搜索信号。

另外,可以根据实际需要,编写所需的应用程序,例如FFT、数字滤波、功率谱分析、加窗处理、存储示波显示、波形实时显示等,用ADSP2106X提供的汇编工具生成可执行文件,就可以直接装入执行,使得系统的应用更加灵活和方便。

6 结语

基于ADSP2106X并行结构设计的末制导雷达信号处理系统,能产生和处理多种不同雷达信号,且各种参数可根据试验需要来设置,功能强、使用灵活,所需外围器件少,电路设计简单。通过对处理单元进行各种软件编程就可实现系统的功能,具有很强扩展功能和通用性,大大减少了硬件研制费用,且提高了系统稳定性、可靠性,取得了很好的效果。

[1]林象平.雷达对抗原理[M].西安:西北电讯工程学院出版社,1985

[2]戴擎宇.高速数字信号处理技术及其在雷达中的应用[M].北京航空航天大学出版,2006

[3]罗景青.雷达对抗原理[M].北京:解放军出版社,2003:293

[4]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,1995:55~56

[5]何友,修建娟,张晶炜,等.雷达数据处理及应用[M].北京:电子工业出版社,2006:21~26

[6]王国玉,汪连栋,王国良,等.雷达电子战系统教学仿真与评估[M].北京:国防工业出版社,2004:86

[7]张立.细看当代舰载雷达[J].世界军事,2006(4):69~72

[8]侯明胜,秦海潮.雷达之间电磁兼容性研究[J].电子工程师,2007,33(9):6~9

[9]何明浩.雷达对抗信息处理[M].北京:清华大学出版社,2010

[10]万果果,张元,李建武,等.一种对统计信号处理中缺失数据估计的算法[J].计算机与数字工程,2010,38(10)

[11]张东,吴晓琳.短时傅立叶变换在振动信号处理中的应用[J].计算机与数字工程,2011,39(8)

[12]Zhang X,Willett P,Bar-shalom Y.Monopulse radar detection and localization of multiple targets via joint multi-bin processing[C]//Proceedings of the 2003 IEEE Radar Conference,2003:232~237