基于FPGA的GPS模块和电子罗盘模块驱动设计

2011-06-05薛红喜

李 宏,薛红喜

(成都电子科技大学 电子工程学院,四川 成都 611731)

全球定位系统 (Global Positioning System简称GPS)是美国第二代卫星导航系统,能提供全天候、连续、实时高精度导航参数,可实现三维定位,并可提供精确的时间信息,具有抗干扰能力强等特点。近年来,GPS在国内外得到广泛的应用,并在各个领域发挥了极大的作用,已成为导航、定位不可缺少的一部分。电子罗盘作为一种重要的航向传感器,正越来越多地应用于导航和定位系统中。其通过对地球磁场等信息的读取、计算,精确输出航向、俯仰、翻转等参数。

GPS模块是GARMIN公司的GPS-OEM产品,其可同时跟踪多达12颗GPS卫星,实现快速定位。电子罗盘模块是PNI公司的TCM3产品,其可用于测量航向、倾斜角和磁场强度,能够提供航向、横滚和俯仰值3个方向的定位数据。它们都采用RS232通信接口,可方便地集成到系统中。GPS模块采用NMEA-0183通信标准格式,输出数据采用ASCII码表示;其输出的完整定位数据多达60多个字节,也就是需要60多次的串口操作;电子罗盘模块控制也需要十几次的读写串口操作。而且,RS232接口的传输速率与DSP运行速度相比很低;因此,采用DSP直接控制GPS和电子罗盘模块,占用的DSP运行时间是相当可观的。

FPGA控制GPS模块和电子罗盘模块的流程并不复杂。GPS模块不需要任何设置,电子罗盘模块则只需要进行简单设置,所以采用FPGA作为GPS模块和电子罗盘模块驱动接口是完全可行的。此外,利用FPGA还可以将数据格式进行处理,缩短数据的位长,采用更高速的接口(SPI或者EMIF)与DSP通信。

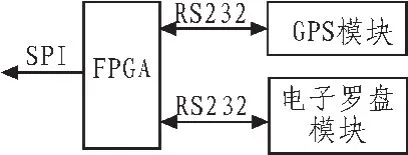

1 系统结构

本系统主要由FPGA,GPS模块和电子罗盘模块3部分构成,如图1所示。由于电平的不匹配,FPGA与RS232接口之间需要进行电平转换。系统工作的原理是通过FPGA直接接收GPS模块发出的数据,从中提取出时间、经度和纬度信息,并将这些数据格式由ASCII码转换成压缩BCD码格式保存。FPGA向电子罗盘模块发送相应的命令,然后获取电子罗盘输出的航向信息并直接保存。这些数据都可由DSP通过SPI接口读取。

图1 系统整体结构Fig.1 Block diagram of system

SPI接口通信速度能够比RS232高很多,能够实现板与板之间的短距离通信,因此被选择作为对外的通信接口;此外,因为FPGA非常灵活,如果FPGA与DSP的EMIF接口直接相连,可以将SPI接口改为EMIF接口,通信的效率会更高。

2FPGA逻辑模块设计

FPGA逻辑设计按功能可以分为SPI通信模块,RS232通信模块,电子罗盘驱动模块和GPS驱动模块4个部分。这种模块化的设计思想在FPGA设计中很重要,这有助于设计者对设计的管理和修改。例如,要将SPI接口换成EMIF接口时,并不需要将设计进行重新设计,而只需要用EMIF接口模块的代码替换SPI接口模块的代码即可。本设计使用的FPGA是Altera的Cyclone III系列中的EP10F256I7N,系统时钟33.3 MHz,SPI接口通信速率约为1 MHz,RS232通信波特率为9 600 bps,硬件设计语言采用VHDL。

2.1 SPI通信模块

SPI总线接口是一种同步串行总线通讯接口,有主从之分,分为读写两种通信状态。这里被设计为从模式。

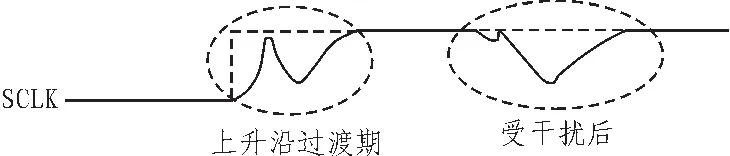

SPI接口的设计需要注意SPI接口通信时钟信号(SCLK)的处理。因为SCLK不可能像专用的时钟输入信号一样距离FPGA器件尽量地靠近;往往为了满足设计的要求,布线长度可能达到几十厘米,不可能不引入干扰;如果直接用做SPI通信的时钟信号,通信肯定会存在风险。如图2所示,SCLK变化的过渡期内,信号的状态不能很快稳定,可能一次上升沿被误认为2次上升沿而出现错误动作(如果SPI的上升沿有意义的话);此外当SCLK受到干扰后,也可能出现错误的逻辑动作。所以在要求较高的情况下,SCLK一般不能直接作为SPI通信的时钟信号。

图2 SPI接口的时钟信号的波形Fig.2 The clock signal waveform of the SPI interface

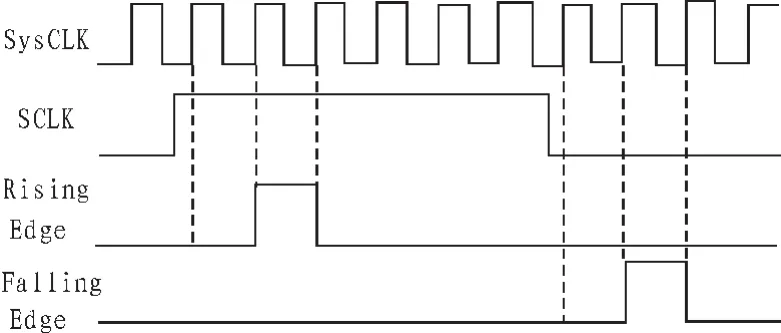

为了减少SCLK引起通信错误,可以使用系统时钟先对SCLK信号进行同步的方法。通过连续多个状态来判断SCLK的情况。如果连续几个时刻SCLK的状态都是高电平,而以前几个连续时刻是低电平,那么可以判断为是SCLK的上升沿,如果再出现连续几个时刻都是低电平,则判定为是SCLK下降沿。依次这样来跟踪SCLK的变化情况,如图3所示。可见,FPGA内部实际的逻辑动作时刻会比SCLK的有效边沿晚一个系统时钟周期,但是如果系统的时钟比SCLK的频率高几十倍时,这根本不会影响SPI的正常通信。

2.2 RS232通信模块

RS232是一种异步串行通信物理接口标准,可用于速率小于20 kb/s,20 m距离内的通信。根据不同的应用需求,RS232接口通信有多种接线方式,其中最简单的接线方式是采用接收(RX),发送(TX)和地(GND)的3线制。本设计也采用这种接线方式。

图3 SCLK在系统时钟域中的同步Fig.3 The synchronize of the SCLK signal in the system clock domain

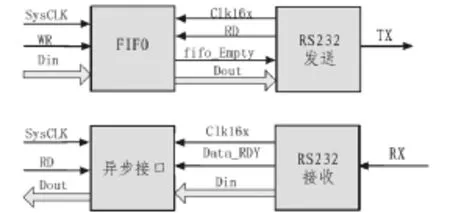

RS232模块在设计时需要注意不同时钟域之间的时序处理。RS232模块的运行时钟等于波特率速率的16倍频率,而不是采用系统的运行时钟,所以必须在RS232模块与其他采用系统时钟运行的模块之间建立一个异步通信接口,才能保证它们之间的正确通信。本设计中,采用图4的结构作为与RS232模块之间的异步通信接口。在发送数据时,只需向异步FIFO中写入需要发送的数据。当FIFO中有数据时,FIFO的空标志(图4中fifo_Empty)变为无效,RS232发送模块就会自动从FIFO中读取数据,将数据串行的发送出去,直到FIFO重新变为空为止。RS232模块接收到数据后,标志信号(图4中Data_RDY)电平发出信号,其他模块就马上读取。为了保证接收到一个数据只被读取一次,采用标志信号的边沿变化来作为触发条件。

图4 RS232模块的结构Fig.4 The structure of the RS232 module

2.3 电子罗盘驱动模块

FPGA驱动电子罗盘模块必须发送两个命令:设置输出数据结构命令 (SETDataComponents)和请求输出数据命令(DataREQ);电子罗盘模块可以输出的数据种类有:航行角度、温度、失真、校准状态、垂直俯仰角度以及水平旋转角度,可以根据需要通过输出数据结构命令来设置电子罗盘模块每次输出的数据种类。读取数据之前,必须向电子罗盘模块发送请求输出数据命令,电子罗盘模块才能输出数据[6]。

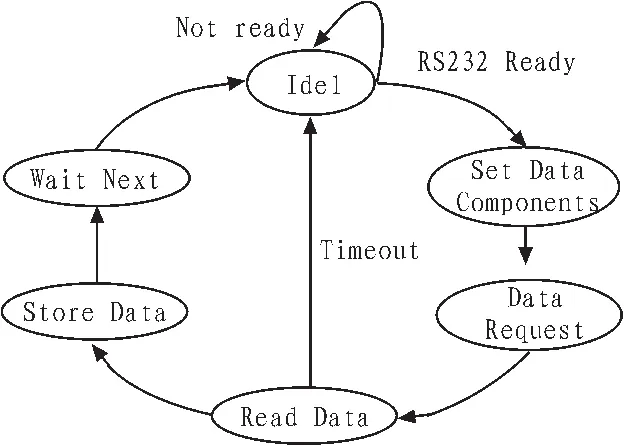

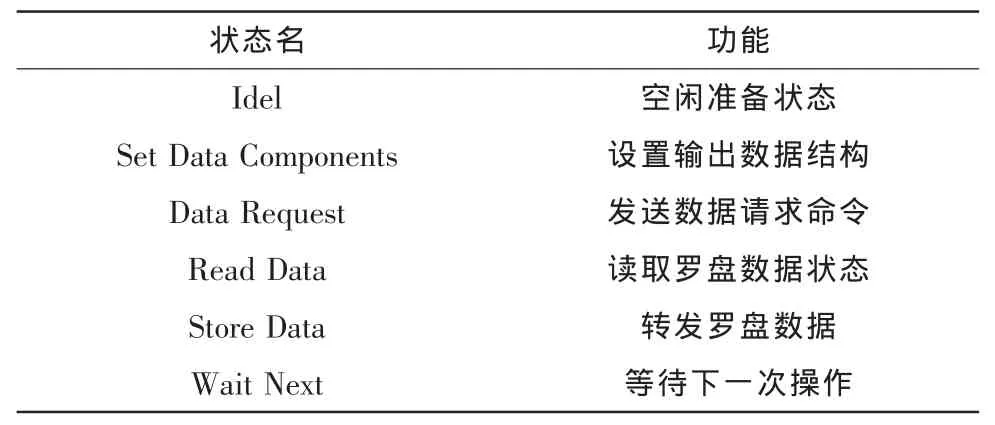

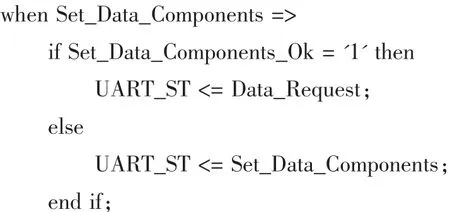

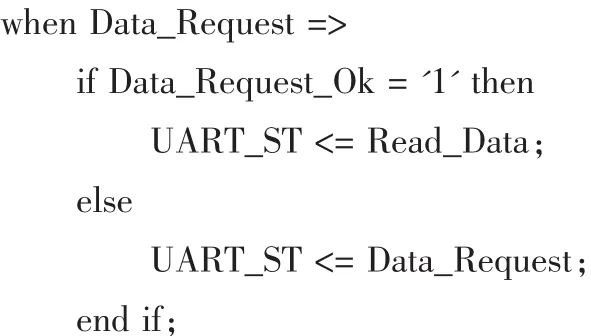

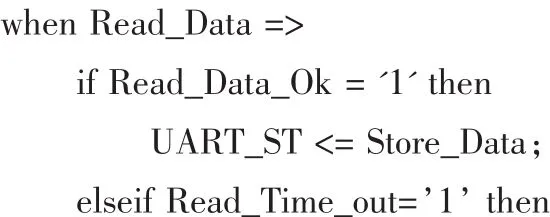

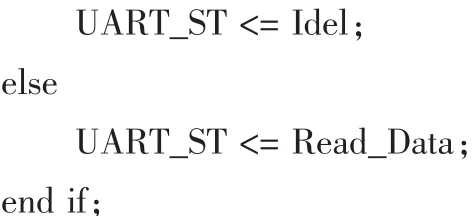

电子罗盘驱动模块采用了有限状态机的控制方式,因为状态机能够实现可靠稳定的控制流程,而且逻辑资源占用更少。电子罗盘驱动模块的状态机包含6个状态,如图5所示,每个状态的定义如表1所示。

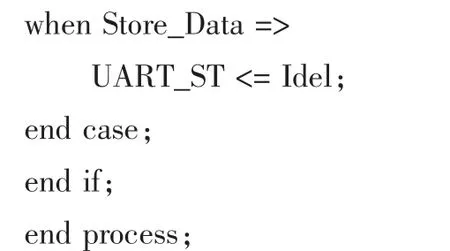

电子罗盘驱动模块状态机VHDL代码(部分)

图5 状态流程图Fig.5 Flow chart of the state

表1 状态定义Tab.1 The definition of state

—用于控制读取数据的频率(2次/秒),开机时等待电子罗盘内部完成初始化。

—设置电子罗盘输出数据结构。—向电子罗盘发送请求输出数据命令。

—读取电子罗盘输出的数据。

—如果在规定时间内,没有返回数据,返回Idel状态重新发送命令。

—保存数据,然后返回Idel状态。

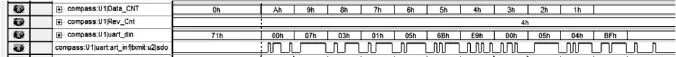

图6 RS232模块发送数据Fig.6 Sending data by RS232 module

图6通过 Quartus II软件的SignalTap Logic Analyzer工具进行在线仿真所截取的RS232发送SETDataComponents命令的波形;图中Data_CNT信号表示减法计数器的计数值,指示需要写入RS232模块的数据字节数;uart_in信号指示了输入到RS232模块中的数据,这个数据将通过串行输出端口发送出去;sdo表示RS232模块串行输出端口。从图中可以看出,电子罗盘模块正确地控制了发送SETDataComponents命令的操作过程,RS232模块也正确地将数据串行发出了。

2.4 GPS驱动模块

GPS驱动模块在结构上与电子罗盘模块的驱动是相似的,但是没有发送部分(不需要向GPS模块发送控制命令)。GPS驱动模块只需要读取RS232模块接收到的数据,从中筛选出需要的信息(经度、纬度以及时间)。此外,由于GPS输出数据是采用ASCII码来表示,而数字(0-9)的ASCII码值的低4位就等于实际表示的数字,因此,将时间、纬度和经度数据的每一位数字直接截取其低4位,转换成压缩BCD码,即可减少一倍的数据位数,在FPGA中也能很方便地实现。

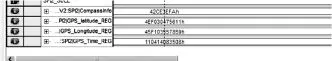

图7是通过Quartus II软件的SignalTap Logic Analyzer工具进行在线仿真的结果。图中第一行是电子罗盘输出的航向数据,第二行是纬度信息,第三行是经度信息,第四行是时间和日期。GPS模块的信息与本地的实际地理位置信息和时间几乎完全相符。在线仿真的结果证明FPGA能够正确实现对GPS模块和电子罗盘模块的控制。

图7 在线仿真结果(十六进制)Fig.7 The result of online simulation(in hexadecimal)

3 结束语

本文介绍了如何通过FPGA控制GPS模块和电子罗盘模块,采用用一个高速的SPI接口与DSP进行通信的方法,并在实际的硬件平台上成功地予以实现。与DSP直接对GPS模块和电子罗盘模块进行控制的方式相比,本方法在硬件方面,可以少使用至少一个DSP的McBSP接口,降低了对DSP器件外设接口的要求。在软件方面,DSP读取的GPS信息的数据长度减少到27个字节(直接控制时大于60个字节);对电子罗盘的控制只有读操作,不再需要写操作,因此,DSP运行过程中串口操作占用的时间明显减少,程序控制流程更加简单,系统的性能也得到提高。

[1]陈石磊,刘贵喜,向国华.FPGA与GPS-OEM板的串行通讯系统设计[J].新特器件应用, 2008, 10(5):11-13.CHEN Shi-lei, LIU Gui-xi, XIANG Guo-hua.The design of the serial communication system between FPGA and GPSOEM [J].Electronic Component&Device Applications,2008,10(5):11-13.

[2]伟利国,张小超,胡小安.TCM3电子罗盘的特性与应用[J].传感器与微系统,2009, 28(7):15-17.WEI Li-guo,ZHANG Xiao-chao,HU Xiao-an.Characteristic ofelectronic compass TCM3 and its application[J].Transducer and Microsystem Technologies, 2009, 28 (7):15-17.

[3]王松.基于FPGA的串行外围接口SPI设计与实现[J].微计算机信息:嵌入式与SOC, 2010, 25(11-2):117-119.WANG Song.Design and implementation of serial peripheral interface based on FPGA [J].Microcomputer information:Embedded System and SOC, 2010,25(11-2):117-119.

[4]王珏文,金伟信,蔡一兵,等.基于FPGA的SPI总线接口的实现[J].现代电子技术.2010, 14(325):102-104.WANG Jue-wen,JIN Wei-xin, CAI Yi-bing, etal.Implementation of SPI bus interface based on FPGA[J].Modern Electronics Technique, 2010,14(325):102-104.

[5]孙丰军,余春暄.SPI串行总线接口的Verilog实现[J].现代电子技术, 2005, 16(207):105-106,109.SUN Feng-jun,YU Chun-xuan.Implementation of SPI inerface with Verilog HDL[J].Modern Electronics Technique,2005, 16(207):105-106,109.

[6]田红霞,戴彦,鹿玉红.基于FPGA的RS232串行接口设计[J].煤炭技术.2010, 29(9):194-196.TIAN Hong-xia, DAI Yan, LU Yu-hong.Design Method of RS232 serial interface based on FPGA[J].Coal Technology.2010, 29(9):194-196.

[7]李金力,刘文怡,彭旭峰.基于FPGA的RS232异步串行口IP核设计[J].电子设计工程,2009, 17(8):31-35.LI Jin-li, LIU Wen-yi, PENG Xu-feng.Design of RS232 asynchronous serialportIP-core based on FPGA[J].Electronic Design Engineering, 2009,17(8):31-35.