基于Verilog的I2C控制器的设计与综合

2011-06-05张文梅褚越强

张文梅,刘 伟,褚越强

(1.中国人民解放军93756部队 电子教研室,天津 300130;2.北华航天工业学院 河北 廊坊 065000)

随着嵌入式产品的不断增多,因此构建其系统所需的芯片种类也不断增多,由于产品在体积和功耗等方面的约束,有时很难在市场上找到与其需求相对应的芯片,基于这个需求,本课题用Verilog HDL在FPGA上设计了一个I2C Slave的控制器,用来控制一些低速的设备,以此来满足产品对特定芯片的需求。

1 概 述

1.1FPGA概述

现场可编程门阵列FPGA (Field Programmable Gate Array)是一种可以编程的数字集成电路 IC(Integrated Circuit),它包含了可配置的逻辑块以及逻辑块之间的互连线。所谓的现场可编程是指设计人员可以通过在工作现场完成对这些逻辑块和连线的配置,以实现或改变复杂的电子系统的功能。随着半导体加工工艺的不断发展,FPGA在结构,速度,工艺,集成度和性能等方面都有了极大的改进和提高。本课题使用的是Altera公司的Cyclone II系列的芯片,它采用全铜层、低K值、90 nm、1.2 V SRAM工艺设计,提供4 608~68 416个逻辑单元,嵌入了18×18位的乘法器、专用外部存储器接口电路、4 kB存储器块、锁相环和高速差分I/O接口[1]。

1.2 I2C总线概述

I2C总线是一种通行世界的低速接口标准。在消费类电子的领域里,虽然有许许多多不同的应用,但是其组成却常常是确定的器件,如微控制器、随机存储器、电子可擦除式可编程存储器及一些特殊用途的集成电路。这些器件需能彼此沟通。沟通的方式,其电路的需求是降低设计成本和减小设计的复杂性[2]。飞利浦公司鉴于此,提出一种总线架构,这种总线架构是一种两条线双向的设计,此种总线架构被称为是Inter IC的总线,又简称I2C总线。它的特点是:只有两条导线,分别为串行数据线(SDA)及串行时钟信号线(SCL),这两条导线同时连接到总线上所有的Master和Slave,因此在同一时刻里,只会有一组Master和Slave在操作[3]。如果有一个以上的Master希望启动Bus,I2C具有的仲裁机制可以避免数据碰撞或破坏数据。串行操作在标准模式下,速率可以达到100 kbit/s,在快速模式下,速率可达到400 kbit/s。采用I2C的原因是节省成本和提高设计上的简易性,而非及高的频宽,如果是对存储器类的存取,就不适合采用I2C作为接口。

随着嵌入式产品的不断增多,因此构建其系统所需的芯片种类也不断增多,由于产品在体积和功耗等方面的约束,有时很难在市场上找到与其需求相对应的芯片,基于这个需求,本课题用Verilog HDL在FPGA上设计了一个I2C Slave的控制器,用来控制一些低速的设备。以此来满足产品对特定芯片的需求。

2 总体设计

本课题设计了一个I2C Slave控制器用来从I2C总线上接收数据,传送的数据除了启始位和结束位以外,还有两个字节的有效数据,其中第一个字节数据的前7位是用来确定与所设计I2C slave控制器进行通信的地址位,第8位是读写的标志位。当控制器接收到地址数据后会与自身的地址进行比较,如果一致,会接收总线上第2个字节,第2个字节是对控制器进行操作的命令位,控制器接收到这个数据后也会对其进行分析,从中取出有效位,来完成对各个外设的控制。

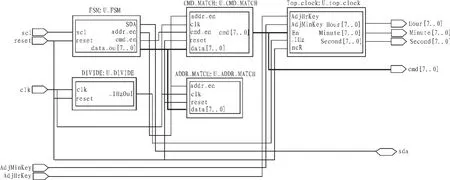

整个设计分为5个模块,一个模块为从I2C总线上接收数据,一个模块为地址匹配模块,当地址匹配成功后会调用命令匹配模块对传送过来的命令进行匹配,匹配成功后会将命令传至时钟模块来驱动时钟,在数码管上显示时间。还有一个分频模块用来给时钟模块提供所需要的频率。其综合后的电路如图1所示。

图1 顶层模块综合图Fig.1 Top-level module synthesis figure

3 设计结果

3.1 数据接收模块设计

此模块负责从I2C总线上接收数据,具体的设计思路是设计一个状态机,一共10个状态,分别为bit_idle,bit_7,bit_6,bit_5,bit_4,bit_3,bit_2,bit_1,bit_0,bit_ack, 当总线上没有数据时为bit_idle状态,它等待着总线上出现开始信号。当开始信号出现后状态机跳转到bit_7状态,在此状态里将总线上SDA数据线的数据存入寄存器变量data_in[7]里,然后跳转到下一状态继续接收总线上的数据,当状态跳转到bit_0时,即从总线上接收了8位数据后。此时状态机会跳转到bit_ack状态,在这个状态控制器发送一个确定信号来告诉主控端己经收到8位数据。然后再跳转到bit_7状态继续接收总线上的数据[4]。此模块的综合电路图如图2所示。

图2 接收模块综合图Fig.2 Receive module synthesis figure

3.2 地址匹配模块设计

当接收模块从总线上接收到第一个8位数据后,它将会发送一个addr_en的使能信号,使地址匹配模块使能,接收来自接收模块的数据,将接收到的数据与自身的地址进行对比。用Quartus对地址匹配模块代码进行综合,得出电路图如图3所示。

图3 地址匹配模块综合图Fig.3 Address match module synthesis figure

3.3 命令匹配模块的设计

当地址匹配模块将数据接收模块传过来的数据进行对比后,如果与自身地址一致,会发送一个addr_match为1的信号,此信号是命令匹配模块的一个使能信号。数据接收模块接收到的第二个8位数据是命令,当它接收这个命令后会发送一个cmd_en信号,当addr_match与cmd_en信号都为1时,此模块才会将接收到的命令与自身所存储的命令进行对比,如果与自身所存储命令相一致,就会控制各个模块按照接收到的命令完成各自的功能。

对此模块代码进行综合,得出如图4所示电路。

3.4 时钟模块电路的设计

图4 命令匹配模块综合图Fig.4 Command match module synthesis figure

时钟模块通过接收来自命令模块的命令对其进行驱动。时钟模块自身包括3个模块,分别是小时计数器模块,分计数器模块,秒计数器模块。而分计数器模块和秒计数器模块又分别包含6进制模块和10进制模块[5]。时钟模块所综合出来的电路,如图5所示。

图5 数字钟综合图Fig.5 Digital clock synthesis figure

3.5 分频模块设计

由于时钟模块所需的频率是1 Hz,而外界所提供的时钟是50 MHz,所以需要将外界频率分频,然后再送入时钟模块。其综合电路图如图6所示。

图6 分频模块综合图Fig.6 Frequency divided module synthesis figure

4 仿真测试平台设计及结果

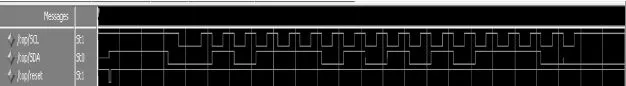

4.1 激励信号的输入

本仿真平台设计了模拟I2C信号的输入信号,目的是测试各个模块是否能正常工作,下面是设计的一个信号输入模块,此模块提供 3个信号,SDA,SCL和 reset信号,如图 7所示,总线上一共发送了两个字节的数据,分别是5D(0101_1101)和 AE(1010_1110)[6]。

图7 激励信号图Fig.7 Stimulus signal figure

4.2 对数据接收模块的验证

图8中,data_out为数据接收模块从总线上接收到一个字节数据后就会将输出,由图可见,数据接收模块可以正确的从总线上接收数据。当接收到第一个字节后,模块会输出addr_en信号,这是地址匹配模块的使能信号,当数据接收到第一个字节的数据后,会将其送入地址匹配模块去匹配。当数据接收到第二个字节后,会输出cmd_en信号,这个信号是命令匹配模块的使能信号。由图可知,此模块可以正确的接收数据。

图8 接收模块验证图Fig.8 Receive module verify figure

4.3 对地址匹配模块的验证

由图9可知,当地址匹配模块接收到数据接收模块传过来的数据并且使能信号addr_en为1时,它与自身的地址5d进行对比后,发现它们是一致的。即输出成功匹配的信号addr_match。

4.4 对命令匹配模块的验证

由图10可知,当数据接收模块接收到第二个字节ae后,它会输出一个命令匹配模块的使能信号cmd_en,命令匹配模块会在cmd_en和addr_en为1时将从数据接收模块得到的命令字输出从cmd端口输出。

图9 地址匹配模块验证图Fig.9 Address match module verify figure

图10 命令匹配模块验证图Fig.10 Command match module verify figure

5 结 论

综上所述,本课题用Verilog在FPGA上设计了I2C slave控制器,可以弥补专用I2C芯片功能单一的不足。以往的I2C控制器一般都指的是主控制器,用来发送I2C数据给I2C的专用芯片,而此控制器是从控制器,主要是从总线上接收数据并对数据进行分析来控制与其相连的外设。本控制器的不足之处在于只能有写操作,没有读操作,因此需要在后续的研究中继续完善功能。

[1]田红霞,戴彦,鹿玉红.基于FPGA的RS232串行接口设计[J].煤炭技术,2010,29(9):194-196.TIAN Hong-xia,DAI Yan,LU Yu-hong.Design method of RS232 serial interface based on FPGA[J].Coal Technology,2010,29(9):194-196.

[2]杜慧敏.基于Verilog的FPGA设计基础[M].西安:西安电子科技大学出版社,2006.

[3]孙玥.I2C总线的单片机C语言的实现[J].民营科技,2009,20(12):37-38.SUN Yue.I2C bus of the microcontroller C language implementation[J].Journal of Private Technology,2009,20(12):37-38.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2009.

[5]罗杰.Verilog HDL与数字ASIC设计基础[M].武汉:华中科技大学出版社,2008.

[6]吴继华,王诚.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005.