基于FPGA的串口通讯与VGA显示

2011-06-05姚善学王代强

姚善学 , 王代强 ,2

(1.贵州大学 理学院,贵州 贵阳 550025;2.贵州人民武装学院 贵州 贵阳 550025)

随着多微机系统的应用和微机网络的发展,通信功能显得越来越重要。串行通信是在一根传输线上一位一位地传送信息,这根线既作数据线又作联络线。串行通信作为一种主要的通信方式,由于所用的传输线少,并且可以借助现存的电话网进行信息传送,因此特别适合于远距离传送[1-4]。FPGA在数字电路的设计中已经被广泛使用。该设计方法可以使得多块集成芯片的电路设计到一个整体中,大大减少了电路板的尺寸,增强了系统的可靠性以及设计的灵活性。

1 系统总体实现方案

整个设计采用至顶向下的模块化的设计思想,设计过程包括顶层模块设计、子模块设计、模块最后合并为3个步骤[5]。顶层设计是设计的第一个步骤,包括对整个设计的规模进行估计,按照功能划分成各个子模块,以及估计子模块之问的相互关系。根据设计的需要,将整个设计按照实现任务分为3部分:串口数据的接收,由uart_rcv模块完成;数据的存储fifo,由fifo模块完成;输出VGA信号,由vga_dis模块完成。整个系统的框图如图1所示。

图1 系统总体框图Fig.1 Block diagram of the whole system

2 串口协议及设计过程

2.1 串口协议

串行通信的数据流是由若干个11 bits的数据符号的串联,每个数据符号包括1 bits的起始位、8 bits的数据位、1 bit的奇偶校验位、1~3 bits的终止位。

2.2 串口FPGA的实现

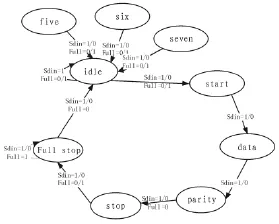

串口状态图设计:

根据串行通信的数据流是11 bits的数据符号的串联,每个数据符号包括1 bit的起始位、8 bits的数据位、1 bit的奇偶校验位、1 bit的终止位,以sdin的下降沿到来判断数据传输的开始,因此可在此之前设一个空闲状态。之后可设一个状态,8 bits的数据位接收设一个状态,1 bit的奇偶校验位可设一个状态、1 bit的终止位设一状态,如果fifo装满则full=1,FPGA就会检测full是否等于1来通过拉低sdin告诉FPGA停止发数据。因此共分为 6个状态,idle,start,data,parity,stop,full_stop。

1)idle状态,等待sdin的下降沿到来。

2)start状态,当sdin的下降沿到来时进入此状态,为8位有效数据的接收作准备。

3)data状态,八位数据的接收,把接收到的数据一位一位的存入到rcv_data,为fifo提供数据。

4)parity状态,当8位数据接收完则进入此状态,检测sdin口来进行奇偶校验,判断接收的数据是否正确,来设置rcv_error位,parity完成后进入stop状态。

5)stop状态,此位置 rcv_ready为 1,让 fifo接收数据,并存储该数据。

6)stop_full状态,检测 full是否为 1,如果为 1,则拉低sdin位并在此状态,否则进入下一状态idle。

串口具体状态图如图2所示。

图2 串口状态图Fig.2 State chart of serial ports

3 fifo的设计与实现

3.1 fifo的原理及功能

本文的fifo存储器采用的是同步设计方法。同步设计的fifo可以存储16个8位的数据。对fifo存储器设计也就对fifo控制信号的生成逻辑电路的读指针和写指针设计[6]。本文把引起读写的信号组成4种状态。00状态表示无读写,11表示读与写同时进行,01表示读一个数,10表示写一个数。当前状态为00,此时fifo内部存的数据的个数无变化,计数个数也不加不减。当进入01状态判断内部的数据是否为空,如果为空则设置相应的标志位,则告诉VGA_dis模块fifo的数据为空;如果当前状态为01状态则当前正处于从fifo中读一个数的状态,读完一个数后应该判断fifo中存的数是否为空也即是cnt是否为0,如果为空则设置使能标志位不让下一再读数了,同时当前存储器的个数cnt=cnt-1。如果当前状态为10状态则当前正处于从fifo中写一个数的状态,写完一个数后应该判断fifo中存的数是否为满,也即是cnt是否为16,如果为满则设置使能标志位不再写数据,同时当前存储器的个数cnt=cnt+1。

3.2 fifo与其他电路的配合工作

fifo是为VGA_dis与rcv_uart电路提供缓存。它的工作过程为,首先采集到一个数后存入到一个寄存器中,然后置位相应的使能位,相应的fifo读取刚才rcv_uart采集到的数,把该数存到fifo中。如果VGA_dis要写一个数则置位使能信号,fifo就送出一个数据放一个寄存器中,VGA_dis就会把fifo送出的一个数取出。rcv_uart在采集到一个数之后就会判断fifo是否已经满,如果满的话,则就置相应的fifo写使能为0同时不停的检测fifo中是否不满,如果不满就写一个数。当VGA_dis需要一个数时,就会判断fifo中是否有数,如果没有数就不取。

4VGA显示的设计

4.1 VGA显示的总体设计

VGA显示设计要满足一定的行场同步时序同时也必须与rcv_uart以及fifo很好的结合才能正常的工作。

每来一个时钟则就会向数据显示端口发出一组数据,当行场消隐时不发送数据,因此rcv_uart不能直接的与VGA_dis相连接,所以需要一个fifo。同时在行或场消隐信号时,可能会使fifo存满数据。因此rcv_uart在fifo存满时就要告知FPGA不要再发数据了。同时fifo数据为空或者复位时就有可能打乱VGA显示,使得不能正常显示,FPGA每发一次信号时就发一场数据。

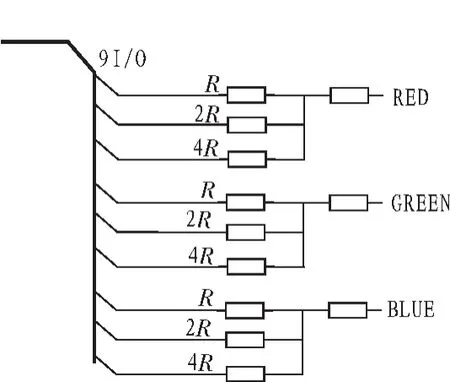

4.2 VGA接口电路与权值电阻

标准的VGA是15针D型接口,由R,G,B 3色模拟信号线和行,场同步两个数字信号构成。直接使用2根I/O口引脚作为同步信号,另外用9个I/O引脚通过由电阻网络构成的DAC作为R,G,B模拟信号 (R颜色3根,G颜色 3根,B颜色3根。)VGA的负载电阻是75 Ω,RGB模式信号的幅度是0.7 V,经过计算可以得出电阻网络中各电阻网络中各阻的值。如图3是VGA接口电路与权值电阻原理图。

图3 VGA接口电路与权值电阻Fig.3 VGA interface circuit and weights resistance

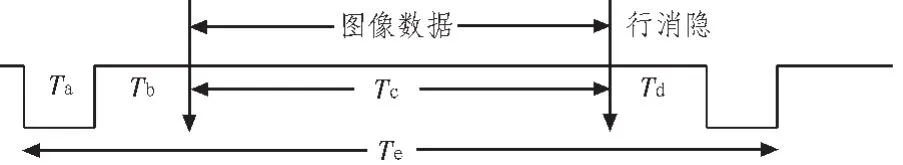

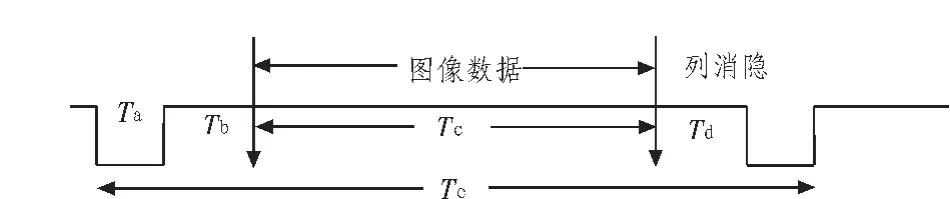

4.3 VGA同步信号设计

在VGA中,水平同步脉冲在光栅扫描线需要回到水平开始位置也是屏幕的左边的时候插入,垂直开始位置也就是屏幕的上方的时候插入。复合同步脉冲与垂直同步脉冲是水平同脉冲与垂直同步信号的组合。RGB为像素数据,在没有图像投射到屏幕时插入消隐信号,当消隐有效时,RGB信号无效。

在水平时序中,包括以下几个时序参数:水平同步脉冲Ta宽度为96个时钟周期:行消隐后沿Ta为48个时钟:视频数据Tc宽度为320个时钟;行消隐前沿Td宽度为16个时钟周期。一整行Te宽度为以上4项相加为480,如图4所示。当时钟频率不是25 MHz,以上参数可按比例进行适当的调整。

垂直时序与水平时序类似,包括以下几个不同的时序参数:垂直同步Ta宽度为2个时钟周期:列消隐后沿Ta宽度为32个时钟周期:视频数据Tc宽度为240个时钟周期;列消隐前沿宽度为11个时钟周期。一整场视频Te宽度为284个时钟周期,如图5所示。

图4 行扫描时序Fig.4 Scanning sequence

图5 列消隐时序Fig.5 Column vanish timing

5 结束语

由于本系统是基于FPGA设计的,因此,相比较以前使用的由小规模集成电路设计的视频采集卡而言,本系统具有可靠性高、性能稳定、开发灵活、调试简单、可以现场编程、设计成本降低、开发周期较短、屏幕显示质量高等特点。

[1]任爱峰,初秀琴,常存.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004:102-146.

[2]李广军,孟宪元.可编程ASIC技术及应用[M].西安:西安电子科技大学出版社,2000.

[3]夏宇闻.Verilog数字设计教程[M].北京:北京航空航天大学出版社,2003.

[4]柳亚东.基于FPGA嵌入式系统设计[M].北京:机械工业出版社,2004:89-96.

[5]郭树涛,靖永志.基于FPGA的串口通信设计[J].北京电子科技学院学报,2006,14(4):74-78.GUO Shu-tao,JING Yong-zhi.Serial communication based on FPGA [J].JournalofBeijing Electronic Science and Technology Institute,2006,14(4):74-78.

[6]朱如龙.基于FPGA的LED显示屏VGA同步图像采集设计[J].电子工程师,2004(10):44-45.ZHU Ru-long.LED display VGA synchronous image acquisition design based on FPGA[J].Electronic Engineer,2004(10):44-45.