基于C8051F060的高速凸轮测试系统设计

2011-05-10李树军徐永新

姜 恒,李树军,徐永新

(西北工业大学 机电学院,西安 710072)

0 引言

凸轮机构是一种由凸轮、从动件和机架组成的高副机构。凸轮机构能实现复杂的运动要求,因而广泛应用于各种自动化、半自动化机械装置中。凸轮机构高速运转时,系统中从动件的惯性力急剧增大,构件弹性形变的影响会使输出端的运动规律偏离预定的要求,产生严重的运动偏差[2]。针对高速凸轮在高速运转时出现的实际问题,国内外学者进行了大量的理论分析研究,但相关的实验研究比较缺乏。

本文介绍了一种利用C8051F060单片机以及美国NI公司的LabWindows/CVI虚拟仪器开发工具构建的高速凸轮测试系统,通过该测试系统获得凸轮机构在高速运转时的动力学参数数据,进而从实验角度对高速动态性能进行分析研究,为高速凸轮动力学研究奠定良好的基础。

1 总体方案设计

1.1 机械结构简介

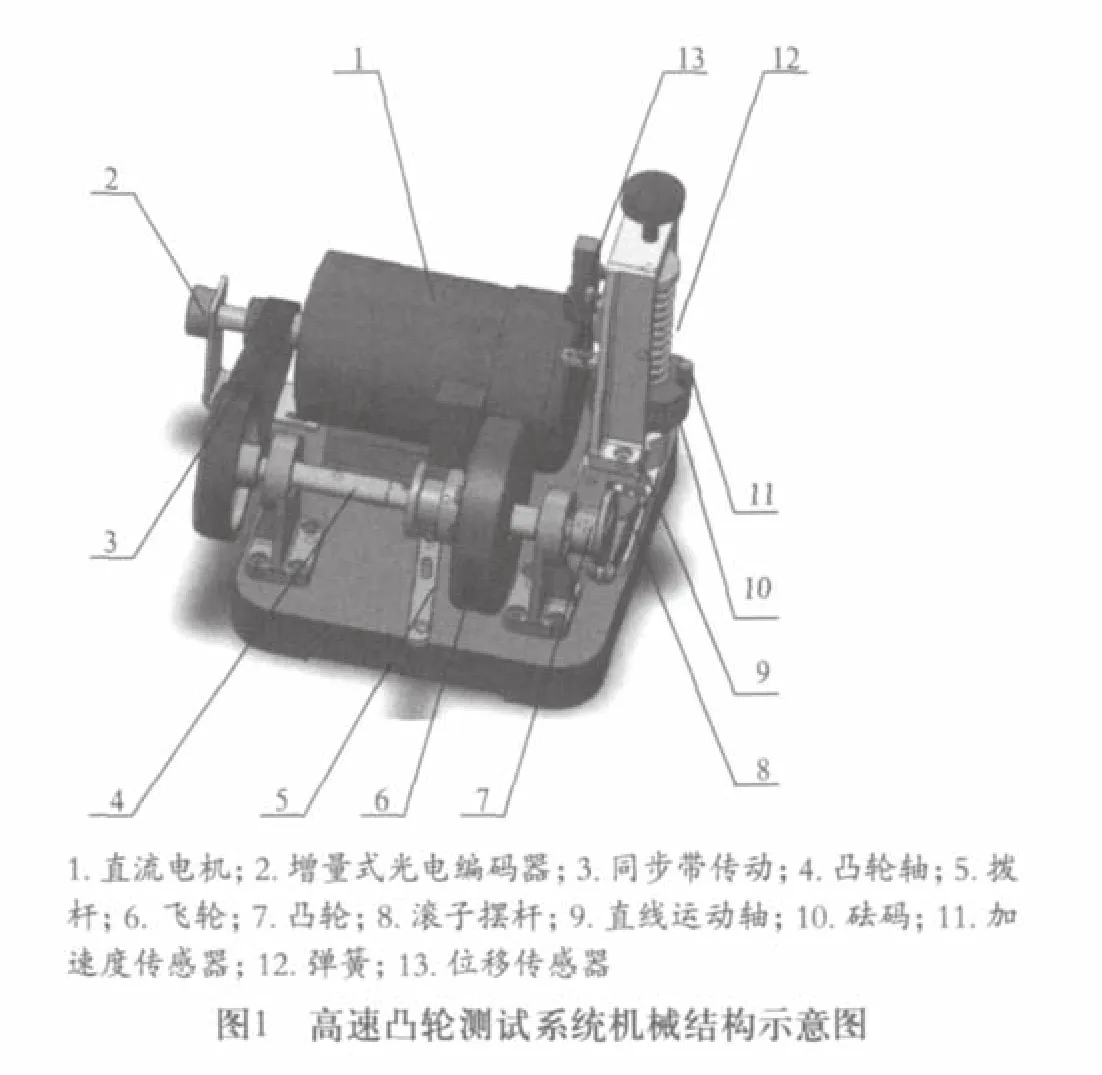

高速凸轮测试系统通过测量凸轮机构的转速、位移以及加速度来研究高速凸轮机构的动态性能。高速凸轮测试系统主要包括机械结构和数据采集系统两部分。其中机械结构如图1所示。

在图1所示的结构中,1为直流电机,直流电机通过同步带传动带动4凸轮轴旋转。直流电机的最高转速为3000r/min,带传动的传动比为1∶3,因此凸轮轴的最高转速为1000r/min。凸轮7通过键与凸轮轴4连接,利用紧定螺钉轴向固定,可以方便地更换凸轮。飞轮6可以通过拨杆5方便的从系统中加载或移除,从而改变系统的转动惯量。8为滚子摆杆,两端装有滚子,可以减少磨损。滚子摆杆一端与凸轮接触,另一端与直线运动系统相接触。直线运动系统由直线运动轴9、砝码10和弹簧12组成,可将凸轮的旋转运动转化为直线运动系统的直线运动。凸轮机构的转速由增量式光电编码器2测量。加速度与位移通过固连在砝码上的加速度传感器11和位移传感器13测量。

1.2 数据采集系统方案设计

数据采集系统主要由传感器、传感器适配器、数据采集卡和上位机组成。由于测试系统的最小采样周期为0.16ms,常用的数据“采集卡+Windows操作系统”的方法无法满足测试系统的要求。因此本测试系统选用以高速单片机为核心搭建数据采集卡。传感器输出的信号经适配器放大后,由高速单片机进行采集,所得的数据首先存入单片机的外存储器。采集工作结束后,再将数据发送至上位机,由上位机进行处理。通过这种方法满足测试系统的要求。

本系统以美国Silicon Laboratories 公司的C8051F060单片机作为核心。该型号单片机其片上集成有与高速流水线结构的8051兼容的CIP-51内核(速度可达25MIPS); 2个16位、1Msps的ADC;5个通用的定时/计数器;1个带6个比较/捕捉模块的可编程定时/计数器阵列[4],完全符合本系统的要求。

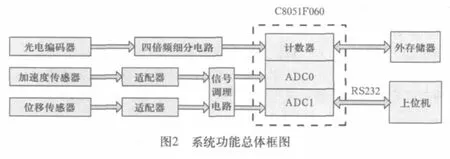

光电编码器输出的信号经四倍频电路细分后由单片机内部集成的计数器进行计数,加速度传感器和位移传感器输出的模拟信号经信号调理电路后由16位的模数转换器ADC0和ADC1进行采集。由于ADC0和ADC1的启动方式可以设置为定时器T3溢出启动,因此选择定时器T3控制信号的采样周期。系统工作时,首先测得凸轮机构在一个周期内的转速平均值,通过转速平均值计算出系统的采样周期,进而确定定时器T3的初值。定时器T3发生溢出时,执行定时器T3中断服务程序,存储计数器的计数值,自动开启ADC0和ADC1,待AD转换结束后将所得的结果存入外存储器。当计数器发生溢出时,采样过程结束,并将所得的全部数据经RS232总线发送至上位机,系统的功能框图如图2所示。

2 系统硬件设计

2.1 四倍频细分电路设计

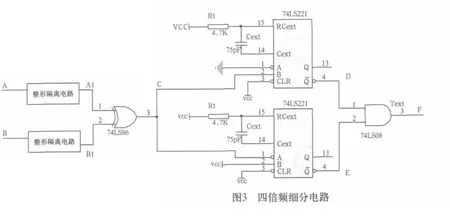

在高速凸轮测试系统中,转速信号的测量是其中的关键。测试系统的一个重要功能就是测试凸轮机构在不同转速、不同负载情况下的转速波动情况。考虑到测试系统采用增量式光电编码器测量转速,为提高系统对转速的测量精度,根据光电编码器输出的A相和B相信号相位相差90°的基本原理,设计了光电编码器四倍频细分电路。四倍频电路如图3所示。

在图3所示的电路中,光电编码器输出的A、B相信号首先经过整形隔离电路后得到A1、B1信号。由于A1、B1信号相位相差90°,因此将A1、B1信号接入异或门电路74LS86进行异或运算,输出的信号C其频率为输入信号频率的两倍。

两倍频信号C经过两路单稳态触发器74LS221分别检测出上升沿和下降沿。该触发器由于内部的补偿作用,输出脉冲的宽度稳定性好。脉冲宽度的大小取决于电阻Rt和电容Cext的大小。实际应用中,Rt的值选为4.7K,Cext的值选为75pF。74LS221负脉冲输出端输出的两路信号D、E接入与门电路74LS08获得四倍频信号F。信号F最终接入单片机计数器的信号输入引脚进行计数。

2.2 模拟信号调理电路设计

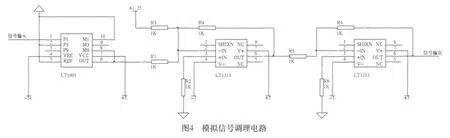

在测试系统中,由于加速度传感器的输出信号为-5~+5V,位移传感器的输出信号为0~+5V,而ADC1和ADC2的输入信号范围为0~VREF(VREF的值为2.5V),因此必须设计信号调理电路将±5V信号转换为0~2.5V。信号调理电路设计如图4所示。

在图4所示的电路中,输入的±5V信号首先经LT1991降压后转换为±1.25V,LT1991是一款精准、增益可选放大器,通过改变引脚的接法可以获得不同的增益,当按图示的接法连接电路时,其增益为0.25。输入信号经LT1991降压后,在通过集成运算放大器LT1363同1.25V的基准电压做反相加法运算,将±1.25V的信号转换为0~-2.5V。最后经反相比例运算电路调整为0~2.5V,输入C8051F060的AIN0和AIN1引接进行采集。其中1.25V和2.5V的基准电压分别由电压基准芯片REF2912和REF2925产生。

2.3 外存储芯片选型

由于C8051F060内部集成的外存存储器容量为4K,无法满足测试系统的要求,所以必须扩展外存容量。本方案中,考虑到C8051F060可扩展的外存容量为64K,因此选用IDT71V124SA12PH实现存储器的扩展。IDT71V124SA12PH是一款3.3V供电的、CMOS静态RAM,其存储容量为128K,完全符合测试系统的要求。C8051F060通过专用的EMIF接口配置外存储器,包括复用方式与非复用方式得选择、存储模式的选择以及时序的设置。

2.4 通信接口电路设计

由于测试系统全部的数据显示工作都由上位机完成,因此必须保证下位机与上位机的通信功能。本系统采用RS232的通信方式。接口芯片选择MAXIM公司的MAX3232。MAX3232芯片是一款3.0V至5.5V供电、低功耗、1Mbps、真RS232收发器。在使用时,只需要外接4只0.1uF的电容,就可以完成数据传输、通信的功能。

3 系统软件设计

3.1 下位机软件设计

高速凸轮测试系统下位机(即C8051F060)软件设计的一个难点是四倍频脉冲信号的计数程序。系统选用的编码器为美国EPC公司的15S系列编码器,每转输出10000个脉冲信号。而上位机显示的凸轮运动周期最多为3个周期,因此凸轮旋转3周,电机旋转9周,编码器输出90000个脉冲,经四倍频细分电路后输出360000个脉冲。C8051F060内部集成的计数器均为16位,最多能计数65536个脉冲信号,无法满足测试系统的要求。本系统利用C8051F060内部的计数器PCA0和T0搭建了一个24位的计数器,并设计了相应的软件算法,从而实现了对360000个脉冲信号的计数。

可编程定时/计数器阵列PCA0的时基信号可以由定时器/计数器T0溢出获得,即T0每溢出一次,PCA0计数值加1。因此可以设置由T0对四倍频信号进行计数,T0工作在8位自动重装载方式下,重载值和初值均为56,即T0每计数200个脉冲信号产生一次溢出。PCA0的时基信号由T0溢出获得,PCA0的计数初值设置为63736,即PCA0计数值达到1800时,针对四倍频信号的计数达到360000。某一时刻的计数值由以下公式确定:计数值=(PCA0-63736) ×200+TL0-56 (1)

PCA0为当前PCA0寄存器的计数值,T0L为当前T0寄存器的计数值。这种计数方法的突出特点是两个计数器的连接完全通过单片机内部配置寄存器实现,无需在单片机外部进行连线,从而提升了系统的计数精度和抗干扰性能。

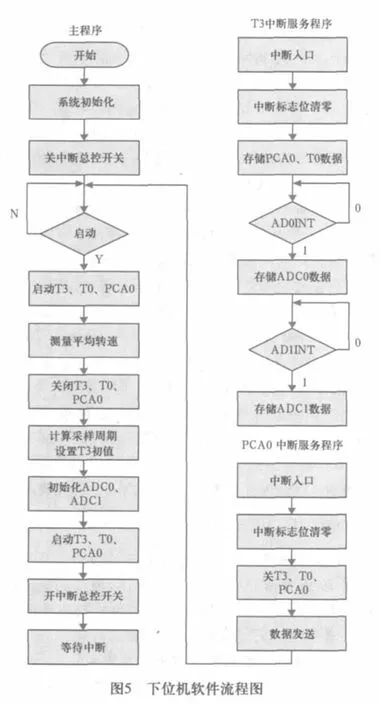

综上所述,下位机软件主要包括系统初始化程序、采样周期设置程序、ADC初始化程序、定时器T3中断服务程序以及PCA0中断服务程序。系统工作时,首先执行系统初始化子程序。在系统初始化程序中需要配置系统时钟、I/O端口、EMIF接口、串行接口UART0、定时器T3、定时器T0、PCA0以及中断优先级寄存器。在系统采样周期设置程序中通过测量凸轮的平均转速确定好采样周期,并设置定时器T3的初值。在ADC初始化程序中确定AD转换时钟和启动方式。在定时器3中断服务程序中,每当定时器发生中断时,PCA0和TL0的计数值存入外存,自动开启ADC0和ADC1进行采样,待AD转换结束后将寄存器ADC0、ADC1的值存入外存。在PCA0中断服务程序中,当PCA0发生中断时,通过串行接口UART0将外存中的数据发送至上位机。下位机程序的流程图如图5所示。

3.2 上位机测控软件设计

在测试系统中,上位机与下位机C8051F060需要进行通信。上位机需要发送控制指令下位机。下位机采集数据结束后,需要发送数据给上位机。上位机接收到数据后,要对数据进行滤波,运算,并以曲线的形式进行显示。通过上位机测控软件可以方便的实现上述功能。本测试系统利用虚拟仪器开发工具LabWindows/CVI编写了一套高速凸轮试验系统上位机测控软件。

LabWindows/CVI是 美 国 NI(National Instrument)公司推出的32位面向计算机测控领域的虚拟仪器开发平台,可以在多个操作系统下运行,利用C语言编程,可以方便快速搭建自定义测控平台。此外模块化的数据处理方法,使软件开发效率得到极大的提升且易于升级[7]。

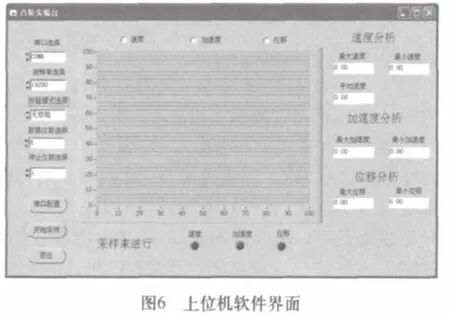

本上位机软件的功能是,通过配置打开串口,向下位机发送控制指令,接收下位机传送的凸轮机械运动参数数据。通过函数OpenComConfig()打开串口并进行相关的配置。数据的接收与发送则是通过函数ComRd()与ComWrt()实现。上位机接收到数据后,通过对数据进行滤波、运算,最终在图形框中以曲线的方式进行显示。上位机的界面如图6所示。

4 实验验证

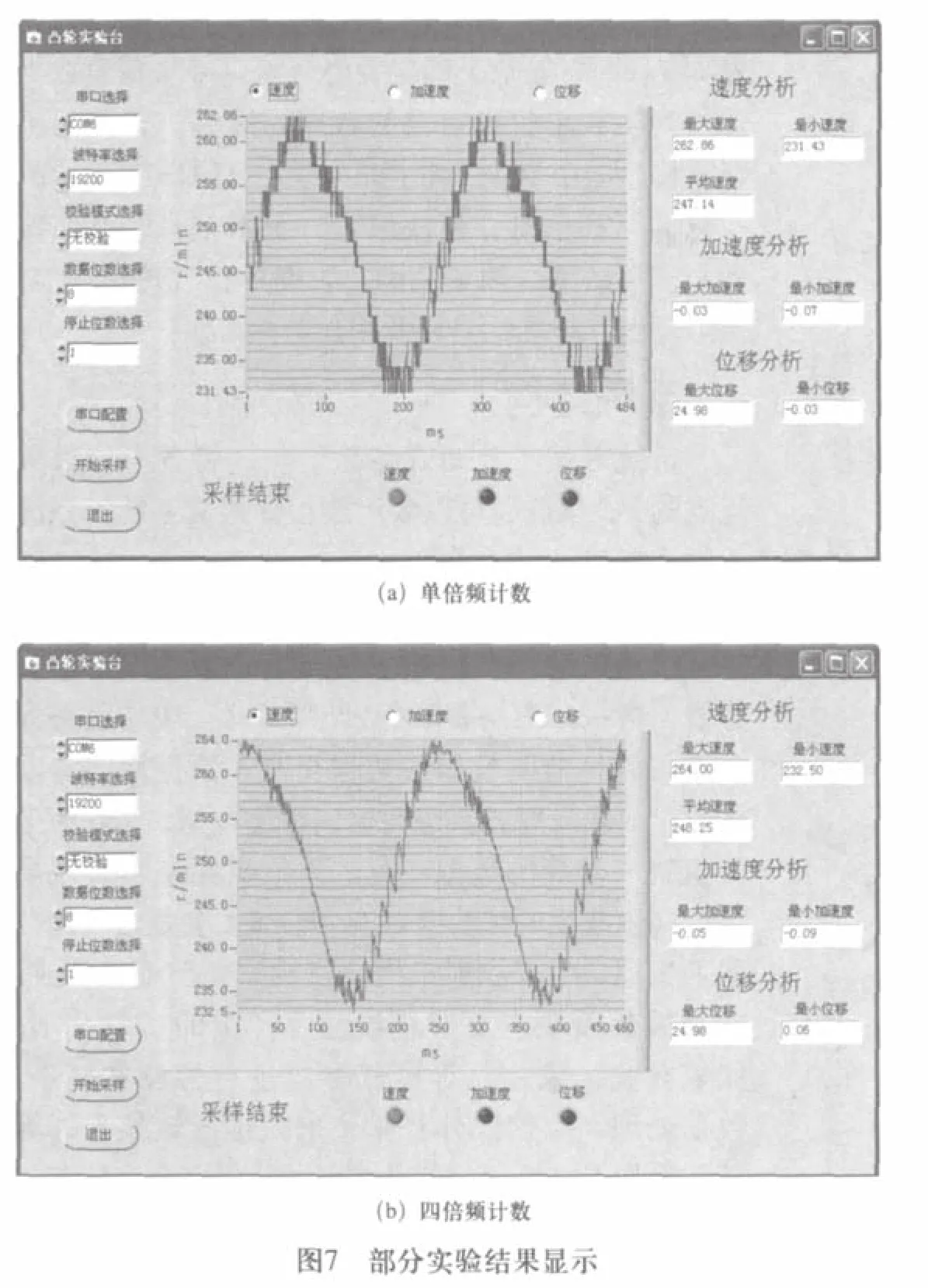

为了验证方案的可行性,制作了采集系统样机并与现有的高速凸轮测试系统进行系统联调。图7是高速凸轮测试系统的部分实验结果,其测试条件为凸轮转速247r/min,试验凸轮为圆偏心凸轮,未加飞轮,显示周期为2周期。

图7(a)为采用单倍频计数时的转速波动曲线,图7(b)为采用四倍频计数时的转速波动曲线。从图中可以看出,当采用四倍频计数时,转速波动曲线更加光滑,更加接近于理论曲线。从而表明采用四倍频电路可以提高系统的采集精度。

5 结束语

凸轮机构是一种在工业领域应用非常广泛的机构,有关于它的实验研究在国内尚处于起步阶段。本方案设计了基于C8051F060的高速凸轮测试系统并制作了样机,对研究凸轮高速运转时的进行了初步研究。在后续调试中还要对采集卡以及程序的优化进行一系列改进。

[1] 孙树峰, 周以齐.基于非均匀有理B样条的空间凸轮设计[J]. 机械工程学报, 2009, 45(8): 125-129.

[2] 苏利亚.高速凸轮机构的动力学分析[J].机械设计与制造, 2008, 12: 181-182.

[3] 安永如, 黎海文, 吴一辉, 宣明. 基于C8051F060的微型生化分析仪高速数据采集系统[J].光电子技术, 2007, 27(3): 166-173.

[4] 潘琢金.C8051F060/1/2/3/4/5/6/7混合信号ISP FLASH 微控制器数据手册[Z].深圳: 新华龙电子有限公司, 2004.

[5] 张培仁, 孙力.基于C语言C8051F系列微控制器原理与应用[M].北京: 清华大学出版社, 2007.

[6] 罗辉,李树军,王亮, 邓宏德.基于LabWindows/CVI和 RTX的高速凸轮测试系统设计[J].测控技术,2011,30(2):23-26.

[7] 史君成, 张淑伟, 律淑珍.LabWindows/CVI虚拟仪器设计[M].北京: 国防工业出版社, 2007.

[8] 孙晓云, 郭立炜, 孙会琴.基于LabWindows/CVI的虚拟仪器设计与应用[M].北京: 电子工业出版社, 2006.