一种软件电台的基带处理架构及频偏估计设计

2011-04-17韦照川卢洪荣欧阳宁孙希延

韦照川,卢洪荣,欧阳宁,孙希延

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

1 系统硬件方案

软件无线电技术基于通用的可编程硬件平台,把尽可能多的通信功能用软件来实现,从而使系统的改进和升级都非常方便,容易实现不同通信系统之间的兼容。文献[1-2]对软件无线电的一些特点和具体应用做了介绍。本文以FPGA+DSP+ARM为核心,FPGA适用于并行处理,速度快,功耗低,但是不适合复杂算法。DSP可编程能力强,在数字信号处理方面具有较大优势且程序设计相对于FPGA容易。基于对资源和运算速度等综合考虑,采用FPGA完成数字变频、位同步和符号同步,DSP完成载波同步、均衡和解调等处理。ARM实现人机界面和总体控制。图1是软件无线电台的基带信号处理板的系统框图,由FPGA实现与A/D,D/A变换器的接口。

图1 硬件系统框图

ARM采用恩智浦公司基于ARM7TDMI-S的内核微处理器LPC2478;FPGA采用Altera公司的CycloneIII系列EP3C40Q240C8N;DSP采用TI公司的TMS320C6000系列TMS320C6713B浮点处理器。TMS320C6713B主频最高达300 MHz,有8个并行处理单元,峰值指令速度(即浮点运算次数)为2.4×109,外接一个语音芯片AIC23B实现语音采集和回放的功能。ARM,FPGA,DSP相互之间通过EMIF接口连接,FPGA还连接DSP的GPIO6和GPIO7管脚,发送定时脉冲作为EDMA通道的同步事件,实现数据传输。

2 DSP软件架构

DSP基带信号处理的流程如图2所示,由3个中断服务程序共同完成基带信号处理。McBSP1的发送中断(XINT1)服务程序完成音频数据的采集和解调后数据的回放;EDMA通道6传输完成中断服务程序发送端的基带信号处理,包括调制和帧形成;EDMA通道7传输完成中断服务程序接收端的基带信号处理,包括频偏估计、自适应均衡和解调。McBSP1发送中断的优先级比另外2个EDMA传输完成中断的优先级低。

2.1 数据帧结构

图2 DSP软件流程图

AIC23B采样速率设置为8 kHz,码元宽度为125 μs。不同的调制方式有不同的帧长度,BPSK调制方式帧长度为33.75 ms;QPSK调制方式帧长度为67.5 ms;16QAM调制方式帧长度为135 ms。帧数据的前14个是帧同步信号,用作信号到达检测和频偏估计。2个用作调制类型选择,则I,Q两路共有16种方式可选,用来通知接收端下一帧采用的调制类型;14个作为频点和地址选择,用来通知接收端下一帧的调制频点,I,Q两路共有28位;240个有效数据,但数据长度根据需要可扩展。图3为BPSK调制方式帧结构。

2.2 发、收端基带信号处理

发送端发送帧同步信号为(1,1,1,0,1,0,0,1,1,1,0,1,0,0),I,Q两路相同。音频数据的采集和回放在McBSP1发送中断服务程序中完成。当XINT1到来时,AIC23B的A/D以8 kHz的采样速率采集音频数据。每次采集数据为32位,为了减轻接收端数据处理压力,在发送端只发送左声道的8位数据。将8位整形数据保存于一维数组,数组的大小由调制方式决定。BPSK调制时,数组大小为30;QPSK调制时,数组大小为60;16QAM调制时,数组大小为120。XINT1中断一次,计数器加1,当计数器达到30,60或120时,计数器归0,重新开始计数。与此同时,将接收端缓冲区解调好的数据通过McB⁃SP1的DXR寄存器传输到AIC23B的D/A转换器进行声音回放。

在EDMA通道6传输完成中断服务程序实现调制和帧形成。将AIC23B采集的每帧信源数据先进行调制,然后按照图3的帧结构保存在乒乓缓存数组中,再将所有发送数据进行满量程映射。最后将数据通过EDMA通道6传给FPGA,在FPGA中完成成型滤波、内插和上变频,将信号传送给D/A变换器。

接收端需要进行大量运算,比如频偏估计、自适应均衡和解调,需要消耗比较多的运算资源,也采用EDMA通道传输数据。当外部中断7同步事件触发时,FPGA通过EDMA通道7将基带数据传输给DSP,传输完一帧数据后产生一个CPU中断,在中断服务程序中完成基带信号的频偏估计、均衡和解调等处理。

3 频偏估计与纠正

因为频偏估计与纠正在通信系统中起着关键作用,所以着重介绍频偏估计原理与实现方法,文献[3-5]介绍几种频偏纠正方法,本文中因为在FPGA中已经完成位同步,在DSP中要完成频偏估计,相位同步这里不作介绍,可以由后端的均衡器实现。

3.1 频偏估计原理

本文采用发送导频信息的数据辅助估算法并结合反正切算法来估算频偏,并对频偏进行纠正软件无线电的各种通信信号采用正交调制的方法来完成,为了保证解调顺利进行,在每一帧数据前插入导频信息。导频信息既可以用作信号到达检测,也可以用作频偏估计。在每一帧数据的帧头插入间隔为Dist的导频信息(Pn序列)

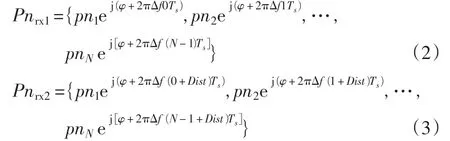

由于在传输过程中存在初始相位和固定频偏,所以接收端接收到的信号为

式中:φ是载波相位,Δf为载波的频偏,Ts为FPGA传输给DSP的基带码元速率。因此

式中:∗表示复数取共轭。所以

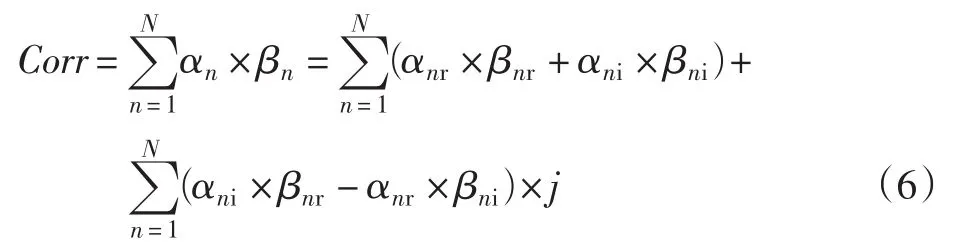

式中:arg[·]表示取复数的辐角。由式(5)可知,要求解频偏,关键是求解接收序列的互相关。假设复数序列为A={α1,α2,…,αN}和B={β1,β2,…,βN},则A和B的互相关(Corr)定义为

式中:αnr,αni,βnr和 βni分别为αn以及 βn的实部和虚部。一个复数的共轭乘法为

根据式(6)和式(7)可以求解出复数序列A和B的互相关。由伪随机序列的特性可知

3.2 具体实现

频偏估计按照3.1节所示原理设计,由式(5)可知,频偏估算范围和Dist,Ts有关,在Ts确定的情况下,Dist与频偏估算范围成反比。实际仿真测试发现,Dist还与频偏估计的精确度成正比,因此频偏估算范围和精确度是成反比的,那么可以采用2个步骤来解决这个问题。接收到第一帧数据时,将这一帧数据的前14个帧头数据用作粗频偏估计,得到的频偏通过DSP发送给FPGA,让FP⁃GA通过计算改变DDS的频率控制字,使频偏得到大致的纠正;在后续帧数据的频偏估计中采用相邻两帧帧头的前7个数据作为频偏估计的数据,使频偏得到精确估计,同时也将每次得到的频偏送到FPGA的DDS,通过DDS的调整,消除剩余的频偏。

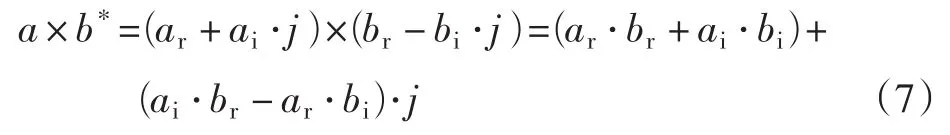

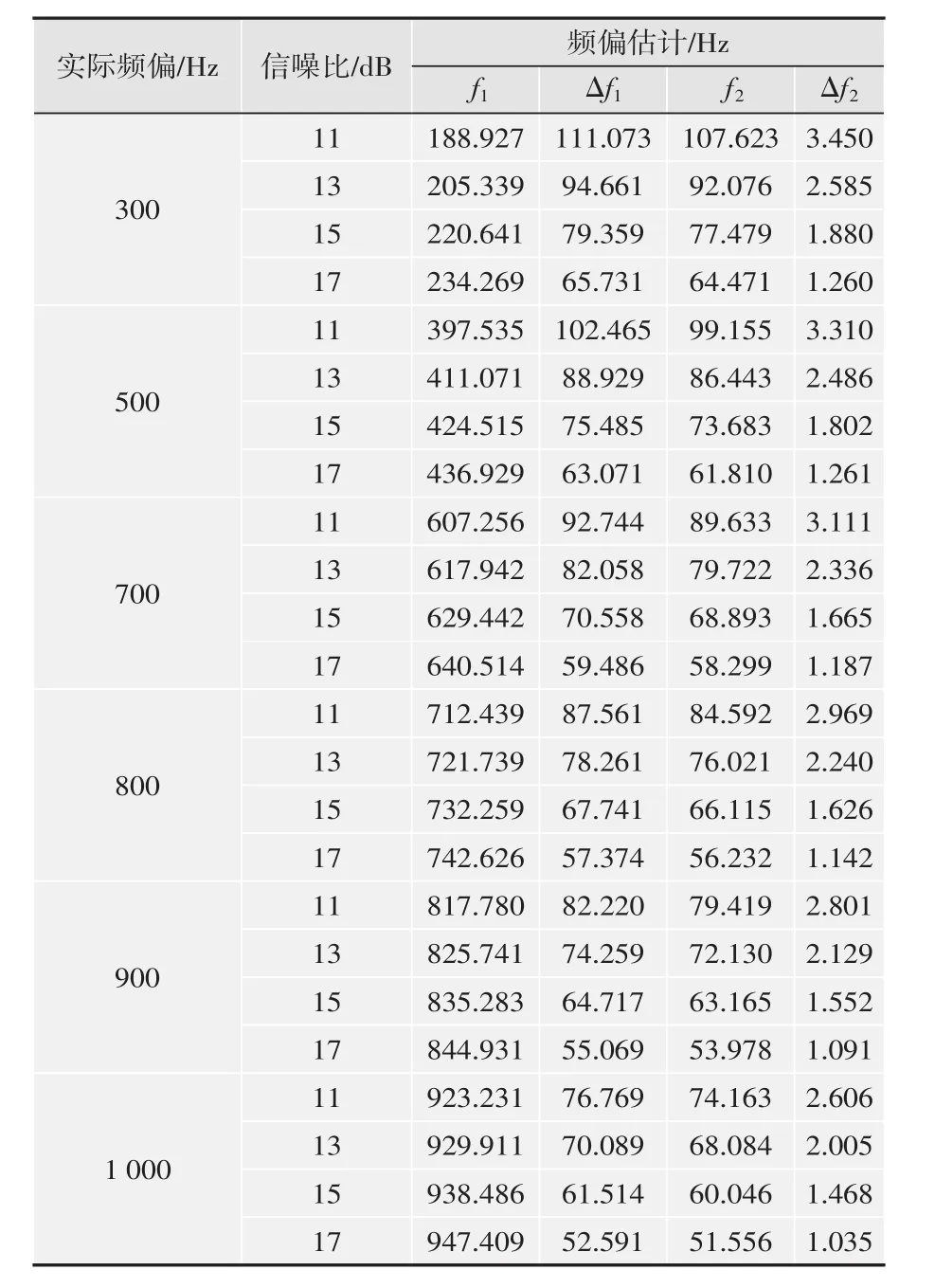

以BPSK调制方式为例,接收到的码元速率是72 kbit/s,在给定信噪比的情况下对频偏进行估计,数据如表1所示。其中f1表示采用同一帧的14个帧头作为频偏估计的数据所得到的频偏估计值,即Dist。Δf1为剩余频偏。f2是对Δf1采用精细频偏估计所得的估计值,即Dist=270。Δf2是最后的剩余频偏。从表1中可以看出,采用同一帧的14个帧头作为频偏估计的估算数据,在频偏较小时,估计相对误差比较大,采用相邻两帧的前7个帧头数据作为频偏的估算数据,估计误差比较小。

表1 频偏估计值

4 小结

最后整个系统包括DSP模块、FPGA数字变频模块、A/D和D/A模块进行闭环联调,AIC23B通过线输入采集音频数据,调制后传输到FPGA完成上变频,数字中频为10 MHz;经过D/A,A/D变换然后进行下变频到基带,这里加入了适当频偏,接着将基带数据送到DSP解调并进行回放,通过耳机听回放后的效果。在实验室范围内进行简单的主观评价测试,其语音质量平均MOS分可达优[6],证明系统设计正确。

[1] TUTTLEBEE W H W.Software-defined radio:facets of a developing technology[J].IEEETrans.PersonalCommunications,1999,6(2):38-44.

[2] 谢印庆.软件无线电中GMSK与QPSK调制解调及其TMS320C6711 DSP实现的研究[D].太原:太原理工大学,2006.

[3] 郑大春,项海格.一种全数字化载波频偏估计器算法[J].电子学报,1999,27(1):78-80.

[4] 储士平,张邦宁,郭道省,等.一种适合软件无线电的载波相位和频差估计算法[J].北京理工大学学报,2005,25(5):443-446.

[5] 方绍,谢显中.基于DVB-T的OFDM频偏估计算法及DSP实现[J].电视技术,2011,35(3):5-8.

[6]MOS语音质量评测指标的介绍[EB/OL].[2010-12-25].http://wenku.baidu.com/view/a4edc25f804d2b160b4ec0c3.html.