武器装备印制板级电磁兼容性设计方法探讨

2011-03-30付本玉赵凯

付本玉,赵凯

(中国船舶重工集团公司第七一三研究所,河南 郑州 450015)

武器装备印制板级电磁兼容性设计方法探讨

付本玉,赵凯

(中国船舶重工集团公司第七一三研究所,河南 郑州 450015)

介绍了电磁环境的组成,引出电磁兼容问题产生的原因,然后提出印制板的电磁兼容设计要求,为了达到这些要求,从元器件的布置、地线和电源线的布置、信号线的布置3个方面详细介绍了印制板的设计方法。

印制板级;电磁兼容性;阻抗匹配

当前我们已经进入信息化时代,信息化时代的武器装备对电磁兼容的要求越来越严格。系统的电磁兼容性,是所有武器装备面对的一个重要问题。为了提高整个系统的电磁兼容性,设计者必须从最基础的印制板级的电磁兼容性抓起。印制板是构成数字电子设备的基础,是使设备达到电磁兼容要求的最关键部分,也就是说,印制板级的电磁兼容是系统电磁兼容性的基础。

1 电磁环境的组成

电磁干扰的基本模型由3部分组成:电磁干扰源,耦合和路径,接收机。

电磁干扰源包含微处理器、微控制器、静电放电、瞬时功率执行元件等。随着大量高速的半导体器件的应用,其边沿跳变速率非常快,这种电路可以产生高达300MHz的谐波干扰。

耦合路径可以分为空间辐射电磁波和导线传导的电压和电流。噪声被耦合到电路中的最简单方式,是通过导体的传递,例如,有一条导线在一个有噪声的环境中经过,这条导线通过感应接受这个噪声,并且将它传递到电路的其他部分。

所有的电子电路,都可以接受传送的电磁干扰。例如,在数字电路中,临界信号最容易受到电磁干扰的影响;模拟的低级放大器、控制电路和电源调整电路,也容易受到噪声的影响。

2 印制板的布线和设计

良好的印制板布线,在电磁兼容性中是一个非常重要的因素,一个拙劣的印制板布线和设计,会产生很多电磁兼容问题,即使加上滤波器和其他元器件,也不能解决这些问题。正确的电路布线和设计应该达到如下3点要求:

(1)板上的各部分电路之间干扰,都能正常工作;

(2)印制板对外的传导发射和辐射发射,尽可能的低,达到有关标准要求;

(3)外部的传导干扰和辐射干扰,对印制板上的电路没有影响。

2.1 元器件的布置

(1)首要问题是对元器件进行分组。元器件的分组原则有按电压不同分,按数字电路和模拟电路分,按高速和低速信号分和按电流大小分。一般情况下都按照电压不同分。

(2)所有的连接器都放在印制板的一侧,尽量避免从两侧引出电缆。

(3)不要让高速信号线靠近连接器。

(4)在元器件安排时,应考虑尽可能缩短高速信号线,如时钟线、数据线和地址线等。

2.2 地线和电源线的布置

(1)地线的布置。地线布置的最终目的,是为了最小化接地阻抗,以此减少从电路返回到电源之间的接地回路电势。减少回路电势,就是要减少电路从源端到目的端线路和地层形成的环路面积。通常增加环路面积,是由于地层隔缝引起的。如果地层上有缝隙,高速信号线的回流线就被迫要绕过隔缝,从而增大了高频环路的面积。

(2)电源线的布置。电源线的布置要和地线结合起来考虑,以便构成特性阻抗尽可能小的供电线路。为了减小供电用线的特性阻抗,电源线和地线应该尽可能的粗,并且相互靠近,使供电回路面积减到最小,而且不同的供电环路不要相互重叠。在集成芯片的电源脚和地脚之间,要加高频去耦电容,容量约为0.01~0.1μF,而且为了进一步提高电源的去耦滤波的低频特性,在电源引入端要加上一个高频去耦电容和一个1~10μF的低频滤波电容。

(3)多层印制板中的电源层和地层的布置。在多层印制板中,电源层和地层要放置在相邻的层中,从而在整个印制板上产生一个大的PCB电容,来消除噪声。速度最快的关键信号和集成芯片,应当布放在临近地层一边,非关键信号则布放在靠近电源层一边。因为,地层本身就是用来吸收和消除噪声的,其本身几乎是没有噪声的。

2.3 信号线的布置

2.3.1 不相容的信号线应相互隔离

不相容的信号线之间,能产生耦合干扰。所以在信号线的布置上,我们要把它们隔离,隔离时采取的措施有:

(1)不相容信号线应相互远离,不要平行,分布在不同层上的信号线走向,应相互垂直,这样可以减少线间的电场和磁场耦合干扰;

(2)高速信号线,特别是时钟线,要尽可能地短,必要时可在高速信号线两边加隔离地线;

(3)信号线的布置,最好根据信号流向顺序安排,一个电路的输入信号线,不要在折回输入信号线区域,因为输入线和输出线通常是不相容的。

2.3.2 注意线路终端的阻抗匹配问题

当高速数字信号的传输延时时间Td>Tr时,Tr为信号的脉冲上升时间,应考虑阻抗匹配问题。因为错误的终端阻抗匹配,将会引起信号反馈和阻尼振荡。通常线路终端阻抗匹配的方法有4种:串联源端接法,并联端接法,RC端接法,Thevenin端接法。下面就详细研究RC端接法方法和Thevenin端接法的使用方法和特性。

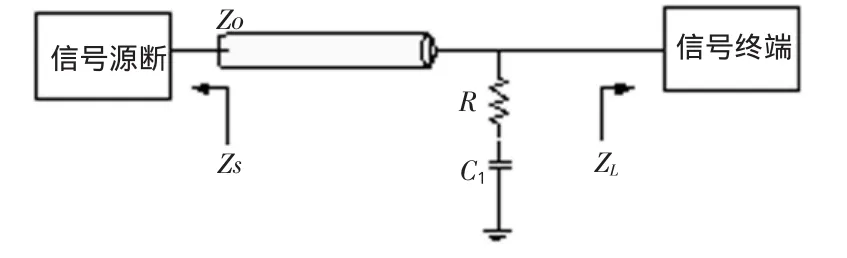

(1)RC端接法。图1中为RC端接电路。这个方法类似于并联端接电路,但是引入了一个电容C1,此时R用于提供匹配Zo的阻抗。C1为R提供驱动电流并过滤掉从传输线到地的射频能量。因此相比并联端接方法,RC端接电路需要的源驱动电流更少。R和C1的值由Zo,Tpd(环路传输延迟)和终端负载电容值Cd决定。时间常数,RC=3×Tpd,其中R//ZL=Zo,C=C1//Cd。

图1 RC端接电路

(2)Thevenin端接法。图2中为Thevenin端接电路。此电路由上拉电阻R1和下拉电阻R2组成,这样就使逻辑高和逻辑低与目标负载相符。其中,R1和R2的值由R1//R2=Zo决定,R1+R2+Z l的值要保证最大电流不能超过驱动电路容量。

图2 Thevenin端接电路

3 结束语

为了适应当前的信息化战争,所有武器装备都必须达到相应的国军标电磁兼容要求,所以电磁兼容在电子设备设计中的重要地位,越来越突出。但是,设备自动化、信息化程度越高,达到国军标的电磁兼容要求越难。印制板极的电磁兼容设计,是所有电子设备的基础,在设计过程中,为了达到相应的要求,设计者如果能够按照上面所有的建议,就能减少不合理的电路设计和印制板的布线,为达到设计要求奠定好的基础。

[1]沙 斐.机电一体化系统的电磁兼容技术[M].北京:中国电力出版社,1999.

[2]System Design and Layout Technique for Noise Reduction in Mcu-Based Systems,Motrola Application Note,AN1259.

[3]郭银景,等.电磁兼容原理及应用教程[M].北京:清华大学出版社,2004.

Naval Weapons and Equipment on the PCB Level EMC Design Method

FU Ben-yu,ZHAOKai

(713 th Research Institute of China Shipbuilding Industry Corporation,Zhengzhou 450015,China)

describes the electromagnetic environment of the composition,leds to the cause of the problem of electromagnetic compatibility;Then,we propoased EMCPCB design requirements,in order to meet these requirements,from components of the arrangement,the arrangement of ground and power lines,signal lines of the arrangement described in detail three aspects of PCB design.

PCB level;electromagnetic compatibility;impedance matching

TN41

B

1672-545X(2011)08-0172-02

2011-05-18

付本玉(1975—),男,山东郓城人,工程师,本科学历,主要从事导弹发射装置可靠性和电气控制系统的研究;赵 凯(1982—),男,河南新郑人,工程师,硕士学位,主要从事导弹发射装置电气系统的研究。