基于FPGA的地震计标定信号发生器的设计与实现

2011-03-26黄儒章国宝黄永明

黄儒,章国宝,黄永明

(东南大学自动化学院,江苏南京210096)

地震计是地震台的基本设备之一。地震计的标定过程是对地震计特性参数进行评判的一种简易手段。它将特定的标定信号输入至地震计的标定线圈内,由于电磁感应原理,标定线圈与磁钢之间产生的策动力矩迫使摆产生振动,从而在工作线圈中产生电压输出,通过分析输出与输入信号之间的幅值、相位关系等,可以基本掌握地震计的工作性能[1]。

使用不同的信号标定,可以获得地震计的各种不同的参数和性能。地震计常用标定信号有正弦信号、方波信号、伪随机二进制信号等。笔者设计一款基于FPGA的地震计标定信号发生器,是地震电磁信息采集系统的子模块,能产生标定所需信号,与地震电磁信息采集系统一起完成地震计的标定工作。

1 信号发生原理

1.1 DDS(直接数字频率合成)技术

DDS或DDFS是Direct Digital Frequency Synthesis的简称,DDS技术被视为第三代频率合成技术,它突破了PLL技术和直接模拟合成两种频率合成法的原理,从“相位”的概念出发进行频率合成,这种方法不仅可以产生不同频率的正弦波,而且可以控制波形的初始相位。甚至还可以用DDS方法产生任意波形(AWG)。DDS具有频率分辨率高、切换速度快、输出信号相位连续、可输出任意波形信号、能够实现全数字自动化控制等优点,使其已成为雷达、通信、工程设计等系统信号源的首选。DDS也具有一定的局限性,主要表现在输出频带范围有限和输出杂散度大。本文中DDS技术主要用来产生正弦波。

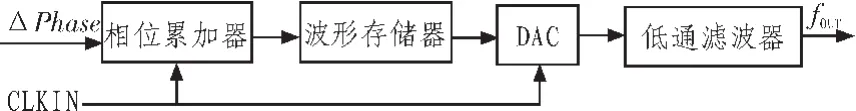

DDS技术的核心是相位累加器,它类似一个计数器。每来一个时钟信号,相位累加器的输出就增加一个步长的相位增加量,其大小由频率控制字来确定。信号波形的数据表包含待产生信号一个周期的幅度—相位信息。从数据表中读出相位累加器输出相位信号值对应的幅度数据,通过DAC将该数据转换成所需的模拟信号波形输出,低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号[2]。相位累加器的相位累加为循环迭加,这样使得输出信号的相位是连续的。相位累加器进行线性相位累加,当相位累加器加至全1时产生一次计数溢出,这个溢出率即为输出信号的频率。DDS可以产生任意频率任意形状的波形[3],如图1所示。

图1 DDS信号合成Fig.1 DDS signal synthesis

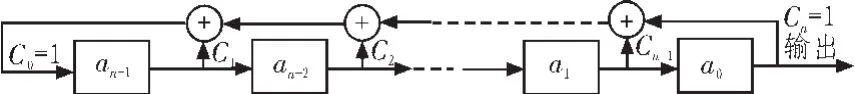

如果相位累加器的位数为N,频率控制字内的相位增量为△Phase,参考时钟频率为fCLKIN,则DDS系统输出信号的频率fOUT为:

输出信号的频率分辨率为:

本文使用DDS技术产生正弦波。

1.2 伪随机序列与m序列[4]

伪随机序列是一种可以预先确定并可以重复地产生和复制,又具有随机统计特性的二进制码序列。之所以称其为伪随机序列,是因为它表现出白噪声采样序列的统计特性,在不知其生成方法的侦听者看来像真的随机序列一样。

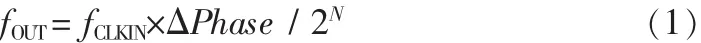

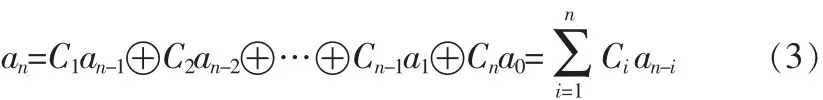

m序列是最长线性反馈移位寄存器序列的简称,是伪随机序列的一种情况。它是由带线性反馈的移位寄存器产生的周期最长的一种序列。m序列可以利用n级移位寄存器产生,可能产生的最长周期为2n-1。m序列发生器的结构主要分为两类,一类称为简单型码序列发生器(Simple Shift Register Generator,SSRG),另一类称为模块型码序列发生器(Modular Shift Register Generator,MSRG)。图2给出的属于SSRG结构,其中Cn,Cn-1,…,C0为反馈系数,也是特征多项式系数。这些系数的取值为“1”或“0”,“1”表示该反馈支路连通,“0”表示该反馈支路断开。反馈线的连接状态不同,就可能改变此移位寄存器输出序列的周期P。

图2 线性反馈移位寄存器Fig.2 Linear Freeback Shift Register

设n级移位寄存器的初始状态为:a1,a2,…,an,经过一次移位后,状态变为a0,a1,a2,…,an+1。经过n次移位后,状态为an-1,an-2,…,a1,a0,再移位一次时,移位寄存器左端得到新的输入an,如图2所示,可以写为:

本文使用m序列产生所需的伪随机二进制信号。

2 硬件设计

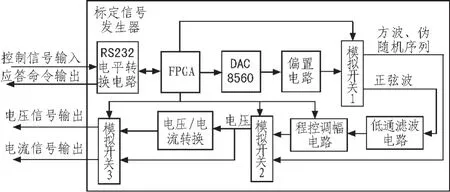

硬件设计的系统框图如图3所示。

图3 系统框图Fig.3 Block diagram of system

采用Altera的EP2C8T144C8 FPGA为控制核心,通过RS232串行通信总线与地震电磁信息采集系统主控制器通信,接收其控制命令。使用FPGA和16位串行DAC芯片DAC8560产生地震计标定所需的正弦波、方波、伪随机序列等信号。DAC产生的电压信号通过模拟开关1分两路输出,一路为正弦信号,经过二阶巴特沃兹滤波器滤波,再经过由数字电位计组成的可由FPGA程控的调幅电路;另一路为方波和伪随机序列,两路信号经过模拟开关2,该模拟开关的输出经过电压电流转换电路成为电流信号。电压电流信号经过模拟开关3输出。FPGA控制系统中的模拟开关的选通和关闭可以确定最终输出的信号类型。

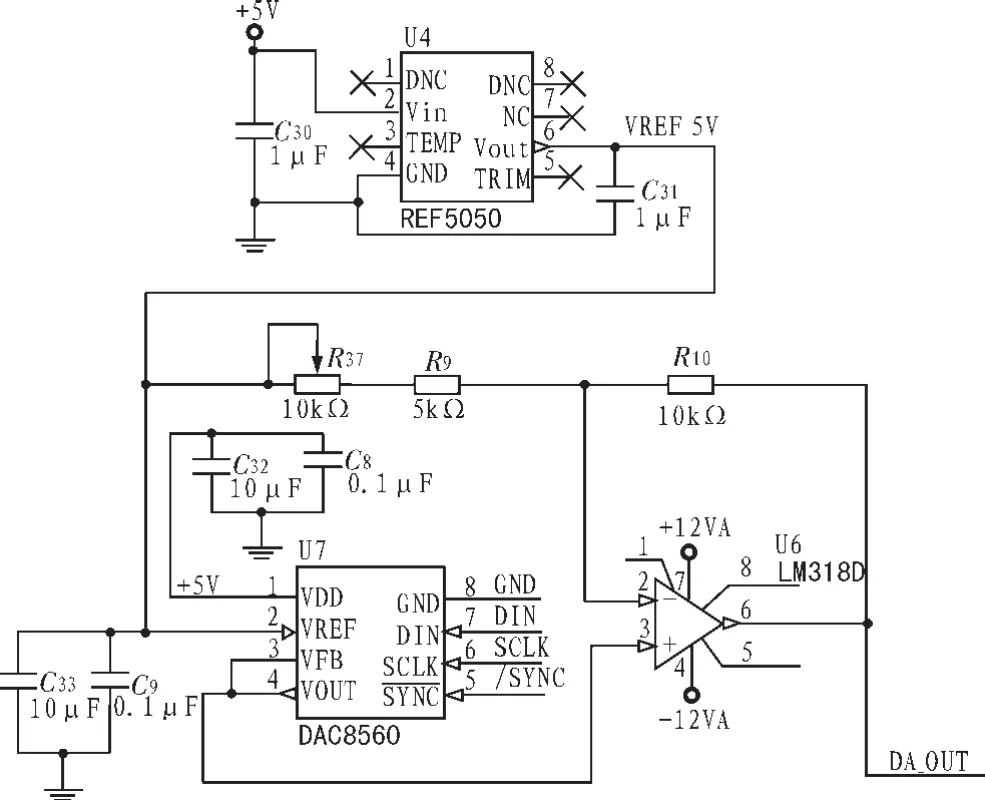

2.1 DAC及偏置电路设计

FPGA通过SPI串行通信接口控制DAC8560。使用外部5 V参考电压,DAC8560输出电压范围为0~5 V,要得到-5~+5 V电压输出,需要加偏置电路。图4为DAC及偏置电路。由电路图,可得:

其中Vo为输出电压,D为输入至DAC8560的数字量。

图4 DA及偏置电路Fig.4 DA and bias circuit

2.2 滤波器设计

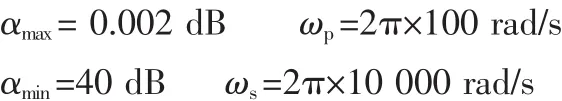

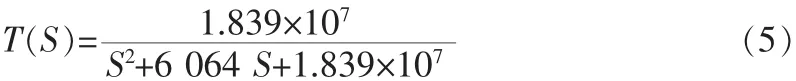

本文使用巴特沃兹滤波器[5]对DAC输出的正弦波滤波。分析系统,按如下技术指标设计滤波器:

其中αmax为通带最大衰减,ωp为通带边界频率,αmin为阻带最小,ωs衰减阻带边界频率。理论滤波器传递函数为:

实际电路由于阻容元器件参数限制,传递函数为:

2.3 调幅电路设计

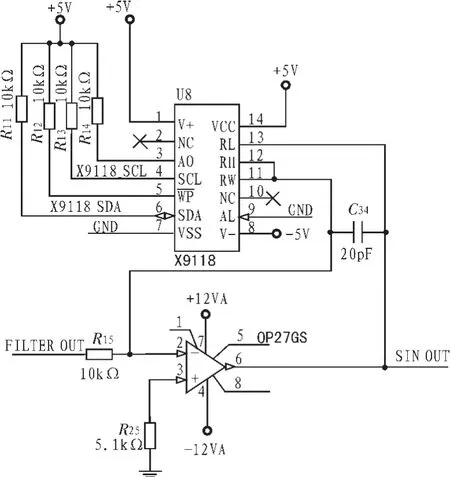

调幅电路基于数字电位计X9118,FPGA通过类似I2C的2线串行总线接口控制X9118。改变X9118的电阻,可改变放大电路的增益,从而达到电压调幅的目的。电路如图5所示。可以推导得出

其中Vo为调幅电路输出电压,Vi为调幅电路输入电压,D为数字电位计输入的数字量。改变输入的D值,就可以程控输出电压幅度。

图5 调幅电路Fig.5 Amplitude modulation circuit

2.4 电压电流转换电路

如图6,可以推导得出,只要R1/R2=R3/R4,可得

其中IL为负载端的电流,V为输入电压。实际电路中为确保满足R1/R2=R3/R4,加入一个可调电阻。

图6 电压/电流转换电路原理图和实际电路图Fig.6 Schematic and real circuit for V/I transform

3 软件设计

本文使用Verilog语言编写系统软件,开发时遵循自顶向下的原则,将系统层次化和模块化。按照响应速度,将系统软件分为3个层次:控制层、解析层、执行层。各层包含了实现各自功能的模块。图7所示为系统的软件系统框图。按照信号的流向,前端模块的输出驱动后端模块更新其状态机[6]的状态。

3.1 执行层

3.1.1 通 讯模块

图7 软件系统框图Fig.7 Block diagram of software system

串口接收模块将异步串行总线电平信号转化成字节流,每收到一个字节会产生一个data_ready脉冲信号,驱使解析器更新信息。

串口发送模块将解析器产生的字节流转化成异步串行电平信号。

3.1.2 芯 片控制器

芯片控制器包括DAC8560控制器、X9118控制器、模拟开关控制器等。其功能是将波形发生器产生的数字信号从串行总线发送到各个芯片,或根据波形要求选通或关断模拟开关。

3.2 解析层

3.2.1 命 令解析器

命令解析器将通讯模块发出的字节流按照既定的协议解析为各种命令,使控制层知道需要产生何种信号及其参数。

打包应答数据子模块将控制器应答信号按照既定的协议打包成字节流,交给通信模块发出。

3.2.2 波 形发生器

正弦波发生器实现了DDS算法,产生频率幅值可调的正弦波。

方波发生器产生幅度、宽度可调的方波。伪随机序列发生器产生m序列。

3.3 控制层

控制器模块根据解析层提供的命令控制波形发生器产生相应波形,并根据协议产生相应的应答数据。

4 结束语

将地震标定信号发生器应用于实验室与江苏省地震局联合开发的DUF-24IP型地震电磁信息采集系统,可以通过主控器发送命令,产生标定所需信号,完成地震计标定工作。

[1]刘庆伟.FBS-3A型反馈式宽频带地震计电流标定方法研究[J].地震报,2001,23(2):192-202.

LIU Qing-wei. Study on the calibration of feedback boardband seismometer FBS-3A with current signal[J].Acta Seismologica Sinica,2001,23(2):192-202.

[2]万其力,吴文彪.基于DDS及单片机的函数产生器设计[J].西安邮电学院学报,2003,8(3):35-38.

WAN Qi-li,WU Wen-biao.Function generator based on DDS and MCU[J].Journal of Xi’an University of Post and Telecommunications,2003,8(3):35-38.

[3]Varnes R S,Ball J A R,Hancock N H.A dual-output,coherent signal generator using direct digital synthesis[J].Instrumentation and Measurement Technology Conference Otlawa,1997(5):19-21.

[4]王会华,李保平.m序列发生器的设计与实现[J].北京电子科技学院报,2007,15(2):58-61

WANG Hui-hua,LI Bao-ping.Design and realize of m sequence generator[J].Journal of Beijing Electronic Science and Technology Institute,2007,15(2):58-61.

[5]刘京南.电子电路基础[M].北京:电子工业出版社,2003.

[6]刘小平,何云斌,董怀国.基于Verilog HDL的有限状态机设计与描述[J].计算机工程与设计,2008,29(4):958-960.

LIU Xiao-ping,HE Yun-bin,DONG Huai-guo.Design and description of finite state machine based on verilog HDL[J].Computer Engineering and Design,2008,29(4):958-960.