一种基于FPGA的媒体网关设计与实现

2011-03-06陈东

陈 东

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

网关是为了满足不同网络之间通信的设备,由于不同网络使用不同的协议,为了让两个使用不同协议的网络能够正常通信,就需要进行协议转换。目前,随着因特网的蓬勃发展,电信业正处于从现有网络向下一代网络(NGN) 演变的巨大变革之中,NGN 泛指以 IP 为中心,可以支持语音、数据和多媒体业务的融合或部分融合的全业务网络。NGN体系采用开放的网络架构,将传统交换机的功能模块分离成独立的网络构件,各个构件可按相应的功能划分,各个独立发展[1]。媒体网关是将一种网络中的媒体格式转换成另一种网络所要求的媒体格式的设备,媒体网关在NGN 中扮演着重要的角色,许多业务都需要媒体网关进行数据转换和接入实现。

1 媒体网关介绍

媒体网关位于软交换网络的媒体接入层,它将一种网络中的媒体转换成另一种网络所要求的媒体格式。根据媒体网关设备在网络中的位置,可以将其分为中继媒体网关、接入媒体网关、综合接入设备和综合接入网关[2]。IP中继媒体网关位于 IP 网络和 PSTN (个人电话交换网)网络之间,业务流通过电路交换机的中继电路进入或离开媒体网关,经其进行媒体格式转换后在IP 网中进行传送[3]。此媒体网关是中继媒体网关中的一种,为保证语音通话质量带内数据等传输质量,在业务由 PSTN交换网向 IP网中过渡中,不需要进行媒体编码转换,媒体网关的设计和实现就可完全基于FPGA进行,所以,其具有相当的设计灵活性与可移植性。

2 媒体网关的设计

2.1 系统设计

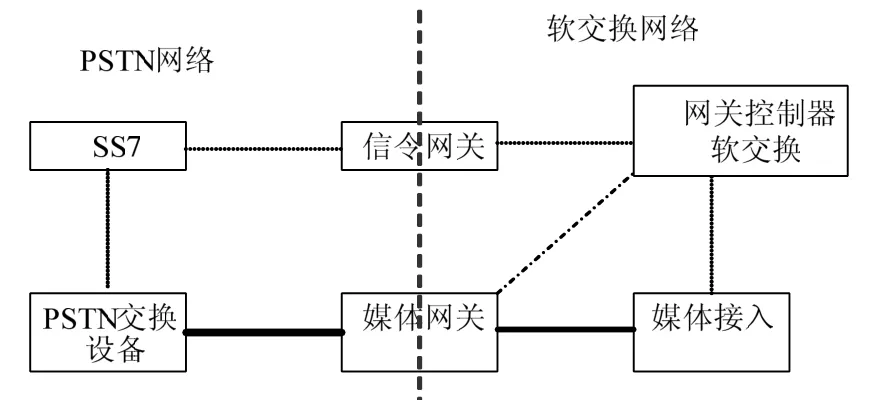

媒体网关附属于路由交换机,是路由交换机的接入与传输层,也是PSTN网落侧的媒体流与软交换网络侧IP数据包的双向终结点。其业务的互通流程需接受网关控制器的控制,才能完成每次语音和数据互通。其控制连接关系如图 1所示。

图1 系统架构和连接关系

2.2 网关硬件设计

(1)中继容量

为提高接入能力,节约宝贵的槽位资源,单个媒体网关卡设计为8个E1接口,共处理240路话音/ 传真/ 数据。单个机箱最多可以配置大约12 块网关卡。

(2) 板卡设计介绍

E1 网关板主要由多路E1 接口电路、千兆以太网接口电路、通信MIPS处理器和Xilinx公司FPGA Vietex-5系列中的155T组成。E1接口电路实现时钟恢复、数据提取、HDB3编解码、去抖动以及近远端环回功能;以太网接口电路实现千兆光接口与电接口自动检测,以及电接口的100 M/1 000 M自适应连接等,通过SGMII接口与FPGA互联,由FPGA提供千百兆MAC;处理器主要实现板卡管理、信令转换与处理和资源控制等功能;FPGA包含了上行数据处理部分、下行数据处理部分和与处理器接口部分,各部分的主要功能有:实现中继信令提取与发送、语音组包与解包、静音检测与回铃音的生成和发送、查表等。设计示意如图2所示。

图2 板卡设计示意

2.3 网关软件(含信令网关)设计

媒体网关软件接受媒体网关控制器的控制命令,按要求控制硬件完成事件生成;向媒体网关控制器报告相应的数据和资料。在局域网出口侧与局域网相连,发送或接收与媒体网关控制器之间的信令、协议和媒体控制消息;在媒体网关内部与硬件接口模块相连,完成对硬件的控制。

媒体网关软件分布于板卡的处理器中,采用分布式负荷分担的机制,提高整机的软件处理效率。从功能模块划分大致可分为:操作系统软件模块、底层驱动软件模块、IP 适配软件模块、网关管理软件模块、信令处理模块、信令传输控制软件模块和业务表项管理模块,如图3所示。

图3 媒体网关软件设计

操作系统软件模块:媒体网关的操作系统采用Vxworks实时操作系统,Vxworks是美国Windriver 公司的先占式实时操作系统,具有丰富的BSP支持,并提供配套的Tornado 开发平台,以其稳定性和高效性,占有商用实时嵌入式操作系统得主导地位[4]。

双拥办是该区对口解决退役军人问题的部门之一。这些年一起走过的风风雨雨,让这些退伍老兵已经把这里当成了“娘家”,一有空就前来扎堆,互诉衷肠,互相鼓励。他们对杏花岭区为他们千方百计排忧解难的做法非常认可,对王业发这样肯扑下身子实干、能不畏艰难敢于担当的干部很是钦佩。王业发得到了部队官兵、家属、复退转军人、军烈属和社会各界的广泛赞誉。

底层驱动软件模块:完成各硬件板卡处理器和各种功能芯片的初始化、管理和控制,并实现与上层软件的接口。

IP适配软件模块:实现TCP/ IP 协议和UDP/ IP 协议,完成信令消息和接入业务与IP 网之间的格式转换。

网关管理软件模块:负责对网关的维护管理,主要网关参数配置、状态监测、对路由和链路状态的管理、对各接口是否正常的检测和管理等。

信令处理模块(信令网关):从硬件线路上接收信令消息单元或向硬件线路发送信令消息单元,完成信令消息的适配处理,并对收到的信令消息进行预处理。

信令传输控制软件模块:完成PSTN 信令在IP 网可靠传输,使用确认方式进行无差错无重复传送用户数据,并根据通路的MTU(消息传输单元) 的限制进行用户数据的分段并在多个流上保证用户消息的顺序递交。

业务表项管理模块:完成FPAG从IP硬件线路上向E1接口码流,与E1接口码流向IP数据双向的数据表项的管理,并负责向FPGA下发与每一个呼叫相关的表项数据。

2.4 网关FPGA设计

媒体网关FPGA既是PSTN侧与板上处理器,以及板上处理器与媒体网关控制器的信令和消息收发与控制通道,又在处理器软件的管理和控制下完成媒体流向IP数据包、IP数据包向媒体流的双向数据格式转换,转换过程中完成双向数据流控制的表项查找;同时完成E1接口侧的7号信令链路层HDLC(高级数据链路控制)数据发送和接收,以及从以太网接口侧(含光口和电口)IP数据包中解析和分流出从媒体网关控制器来的信令与路由交换而来的语音数据包。

在整个设计过程中将其分成上行处理部分(从E1接口到处理器和路由交换整个过程)、下行处理部分(从处理器和路由交换到E1整个过程)和与处理器接口部分3个部分,前两个部分数据流向是完全相反的两个数据处理流程。按照设计的模块化和可移植性来说,虽然此媒体网关含有8个E1端口,这里的基本设计思维是先按照最小使用逻辑量设计出一个端口,然后再复制七份,从而完成整个8个端口的逻辑设计,与处理器接口部分主要完成与处理器信息交互的功能,现不在作过多说明,下面主要对前两个部分进行介绍。

媒体网关FPGA上行数据处理主要分为以下几个部分:接口数据时域转换处理、HDLC数据接收和处理、业务数据缓存、业务数据封装IP包、特殊数据解析。上行数据处理示意如图4所示。

接口数据时域转换模块:完成由输入时钟相对应的输入数据到与内部时钟时钟相匹配数据的转换模块,便于统一FPGA内部的处理时钟,使所有逻辑模块都相对集中在同一时钟下处理,有利于FPGA的布局和布线。

HDLC数据接收和处理模块:完成HDLC数据的帧定位、插入零的删除、HDLC数据的接收、CRC16检验、错误数据包的滤除等功能,然后将正确的HDLC数据发送到处理器进行解析。

业务数据缓存模块:业务数据存储器,设计中分成上下两个半区,当上半区数据满后,就开始将数据缓存于下半区,同时将上半区的数据按照一个时隙一个包的形式发出。同理,当下半区数据满后,就开始将数据缓存与上半区,同时将下半区的数据按照一个时隙一个包的形式发出。依次循环。

业务数据IP包封装:接收从业务数据缓存送来的每个时隙数据包,在处理器的控制下,将相应的数据包进行RTP/RTCP、UDP、IP封装,然后发送到路由交换。

特殊数据解析模块:对每个话路时隙中的特殊数据进行解析,然后将解析到的数据发送到处理器中进行处理。

2.4.2 下行数据处理介绍

下行数据处理器流程相对于上行来说更为复杂,在设计时除需要考虑将多种数据包向对应的端口和时隙发送,最主要的是还需要考虑业务数据的连续性,即业务数据在由IP数据包向码流转换时的连贯性。因此,就需要考虑到IP数据包在传输中可能发生的延迟、抖动、掉包、包续错乱等现象,这在以太网数据交换和传输中是很常见的现象,但是对于以码流形式传输的PSTN交换中,却是非常致命的问题,会造成语音质量的严重下降,或者根本就无法进行有效的通信。所以,在FPGA的设计中都必须将这些问题予以最大程度的消除和解决,以保证每次通信性能的稳定性和有较高通信质量。

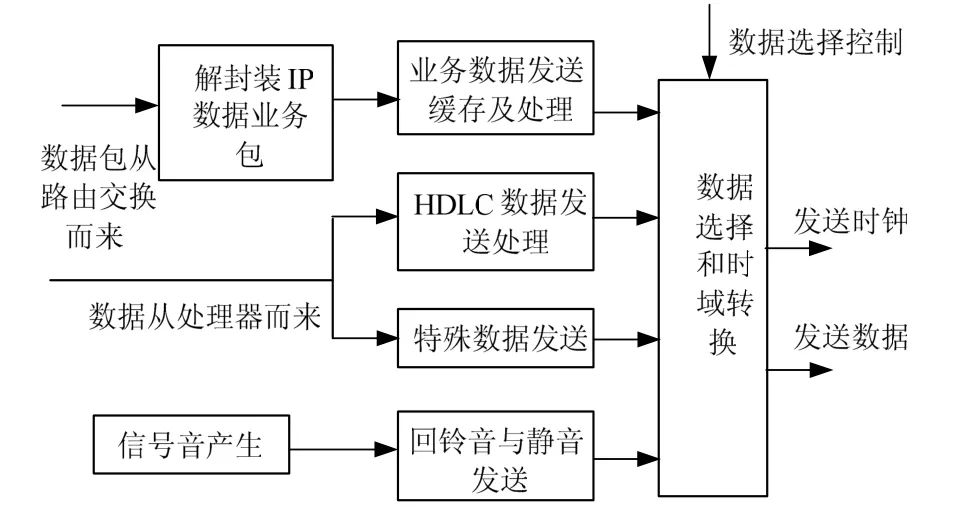

媒体网关FPGA下行数据处理主要分为以下几个部分:解封装IP数据业务包、业务数据包发送缓存及处理、HDLC发送数据处理、特殊数据发送、回铃音与静音发送,以及数据选择和时域转换等功能模块,下行数据处理示意如图5所示。

图5 下行数据处理示意

解封装IP数据业务包模块:对路由交换而来的IP数据包业务包进行解析,然后将各个业务数据包发送到对应的端口、时隙业务数据发送缓存的相应缓存中。

业务数据发送缓存模块:要抗线路传输抖动、延时、掉包、包续错乱问题,此模块的设计至关重要。将每个时隙的缓存分成四个分支缓存,分别存储RTP/RTCP包序号中的后两比特分别为00、01、10、11的数据包,如此,即使包续好发生了错乱,也有较强的纠正能力。同时在向E1接口发送数据的处理上,将收到的第一个业务包,先不及时发送,等计数到一个数据包组包时间或者或下一个数据到来的两个条件其中一个满足才开始发送数据,这样就有较好的抗延时和抖动的能力,如:完成一个IP包160个字节的组包时间需要20 ms,收到第一个IP包后,等20 ms才开始发送数据,发送第一个数据包的时间又需要20 ms,只要在这40 ms的时间内第二个数据到来,都可以正常发送,而不会造成掉包。如果想要取得更大的抗抖动和延时效果,可以将每个时隙的分支缓存成倍增加,然后多等待几个包到来才开始发送第一个包,但是,等待时间越长话音延迟也会越大。此设计也是业务Qos保障的手段之一

HDLC数据发送处理模块:完成HDLC数据帧头的发送,HDLC数据的发送中每五个“1”后零的插入,HDLC数据CRC-16的计算和CRC的发送等。

信号音产生、回铃音与静音发送模块:信号音产生模块产生450 Hz的单音信号发送出去,回铃音与静音发送模块将各个时隙所需信号音根据控制模块的要求发送到相应的各端口时隙上。

特殊数据发送模块:将从处理器而来的特殊数据发送到相应的端口时隙中。

数据选择和时域转换模块:将以上各种数据,根据数据选择控制信号,发送相应的数据到E1接口线路上,同时完成数据从内部数据处理时钟到线路发送时钟的转换。

3 结语

这里简要分析了媒体网关的体系结构和发展现状,详细介绍了一种媒体网关的硬件、软件,特别是FPGA部分的设计方案和实现,其设计对于通用媒体网关也具有一定的借鉴意义。且所描述的媒体网关的模型是笔者结合实际开发的经验设计的,该设计已经运用到实际,经过测试与实践,性能良好,满足网络媒体网关的各项功能指标和要求。

[1] 赵慧玲,叶华.以软交换为核心技术的下一代网络[M].北京:人民邮电出版社,2003.

[2] 黄蓉,晏宪华,王波.基于软交换的中继媒体网关设计与实现[J].广东通信技术,2005(02):6-9.

[3] 张杰斌,黄本雄,胡广.软交换网络中中继媒体网关的研究与设计[J].通信技术, 2003(04):22-24.

[4] 陈凤祥,刘学军.IP媒体网关的设计[J].无线电工程,2008(08):7-10.