多核实验平台的片上总线设计

2011-02-10饶云华李德识隋竹翠武汉大学电子信息学院湖北武汉430079

饶云华,李德识,田 茂,隋竹翠 (武汉大学电子信息学院,湖北武汉430079)

多核实验平台是 《EDA实验》课程的基础平台之一,不仅需要采用先进的实验系统架构,而且其实验内容也必须随着技术的发展及时更新,这样才能使学生理解和掌握最新的设计方法和技术。

在多核实验中,设计采用基于IP的可重用设计方法,整个CPU性能与IP之间互连方式密切相关。因此,IP互连就成为构造多核CPU的关键,也是多核CPU设计实验的重要内容之一。使用片上总线标准协议是实现多核CPU中IP互连最常用的技术手段,也适合作为多核实验中CPU的互连方式。

笔者在探讨主流片上总线特点的基础上,根据EDA实验课程教学特点,并结合多核实验平台性能等实际情况,提出了以现有多核EDA实验平台为基础的AXI片上总线互连方案,从而满足实验教学需要。

1 主流片上总线介绍

1.1 OCP协议

OCP协议[1]是为了在SoC设计中实现IP核的即插即用而制订的开放式内核协议。OCP协议与总线独立,以IP核为中心,能满足IP核通信机制的所有要求。OCP协议支持从简单的请求-响应到流水线以及多线程对象的高性能数据传输模型。OCP协议信号具有同步和单向的特征,简化了核的实现、综合和时序分析,适用于多种形式的片上通信。OCP协议包括点对点的同步接口、与总线独立、地址周期和数据周期分开、支持流水线操作、突发传输方式及乱序传输等特性。

1.2 CoreConnect协议

CoreConnect协议[2]由IBM开发,主要包括处理器本地总线 (PLB)、片上外设总线OPB(On-chip Peripheral Bus)、总线桥接器、2个仲裁器及设备控制寄存器DCR(Device Control Register Bus)。根据访问速度,CoreConnect总线可分为3层,其中,PLB与处理器及DMA等高速外设连接,采用数据总线读写分离的方法,数据位宽最高为256位,工作频率可达180MHz;OPB连接UART、GPIO等低速设备,数据/地址位宽都为32bit,OPB通过桥接器接到PLB;DCR采用菊花链方式将处理器与设备配置寄存器连接起来,具有与PLB不同的地址空间。CoreConnect总线结构为多核互连设计带来极大的灵活性,可根据不同的应用选择不同的总线架构和模块互联。

1.3 AMBA协议

AMBA协议[3]是ARM公司开发的用于连接和管理片上系统中功能模块的开放标准和片上互连规范,主要包括AXI、AHB、APB和ATB等部分。其中,AMBA3 AXI接口规范可支持高数据吞吐量。利用相对计时灵活的5个单向通道和乱序数据传输,可以进行管道化互连、频率之间的切换实现功耗管理、同时执行读写操作来有效支持低速外设。AMBA3 AHB接口规范可在对AMBA3 AXI性能没有要求的情况下,在单频率子系统中实现简单外设之间的高效互连。AMBA3 APB接口规范支持访问外设中的配置寄存器和通过低带宽外设的数据通信所需的低带宽业务。AMBA3 ATB接口规范增加了数据不可知的接口,可在跟踪系统中根据AMBA规范跟踪数据、组件和总线,其与外设保持平行,互相连接,同时保持可见性。

2 基于AXI总线的互连设计

多核EDA实验平台本身并不固定采用CPU核,由学生自行选择设计,但为了保证接口兼容性,在多核处理器互联方面,结合教学实际,内部连接采用适合片上系统通信、具有高可配置性的AXI3协议。使用该协议可有效解决IP核可移植性、设计复用的问题。

2.1 AXI协议特点

AXI总线是一种多通道传输总线,以不同通道进行地址、读数据、写数据、控制等信号传输,支持乱序数据发送,主设备在得到返回数据前可发出多个读写操作。通过使用字节选通功能支持非对齐数据访问。支持只发送起始地址的突发传输。除支持数据传输外,AXI总线还包括可选的扩展信令协议以支持低功耗操作。

2.2 AXI协议读写时序

AXI协议以突发传输为基础,有5个独立的传输通道,其中地址和控制信息分别在读和写地址通道上传输,数据分别在写数据和读数据通道上传输。另外,还有附加的写响应通道以允许从设备通知主设备写操作完成。所有通道使用双向的VALID和READY握手结构。

突发读传输如图1所示。主设备输出地址,同时输出突发传输长度和方式的控制信号,从设备在一个周期后接收。当地址在地址总线上后,数据开始在读数据通道进行传输。从设备将VALID置低,直到出现读数据。在突发传输的最后,从设备将RLAST置位以表明正在传输最后一个数据。

图1 突发读传输

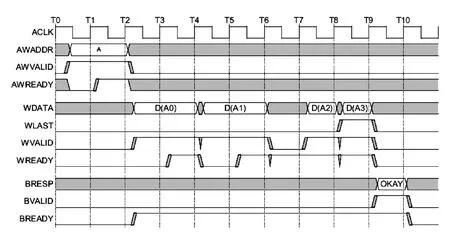

突发写传输如图2所示。当主设备在写地址通道上发送地址与控制信息时,则表明开始写传输。然后,主设备在写数据通道上发送所写的每个数据。当主设备发送最后1个数据,WLAST信号变高。当从设备接收到所有数据后,向主设备返回写响应信号,表明写传输完成。AXI协议通过接口为每个传输分配一个ID来支持乱序数据传输。同时,要求同一ID需按序传输,不同ID可乱序传输。

2.3 AXI总线验证

对于多核CPU芯片来说,设计逻辑复杂度的提高将使验证时间在整个开发周期中占很大比重,对整个设计的成功具有决定性影响。ARM公司的AMBA设计工具包 (ADK)提供了AHB和APB设计和验证组件,包括AHB总线矩阵和文件读取器总线主接口,可方便快捷地进行基于AHB/APB的系统设计。为此,Synopsys公司针对AMBA3 AXI开发了能完善地解决基于AXI多核系统验证问题的DesignWare IP解决方案[4],该方案包括3个部分:DesignWare综合IP、验证IP及带有coreAssem-bler工具的DesignWare IP,可快速生成、仿真和综合基于AMBA的子系统,实现整个设计过程的自动化。

图2 突发写传输

2.4 AXI互连架构

AXI协议提供了主设备与互连结构、从设备与互连结构以及主从设备之间的单一接口定义。在基于AXI互连架构中,一个实体作为主设备,另一个实体作为从设备。只有主设备才能发出控制命令,控制传输。从设备响应主设备的控制命令,并接收来自主设备的数据或者向主设备传送数据。典型的AXI互连结构如图3所示,该互连架构利用AXI协议,实现了IP核可移植性,具有设计可复用的优点。

图3 基于AXI协议的片上互连架构

3 结 语

多核EDA实验平台以多核架构设计为主线,为学生提供多核设计实验,有助于提高学生分析问题和解决问题的能力。笔者讨论了AMBA 3AXI协议及其设计,包括基于AXI的片上系统架构设计和系统级验证。基于AXI协议的互连架构能促进IP核的复用,缩短设计时间并且提高系统性能,通过该实验可使学生加深认识并掌握多核互连设计的方法。

[1]饶云华,鄢媛媛,朱小虎,等.面向SoC的开放式IP核接口协议 (OCP)研究 [J].中国集成电路,2007,16(2):39-43.

[2]王炜,汤志忠,乔林.片上多处理器互连技术综述 [J].计算机科学,2008,35(5):7-30.

[3]肖福明.高密度计算与多核系统设计技术研究[D].合肥:合肥工业大学,2010.

[4]孟昕.SoC设计优化的域特定语言方法和建模 [D].杭州:浙江大学,2010.