一种集成稳压电路的设计与研究

2011-02-09兰燕娜薛同莲罗向东

兰燕娜,薛同莲,罗向东

(1. 南通大学 理学院,南通 22600;2. 南通大学 省专用集成电路设计重点实验室, 南通 226001)

0 引言

稳定的基准电压源是模拟集成电路和混合集成电路的重要模块,广泛应用于诸如高精度比较器、模/数转换器、数/模转换器、偏置电路等集成电路设计中[1,2]。带隙基准电压源具有良好的输出精度和稳定的温度特性,已经成为目前使用最为普遍的电压基准源[3]。本文设计了一种带隙基准电压源,采用CSMC0.6um CMOS 2P2M标准工艺,具有电源抑制比高和温漂低等特点,能够较好满足芯片的整体要求,具有一定的实用性。

1 理论分析

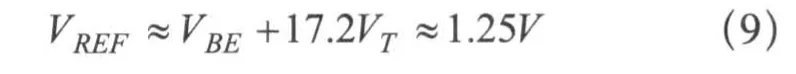

带隙基准的工作原理是根据硅材料的带隙电压的温度无关的特性,利用 VBE的正温度系数与双极型晶体管VBE的负温度系数相互抵消,实现低温漂、高精度的基准电压,即VREF=1VBE+2VBE。选择适当的参数,使两个电压的温度漂移相互抵消,从而可以得到在某一个温度下为零温度系数的电压基准[4,5]。

下面详细推导这个原理[6]。

对于一个双极器件,有Ic=ISexp (VBE/VT),变换之后,写出VBE=VTln (IC/Is)。在VBE对T取导数时,IC也是温度的函数。为了简化分析,暂时假设IC保持不变。这样,

又因为饱和电流Is正比于,其中 为少数载流子的迁移率,硅的本征载流子浓度。这些参数与温度的关系可以表示为 ∝0Tm,其中,m≈-3/2,并且 [-Eg/(kT)],其中Eg≈1.12eV,为硅的带隙能量。所以

式(6)给出了在给定温度T下基极-发射极电压的温度系数,从中可以看出,它与VBE本身的大小有关。当VBE=750mV,T =300K时,VBE/T ≈-1.5mV/K。另外由式(6),我们还注意到,VBE的温度系数本身与温度有关。

如果两个双极晶体管工作在不相等的电流密度下,那么它们的基极-发射极电压的差值就与绝对温度成正比。如果两个同样的晶体管(如IS1=IS2)偏置的集电极电流分别为nI0和I0并忽略它们的基极电流,那么

这个温度系数与温度或集电极电流的特性无关。利用上面得到的正、负温度系数的电压,我们可以设计出一个令人满意的零温度系数的电压基准。我们有VREF=1VBE+2(VTln n),这里VTln n是工作在不同电流密度下的双极晶体管的基极-发射极电压的差值。恰当的选择1和2的值,就可以得到不同的基准。因为在室温下 VBE/T ≈-1.5mV/K,而VBE/T ≈+0.087mV/K,所以可以令1=1,选择(2ln n) (0.087mV/K)=1.5mV/K,也就是,2ln n≈17.2,表明零温度系数的基准为

3 电路结构和工作原理

3.1 电路组成

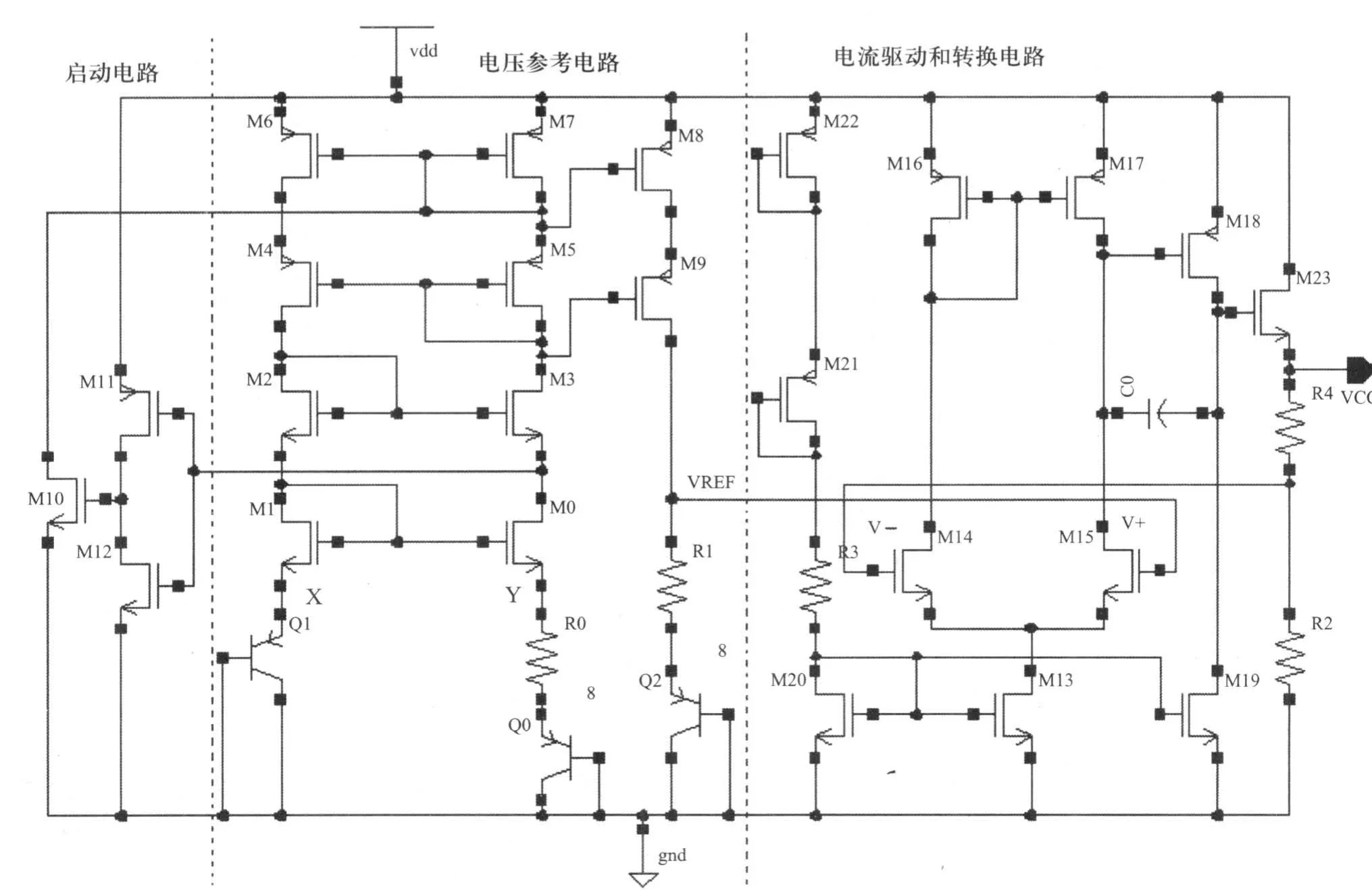

图1为电路原理图。本电路分为3部分:启动电路(start-up circuit)、电压参考电路(voltage reference circuit)和电流驱动和转换电路(current driving and converting circuit)。该电路可以实现VBE和 17.2VT相加。

3.2 工作原理

3.2.1 电压参考电路

电压参考电路由PTAT电流产生部分和VREF输出组成,特点是采用了共源共栅电流镜结构[7]。 在 图 1中, 由 M5、M7、M8、M9组 成 共 源共栅结构的电流镜,使得通过Q0、Q1、Q2 三个晶体管的电流都相等,M0、M1、M2、M3组成电压箝位电路,保证X、Y二点的电压近似相等,Q0、Q1和R0组成PTAT电路,由于VX=VY,VX=VBE1, VY=VR0+VBE0,所以得到 VBE1=VR0+VBE0,VBE=VBE1-VBE0=VR0,联系上文所述,可知 VBE是一个正温度系数的电压,进而产生流过R0、R1的PTAT电流,VREF的值由下式决定

图1 电路原理图

3.2.2 启动电路

在与电源无关的偏置电路中有一个很重要的问题是“简并”偏置点的存在,即电路存在两个平衡工作点,一个是电源上电后所有的晶体管均传输零电流,并且可以无限期地保持关断,另一个是正常工作点。由于电路可以稳定在两种工作状态中的任一种,所以需要通过增加启动电路,在电源上电时驱使电路摆脱简并工作点[8]。

在本设计中,启动电路由3个MOS管构成。如图1中左半部分所示,M11、M12构成反相器,M13构成共源放大器。反相器的输入端接在M3的源极,输出端接在M13的栅极,而M13的漏极接在M7的漏极。电路上电时,基准产生电路的所有晶体管传输零电流,M13关断,M3的源极为低电平,因此,经过反相器,M13的栅级输入高电平,将M13导通,从而M13的漏端,即M7的漏端电压被提高,M7也导通,进而使整个电路都导通。之后,由于反相器输入端电压上升到高电平,输出端降为低电平,从而关断M3,完成整个电路的启动过程,使电路进入正常工作状态。

3.2.3 电流驱动和转换电路

在电压基准产生电路中,利用电流镜把流过R0的电流I1镜像到R1支路,使得这两路电流完全相等,因此,在基准输出端VREF不能向负载提供电流驱动,这样电路就只能提供电压驱动能力,这在许多应用中是不够的,为了改变这种状况,本文设计了将电压转换成电流的转换电路。

从图1中可以看到,M13~M22及R3构成一个NMOS输入端的二级运算放大器结构。第一级放大:M14和M15两个NMOS作为驱动管,M16和M17组成一个有源电流镜作为M14和

M15的负载,M13、M19、M20构成电流镜,而M20~M22以及R3一起决定了电路的偏置电流,其电流值为

I3取20uA,则M22的宽长比为3.5/1.2,M21:3.5/1.2,M20:8.4/1.8,R3的阻值取10K。

第二级放大:M18和M19构成共源放大器,M18作为驱动管,M19作为M18的有源负载,同时还起到镜像电流的作用。它将第一级差分放大器的单端输出信号进一步放大,以得到较高的电压增益。如图1右边部分所示,运算放大器的同向输入端V+连接到基准输出端 ,反向输出端V-接到电路的最终输出,运算放大器输出接在一个共漏电路的输入端,形成单位增益缓冲器,改变了电路的负载特性,降低了输出阻抗,使得电路更接近于一个理想的电压源。由M23、R4、R2构成的共漏电路提供了负载所需要的驱动电流。加了电流驱动和转换电路之后,基准电压的温度特性和电源抑制比都得到了改善,并且得到了后续电路所需的电压信号[9]。

4 仿真结果及其分析

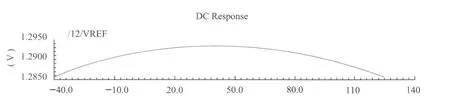

仿真结果如图2、图3所示,由此可得此稳压电路的性能特点及技术指标。

4.1 温漂小

VREF的温度特性如图3所示。

图2 温度特性曲线

实际仿真中,取R1为30.63KΩ,R0为2.7KΩ。电压VREF在-40℃ 125℃温度范围内的温度系数为37.3533ppm/℃。在27℃时,电压输出为1.29341V。

4.2 电源抑制比高

图3是带隙基准电压电路的电源抑制比输出,由图中可以看出,其直流电源抑制比的值为43.98dB。

图3 电源抑制比特性曲线

5 结束语

本文根据带隙基准原理,实现了一个高精度带隙基准电压电路,它具有很好的温度稳定性和电压精度,得到了后续电路所需的电压信号。在版图设计时采用0.6umCMOS工艺。SPECTRE仿真结果表明,本设计达到较好的技术指标。

[1] 幸新鹏,李东梅,王志华.CMOS带隙基准源研究现状[J].微电子学,2008, 3( 1): 57-63.

[2] E Hegazi, Abidi A A. Varactor Characteristics, Oscillator Tuning Curves and AM-FM Conversion [J]. IEEE JSSC,2003, 38(6): 1033-1039.

[3] 吴志明,黄颖,吕坚等.高电源抑制比的CMOS带隙基准电压源[J].电子科技大学学报,2008,37(3):453-456.

[4] M A Margarit, J L Tham, R G Meyer, M J Deen.A lownoise, low-power VCO with automatic amplitude control for wireless applications [J].IEEE JSSC, 1999, 34(6): 761-771.

[5] A Hajimiri, T H Lee. A General Theory of Phase Noise in Electrical Oscillators [J]. IEEE JSSC, 1998, 33(2): 179-194

[6] Behard Razavi.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2004.

[7] 刘宗福,马冬冬,赵丹辉.一种高精度低电源电压带隙基准源的设计[J].电子科技,2010,23(11):41-43.

[8] 刘军儒, 牛萍娟, 高铁成. 一种高电源抑制比带隙基准电压源的设计[J]. 天津工业大学学报. 2010, 27 (2): 60-62.

[9] 邓云飞,吴广玉.一种芯片内部稳压电源的实现[J].电子器件, 2004, 27(2):94-97.