基于VMM方法的SOC集成验证

2011-01-26罗胜钦

李 磊,罗胜钦

(同济大学电子科学与技术系,上海 201804)

1 引言

随着集成电路设计向超大规模发展,芯片验证工作的难度在不断增大,验证的工作量已经占到整个SOC研发的70%左右,芯片验证直接影响到芯片上市的时间,因此提高芯片验证的效率已变得至关重要[1]。

VMM是synopsys公司推出的基于system verilog的一套验证方法学,继承于RVM。利用VMM的层次化、随机约束等特点,能有效提升现有的验证方法,快速搭建具有目标模块的验证环境[2]。

2 SOC集成验证

SOC验证可以分为集成验证IV(Integrated Verification)和系统验证SV(System Verification)。本文主要介绍SOC集成验证,采用VMM验证方法学和DesignWare VIP,Master例化为VIP Interface模型,通过约束VIP Transaction参数产生各种定向激励;通过约束Scenario Class产生各种随机激励。

2.1 集成验证的功能

集成验证需要完成的任务包括:

(1)验证各功能模块是否正常连接;

(2)验证各模块对片外IO是否连接正常;

(3)验证各模块间的互联是否正常,例如DMA请求信号和VIC请求信号;

(4)验证各层总线的地址映射是否正常;

(5)Memory地址遍历和随机测试;

(6)多Master冲突检测等。

集成验证是基于时钟周期的测试,能够基于时序非常方便地发送各种不同的操作,可以弥补系统验证的不足;同时由于不需要启动系统,集成验证具有运行速度快的特点。集成验证在芯片验证中极其重要。

2.2 集成验证平台

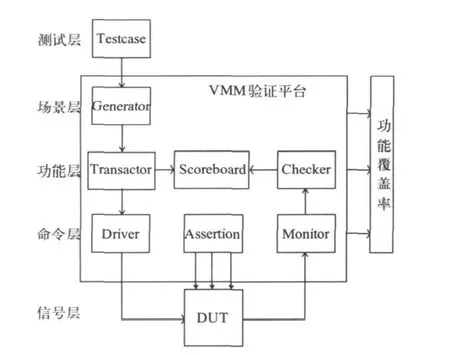

在SOC集成验证中需要将每个Master替换为VIP Interface模型,通过例化的模型访问所有的IP寄存器和Memory地址空间,验证架构互连的正确性。项目的集成验证平台采用VMM方法。图1显示了VMM层次化验证平台的结构[3]。

图1 VMM层次化验证平台结构图

VMM验证平台有多个层组成,主要包括图1中的测试层、场景层、功能层、命令层和信号层,反映了设计所处理数据的抽象层次。验证平台能满足不同测试用例的各种要求,测试用例的编写位于该验证平台的顶层,每个层次都能给上层提供一系列的服务,并通过抽象将低层次的细节隐藏起来[4]。

3 集成验证环境

3.1 可归一化的集成验证环境

集成验证是否高效,跟集成验证环境的优劣密切相关。其中,集成验证环境的归一化对集成验证工作具有重要意义。

集成验证环境的搭建是需要花费很多人力时间才能完成的。在追求芯片快速上市的今天,一个项目搭建一个全新的验证环境已经无法让人接受[5]。集成验证环境的归一化主要体现在一些公有目录和文件的存放具有统一性,可被其他项目重用,从而避免一个项目一个验证环境的情况,对于新的项目只需修改一小部分文件即可。

本项目采用可归一化的验证环境,在验证环境搭建中减少了很多工作量。

可归一化SOC验证环境文件的存放如下:

|—Verification // 验证的总目录

|—common // 系统验证和集成验证公共目录

|—bin // 公共脚本

|—testbench //存放公共的测试文件

|—vfilelists //存放所有的RTL代码

|—pmap //存放IP的pmap文件

|—mem-model //存放存储器模型

……

|—iv // 集成验证目录

|—env //验证环境文件的存放

|—sim //仿真开始目录

|—log //仿真log文件夹|—wave //仿真波形文件夹

|—output //编译仿真过程文件

……

|—tc //验证用例目录

|—reg //寄存器测试用例目录

|—mem //Memory测试用例目录

……

|—script //脚本文件目录

|—vmt_bfm //Vmtmaster的bfm目录

……

其中,env文件下存放着VMM验证代码模板。Ahb_env.sv主要用于把各个Master、slave和他们各自的数据通道连接起来,起到贯穿所有组件的作用。Ahb_gen.sv用于产生各种激励,通过约束Vip transaction参数来定义上层激励函数。Ahb_defines.sv包含系统使用的宏定义。

对于架构、功能等不同的片上系统,SOC验证环境的修改不可避免,但是有了可归一化的SOC验证环境,其继承性就大大加强。根据归一化验证平台,就可快速搭建一个新项目的SOC验证环境。

3.2 基于VMM和DW VIP的集成验证环境

AMBA总线是ARM公司推出的SOC总线,应用广泛。本项目也是基于AMBA总线架构,采用ARM9处理器,SOC的集成验证环境是基于VMM和DesignWare VIP。

V M M提供了用于实现验证环境的基本类vmm_env,任何验证环境都从该类继承,该类控制着整个仿真的进程,用于控制其他类的实例化,进程启动和结束[6]。

Vmm_env提供的基本函数和方法使得环境的搭建到仿真的完成只需9步操作。这9步操作均在ahb_env.sv中定义和配置,分别是:env.gen_cfg,env.build,env.reset_dut,env.cfg_dut,env.start,env.wait_for_end,env.stop,env.cleanup,env.report。

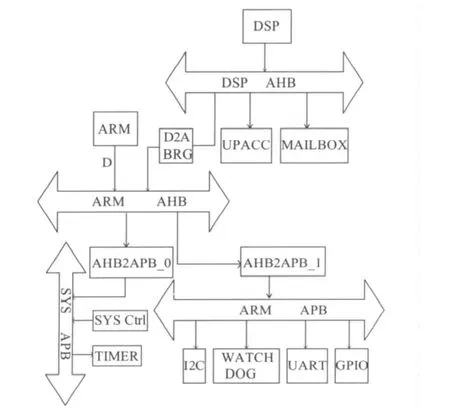

在这9步操作中,我们可以根据具体验证的要求和任务,在 env.build、env.start、env.wait_for_end、env.stop这几个步骤中进行设定。图2是SOC系统芯片结构简图。

图2 SOC系统芯片结构简图

在SOC集成验证中我们将每个Master替换为AHB VIP Interface模型,通过例化的模型访问所有的IP寄存器和Memory地址空间[7]。

测试层testcase主要是验证用例的编写。而VMM_SCENARIO_GEN类由宏生成,根据指定的VMM_DATA类来生成场景发生器。

本文的测试用例构造最常用的方式是:`ARMD.write_32(`asicSYSCTRL,32’h00000010)。此语句是Master ARMD访问系统控制器SYS CTRL的一个寄存器。其中,`ARMD是一个宏定义,为场景层的generator发生器的一个通道。在write_32函数中,运用了VMM_channel类out_chan.put(item),主要作用是generator将数据包放入通向transactor的channel中。

AHB VIP模型在VMM验证中起着重要的作用,在VMM中实现的是功能层和命令层的功能。这里采用的是DW_Vip_ahb_master_rvm类,此类具有事务处理器(transacor)的功能。构造函数为:

Function new(

string Instname,

AhbmasterPort portconnect,

dw_vip_ahb_master_configration cfg,

dw_vip_ahb_transaction_channel in_chan,

dw_vip_ahb_transaction_channel out_chan,

)

从in_chan输入的transaction,经过transactor解析后,转换成AHB Masterport的信号。通过AHB Masterport interface和DUT交互,从而完成了从测试层到DUT接口的激励传输。

从测试层到达信号层的过程很好地体现了VMM验证方法的核心。

VMM验证与传统的功能验证区别在于:传统的功能验证是在DUT的接口上直接输入激励,通过DUT检查响应。这种方法抽象级别低,在复杂的SOC中不容易定位错误,验证耗时也长;VMM验证如上述的过程,是抽象级别高的验证方法,testcase采用面向对象的system verilog语言,有丰富的类库支持,能有效提高验证的功能覆盖率和验证的效率[8]。

4 结论

在越来越高的抽象层次上进行验证是验证方法学不断发展的趋势。本文以AMBA总线架构系统芯片的集成验证为例,采用VMM和DW VIP的集成验证方法。验证环境归一性强,进行简单修改即可被新项目继承,同时验证环境采用大量的脚本文件,自动化程度高,节省了人力资源和时间,可显著地提高验证的工作效率,从而缩短整个复杂SOC的研发时间。

[1]Chris Spear. SystemVerilog for Verification[M].Springer,2006,1-18.

[2]Verification Methodology Mannual[P].Synopsys,Inc,&ARM,Inc.

[3]Janick Bergeron,Eduard Cemy,Alan Hunter等著,夏宇闻等译. System Verilog验证方法学[M].北京:北京航空航天大学出版社,2007.

[4]Jinbin Hu,Xiaoguang Li.System verification based on VMM and SOPC[C].Computer Science and Information Technology (ICCSIT), 2010 3rd IEEE International Conference.2010:41-43.

[5]孙海平,丁健. 系统芯片验证方法与技术[M].北京:电子工业出版社,2005.

[6]Keaveney Martin ,McMahon Anthony,O’Keeffe Niall,et al..The development of advanced verification environments using System Verilog[C]. Signals and Systems Conference,208. (ISSC 2008). IET Irish.2008:325-330.

[7]Lu Kong,Wu-Chen Wu,Yong He,et al.. Design of SoC verification platform based on VMM methodology[C]. ASIC,2009. ASICON ’09. IEEE 8th International Conference.2009:1272-1275.

[8]Janick Bergeron.Writing Testbenches using SystemVerilog[M].Springer,2006.