流水线模数转换器研究现状

2011-01-26姜思晓须自明陈珍海

陈 飚,姜思晓,周 洁,张 键,须自明, 陈珍海

(1.中国电子科技集团公司第20研究所,西安 710068;2.中国电子技术标准化研究所,北京 100007;3.无锡职业技术学院,江苏 无锡 214000;4、中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

无线通信、高速测量仪器、数字雷达等应用系统对ADC提出了高速度、高精度、大动态范围、宽输入信号带宽、低功耗等指标要求,使得系统对高性能ADC产品的需求日益突出。目前,适用于上述应用场合的ADC实现方式为流水线结构[1-2]。然而,传统的基于运算放大器的开关电容结构流水线ADC对模拟电路和工艺要求特别高,并且其功耗水平居高不下。为降低流水线ADC对于工艺的苛刻要求,特别是让其能在纳米级CMOS工艺条件下实现,国内外各大科研机构和IC供应商均投入大量的人力物力开展相关技术的研究,近年来已发布了非常多的研究成果。

本文首先介绍了流水线ADC的基本原理、其次介绍了基于运算放大器(OTA)的开关电容实现技术及其在纳米级CMOS工艺条件下实现的主要限制,最后介绍了国际上的一些最新研究进展。

2 基本流水线ADC

基本流水线结构ADC由多级流水线构成,每一级都包含采样保持电路、低分辨率的子模数转换器、子数模转换器电路、余量和增益电路(最后一级电路没有子DAC)。图1所示为流水线结构ADC的典型系统结构图[3]。

图1 流水线ADC典型结构图

流水线ADC由时钟产生电路、延时对准寄存器阵列、数字校正电路、输入SHA、n级子级转换电路和Flash ADC电路构成。整个流水线ADC的工作受两相不交叠时钟ΦS和Φf控制,而两相不交叠时钟由外部输入时钟clk经时钟产生电路产生得到,其中,ΦS对应采样相,Φf对应放大相,图1中SHA和Stage 1~Stage n的时钟ΦS和Φf的排序就代表各级电路之间的工作状态对应关系。

图1中流水线ADC的工作过程如下:SHA在其采样相对输入信号进行采样,然后在保持相向Stage 1输出,即作为Stage 1的输入电压Vi;Stage 1中的S/H电路对Vi进行采样和保持,同时subADC对Vi信号进行量化编码,所得到的k1-bit转换结果不仅作为本级转换结果输出到延迟对准寄存器阵列,同时也作为subDAC的数字输入以产生对Vi的估计值,模拟减法电路实现Vi与subDAC产生的估计值相减,得到余差信号,在放大相此余差信号通过放大器放大2k1-1倍后,作为本级模拟输出Vo向Stage 2输出;Stage 1~Stage n的电路结构和工作过程与Stage 1相似,只是其中的subADC和subDAC为k2-bit~kn-bit而余差放大倍数为2k2-1~2kn-1;Stage n的模拟输出送到kn+1-bit的Flash ADC,实现最后一级转换,Flash ADC的转换结果也输出到延迟对准寄存器阵列。由于流水线ADC对模拟信号的逐级串行流水处理,对应于同一个模拟输入的各级电路的数字转换输出逐级延迟,这样使得对应于同一个模拟输入的各级电路数字输出能在时序上对齐后输出。

流水线结构的最大优势在于速度、精度、功耗等方面很好的平衡,而且可以工作在更低的电压条件下。与其他结构的高速ADC相比流水线结构主要的不同之处在于:(1)流水线结构每一级均有采样保持电路,所以各级可以同步处理,提高数据输出的效率。(2)级间放大器的增益大于1,后级的非线性效应会被前级的增益所衰减,降低后极电路的要求以进一步优化功耗和面积。(3)数字校正算法和冗余自校正技术可以把电路非理想因素对线性的影响减到最小,放宽对比较器失调的要求,可以采用动态比较器减小功耗。

从整个转换过程来看,流水线工作方式可以看作是串行的,但就每一步转换来看是并行工作的。因而总的最大转换速率取决于单级电路的最大速度,而且总的转换速率与流水线结构的级数没有关系。流水线型结构在所有这些改进的结构中对于精度、速度和功耗等性能指标的折中具有最大的自由度,因而在高速高精度领域获得了最广泛的应用。

3 开关电容流水线ADC及其性能限制

3.1 基于OTA的开关电容流水线ADC实现技术

目前国内外比较成熟的实现高速高精度流水线ADC 的技术是基于高增益和带宽OTA的开关电容电路技术。典型的ADC子级电路如图2所示。ADC子级电路通常采用差分形式实现,为简单起见只给出了单端实现的原理图。

可以看出子级电路由模拟开关、电容和运算放大器(OTA)构成,其中Cs为采样电容,CF为反馈电容,Vin为模拟输入,Vres为模拟输出,ΦS和Φf为两相不交叠时钟,分别控制电路工作于采样和放大相;运算放大器为了提供足够高的增益通常采用增益自举的两级运放结构。

在采样相ΦS时,采样电容Cs的左极板接输入信号Vin,采样电容Cs的右极板接地,信号Vin被采样到采样电容Cs上,同时运算放大器的输出接地;在放大相Φf时,采样电容Cs的左极板接一组DAC开关控制信号,控制Cs的底板在Φf相时选择哪种参考电压,采样电容Cs的右极板连接到反馈电容CF的一端,反馈电容CF的另一端连接到运算放大器的输出端形成一个负反馈,采样电容Cs上所存储的经过DAC加减的余量信号就会被转移到反馈电容CF上,同时按一定的比例被放大得到本级处理之后的余量信号Vres。

图2 典型开关电容ADC子级电路

目前该技术已经非常成熟,采用该技术实现的精度达14~16位、采样速度超过100MHz、SFDR超高90dB的中频采样流水线ADC报道已经很多。如ADI公司的Ahmed M. A. Ali等人早在2006年就发布了一种10MHz输入条件下SFDR达100dB的14位125MSPS中频采样流水线ADC[4];2010年他们又发布了一种16位250MSPS中频采样流水线ADC,该ADC在250MHz全速采样条件下对于10MHz输入信号SFDR同样达100dB[5], ADI公司的Siddharth Devarajan等人还在2009年发布了一种采用CMOS工艺实现的16位125MSPS中频采样流水线ADC,该ADC在125MHz全速采样条件下对于30MHz输入信号SFDR达96dB[6]。

3.2 工艺缩减对开关电容流水线ADC性能的限制

随着CMOS工艺技术特征尺寸不断缩减,高信噪比(SNR)模拟电路的实现却越来越困难[7]。一个全差分采样保持电路的信噪比为:

其中,C为采样电容,Vpp为输入差分正弦信号的最大幅值,k为波尔兹曼常数,T为绝对温度。由于SNR与输入信号的最大幅值的平方成正比,对于较低的电源电压,当输入信号摆幅减小时,为达到相同的信噪比必须增大采样电容。这样一来,要达到相同的处理速度就必须增加电路的功耗;而要保持相同的功耗,就会降低电路的输入带宽和处理速度。

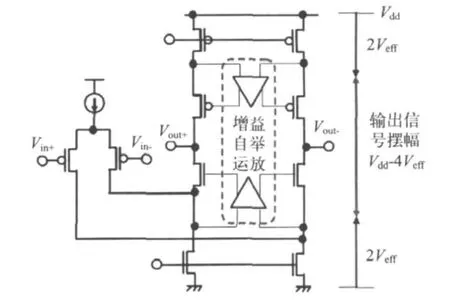

开关电容流水线结构ADC需要使用大量的高增益、宽带宽OTA来保证电路的精度。而在纳米级CMOS工艺条件下实现该种高性能OTA将会是非常困难的。首先是低电源电压的限制。图3为传统开关电容流水线ADC经常使用的增益自举(Gainboost)折叠式共源共栅运算放大器。为达到所需要的高增益,采用4个MOS管堆栈起来的共源共栅结构是必须的;并且为达到足够的带宽,辅助的增益自举运放也是必须的。

图3 增益自举折叠式共源共栅运算放大器

为使MOS管工作在饱和区,它的漏源电压Vds的最小值为Veff(=Vgs-VT),而通常Veff的取值为0.15V~0.2V,这样OTA输出信号的摆幅为Vsw=Vdd-4Veff≈Vdd-0.7V。对于纳米级CMOS工艺,如果我们选择电源电压Vdd=1V,那么信号摆幅仅为0.3V,对于许多运用来说,0.3V的信号摆幅实在太少。因此低电压条件下该类高带宽高增益OTA的设计是有瓶颈限制的。

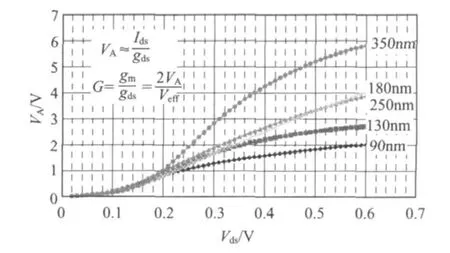

除电源电压以外,该类OTA实现的另外一个限制是MOS管的漏极输出电阻随工艺尺寸的缩减而减小。图4为几种工艺条件下MOS管的本征跨导Gi随电源电压VA以及漏源电压Vds变化的曲线[8]。可以看出,90nm条件下NMOS管的本征跨导Gi仅为0.35μ m条件下的三分之一。

图4 几种工艺条件下MOS管的本征跨导对比

因此,在纳米级CMOS工艺条件下若采用3.1节所述的基本开关电容技术来实现高速高精度的流水ADC将会非常困难,原因就在于高增益带宽OTA难以实现。而要克服基本开关电容结构ADC的性能限制,最直接的方法就是采用其他技术降低运算放大器增益和带宽要求或者彻底不使用这种高增益和超宽带宽的OTA。

4 流水线ADC研究最新进展

由于基于OTA的开关电容技术对于工艺的苛刻要求以及功耗方面的瓶颈限制,近年来国内外很多研究机构针对该问题进行研究,提出了许多流水线ADC实现的新技术和改进措施,其中基本方向可以分为几大类:

(1)数字校准辅助的开关电容技术,通过采用数字技术进行纠错补偿以降低开关电容技术中OTA的增益要求[9];

(2)采用基于比较器的新结构开关电容技术[10],省略OTA的使用,最大限度降低了ADC功耗。

4.1 数字辅助的开关电容技术

数字辅助模拟集成电路的研究是目前国际CMOS集成电路研究领域最活跃的课题之一。集成电路工艺不断进步,特征尺寸越来越小,电源电压越来越低,MOS晶体管的本征增益随之降低,模拟电路可工作的电压空间越来越小,共源共栅这样的结构已经难以在很低的电压下应用了,模拟电路的设计受到了前所未有的挑战。与此相反,数字集成电路从工艺进步中获得的好处是显而易见的,数字电路的性能指数提高。因此在设计高性能模拟电路时,可以另辟蹊径,利用性能越来越强大的数字电路对模拟电路设计中存在的误差进行校准。

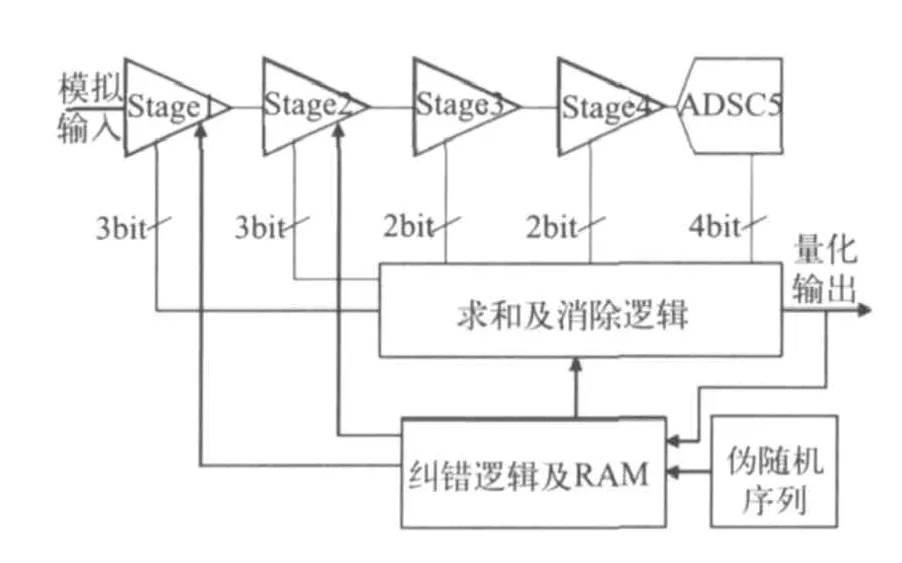

基于开关电容技术的流水线结构ADC需要使用大量的高增益、宽带宽运算放大器来保证电路的精度和速度。通过应用新颖数字算法进行纠错补偿可以降低OTA的高增益要求,并且在先进工艺条件下高带宽低增益运放的实现还是相对容易的。2006年,Peter Bogner、Franz Kuttner和Claus Kropf 等人在ISSCC上发表了一种使用0.13 μm CMOS工艺实现的功耗仅为224mW的14-bit 100MSPS 流水线ADC[9]。

该ADC通过内建的新颖数字算法对OTA低增益所带来的误差进行校准。整个电路一共5级,该ADC在传统结构的基础上加入了一个纠错RAM电路,该RAM根据ADC的输出信号以及片上产生的一个“伪随机”序列(Pseudo Random Sequence)对ADC前两级子级电路进行纠错。该ADC采用130nm CMOS工艺进行设计,工作电源电压仅为1.5V。ADC电路实现仍然采用开关电容电路,但是所使用的OTA的增益仅为44dB,有效克服了纳米级CMOS工艺条件下宽带宽、高增益OTA设计困难带来的限制。

图5 基于数字校准技术的流水线ADC结构框图

4.2 基于比较器的开关电容技术

基于比较器的开关电容技术就是近几年提出的一种省去OTA使用的一种开关电容电路技术。基于OTA的开关电容电路的电压传输和处理精度主要通过保证OTA输入端和输出端的“虚地”来实现;基于比较器的开关电容技术则通过使用真正的电源“地”而不是使用OTA的“虚地”,实现开关电容电路。该技术同样可以用于实现流水线ADC。2006年MIT的T. Sepke、J. K. Fiorenza和 C. G. Sodini等人提出了一种基于比较器控制电流源的流水线ADC结构,通过使用比较器控制电流源的方式实现真正电源“地”的使用[10]。使用该技术的一种10-bit速度达8MSPS的流水线ADC已经实现,整个电路的功耗仅为2.5mW。

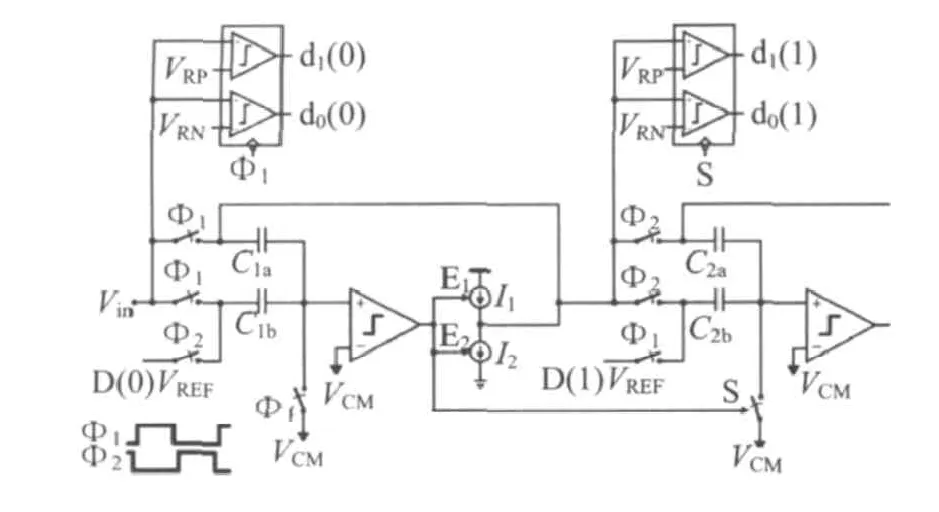

图6所示即为基于比较器的1.5位/级开关电容流水线ADC电路的具体实现。电路基本结构和基于OTA的开关电容电路类似,不同之处在于采用比较器控制的电流源代替OTA。在采样相Φ1时,电路工作和基于OTA的开关电容电路类似,电容C1a和C1b的左极板接输入信号Vin,右极板接交流地,信号Vin被采样到电容C1a和C1b上;在放大相Φ2时(如图7所示),电路首先控制E2打开电流源I2,Vo电压被拉到地,这会将X点电压Vx拉低到交流地(Vcm)以下,随后电路控制E1打开电流源I1,同时电容C1a的左极板接将会连接到加减基准电压,然后Vo电压被慢慢抬高,同时将X点电压Vx慢慢抬升直到其电压大于交流地(Vcm),此时比较器的状态发生翻转,放大相电荷转移过程结束,比较器的状态保持直到时钟相位改变,放大相结束。

比较器控制电流源的方式完全类似于一个运算放大器。由于比较器的工作电压可以非常低,该结构ADC可以工作在0.5V电源电压以下。因此,采用该技术可以极大降低ADC电路功耗,同时适合于在纳米级CMOS工艺条件下实现。

图6 基于比较器的开关电容电路实现

图7 放大相工作原理

5 总结

基于OTA的开关电容技术由于需要使用高增益宽带宽OTA来保证流水线ADC的速度和精度,因此该类ADC对模拟电路和工艺要求特别高,难以在纳米级CMOS工艺条件下实现;并且相同精度和工艺条件下其功耗水平随速度提高而显著提高,功耗限制非常突出。

目前国内外各研究机构已经提出了多种改进措施,主要有:数字校准辅助的开关电容技术、开环运放技术、基于比较器的开关电容技术。数字校准辅助的开关电容技术通过数字校准技术降低OTA的增益,从而使得ADC可以在纳米级CMOS条件下实现;基于比较器的开关电容技术则直接省略OTA的使用,使得ADC可以非常容易地在纳米级CMOS条件下实现,同时最大限度降低了功耗。

[1]Stephen H. Lewis, Paul R. Gray. A Pipelined 5-Msample/s 9-bit Analog-to-Digital Convert [J]. IEEE J. Solid-State Circuits, 1987, 22(12): 954-961.

[2]D.Cline,P.R.Gray. A Power optimizied 13-b 5Msample/s Pipelined analog-to-digital converter in 1.2 μm CMOS[J]. IEEE J.Solid-State Circuits, 1996, 31(3):294-303.

[3]李福乐. 适宜于系统集成的高速高精度模数转换器电路设计技术研究[D].北京:清华大学博士论文,2003.

[4]Ahmed M.A. Ali, Chris Dillon,Robert Sneed,,et. al, A 14-bit 125 MS/s IF/RF Sampling Pipelined ADC With 100 dB SFDR and 50 fs Jitter[J]. IEEE J.Solid-State Circuits,2006,41(8):1846-1855.

[5]Ahmed M.A. Ali, Andy Morgan, Chris Dillon,et al.. A 16b 250MS/s IF-Sampling Pipelined A/D Converter with Background Calibration[C].ISSCC 2010, Dig.Tech. Papers, 2010:292-294.

[6]Siddharth Devarajan, Larry Singer, Dan Kelly, et al.. A 16b 125MS/s 385mW 78.7dB SNR CMOS Pipeline ADC[C].ISSCC 2009, Dig.Tech. Papers, 2009: 86-88.

[7]Annema A. J., Nauta B., Langevelde R., et al.. Analog circuits in ultra-deep- Submicron CMOS[J]. IEEE J.Solid-State Circuits, 2005, 40(1):132-144.

[8]Akira Matsuzawa. Trends in high speed ADC design[C].ASICON’07, Dig.Tech. Papers, 2007:245-248.

[9]Peter Bogner, Franz Kuttner, Claus Kropf, et al.. A 14b 100MS/s Digitally Self-Calibrated Pipelined ADC in 0.13 μm CMOS[C]. ISSCC 2006, Dig.Tech. Papers, 2006: 224-225.

[10]Sepke T., Fiorenza J. K., Sodini C. G.,et al.. Comparator based switched-capacitor circuits for scaled CMOS technolgies[C]. ISSCC 2006, Dig of Tech Papers, 2006:574-575.