基于DSP的4/πQPSK调制解调器的设计

2011-01-24刘艳萍李妹苓

张 玲,刘艳萍,李妹苓,徐 莉

(河北工学大学 信息工程学院,天津 300401)

QPSK数字调制技术,具有频谱利用率高、频谱特性好、抗干扰性能强、传输速率快等突出特点,目前已经广泛应用于无线通信中。由于QPSK是一种恒包络调制,其信号的平均功率是恒定的,因此不受幅度衰减的影响,幅度上的失真不会使QPSK产生误码,它的这一特性使得QPSK成为卫星数字电视(DVB-S)广播调制标准所采用的调制方式[1]。

近年来,数字信号处理(DSP)技术的发展十分迅速,许多从前必须使用硬件电路实现的信号处理过程,现在已经逐渐由软件实现的DSP算法所取代,而且功能更强大,性能更可靠,接口更通用,互连更灵活。DSP技术已经渗透到数字通信领域的各个环节,如编码译码、数字滤波、调制解调、时钟同步、载波同步等。事实表明,DSP技术在通信和计算机应用领域起着越来越重要的作用。可见如果将两者相结合,利用DSP强大的数字信号处理功能可以更高效地实现QPSK的调制解调[2]。

1 调制解调器的关键技术

在数字通信系统中,定时同步是一个非常重要的问题。通信系统能否有效可靠地工作,很大程度上依赖于同步技术的优劣。最大平均功率定时算法是一种直接从时域提取定时误差信息的较新算法,对接收信号采样序列作平方变换之后,不需要采用滤波器提取时钟,只用最简单的算术运算就可以得到时延的判决测度—平均功率。计算量小,电路简单,能适应很高的数据传输率[3]。

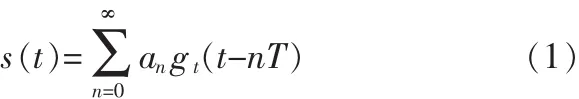

数字调制技术的等效低通发射信号为

其中T为符号周期,{an}代表离散的信息(复值)符号序列,gt(t)为成形脉冲,其带限频率响应为 Gt(f),且当|f|>W 时,满足Gt(f)=O。 假设信道对信号引入一个幅度衰减因子 ρ(t),一个相位偏移 θ(t)和一个信道时延 ε(t)T,则接收到的 QPSK信号等效低通信号为:

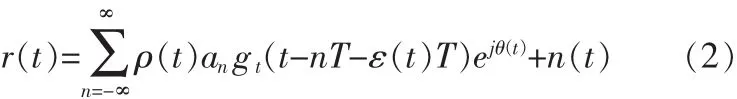

其中T为已知的符号周期,n(t)是高斯白噪声,其单边功率谱密度为n0,定时提取就是估计出ε(t)的值。因为在实际系统中,通常采用AGC电路可以使得衰减因子ρ(t)得以补偿或保持某个恒定值ρ,ε(t)随时间的变化相对于符号速率是非常缓慢的,可以将接收到的信号作分段统计处理,对每一段(如观察长度为L个符号)而言,ε(t)可以视为常量 ε。这样定时恢复的问题就归结为逐段估计定时常量ε并逐段更新的问题。

设接收滤波器脉冲响应为gr(t),则接收信号经滤波后成为:

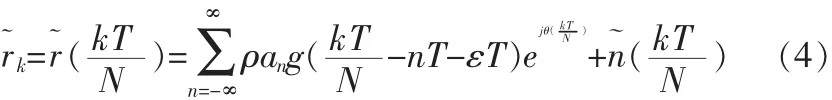

经采样后得:

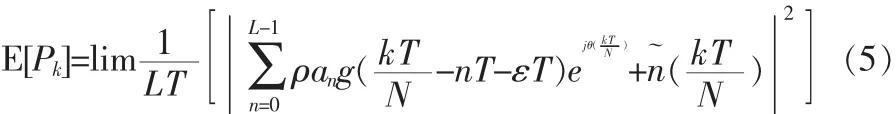

对L个符号N个样点中的第k个样点构成k时刻的采样信号序列,先平方,再计算该平方序列的平均值。定义第k时刻的采样信号序列的平均功率为:

{an}可以认为是均值为0的元素间相互独立的平稳序列,则接收的信号可以认为是一个零均值的周期平稳过程,其平均功率为=。(t)是接收滤波器对加性高斯白噪声 n(t)的响应,也是一个高斯噪声,均值为零,采用平方根升余弦滤波器,t)的平均功率为δ2。因为符号与噪声相互独立,且噪声均值为0,所以式(5)中交叉项为O。当观察区间L足够长时,可在L个符号内计算平均功率分布,结果为:

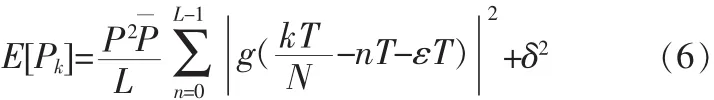

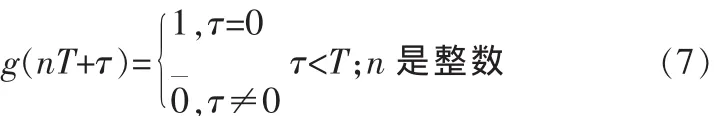

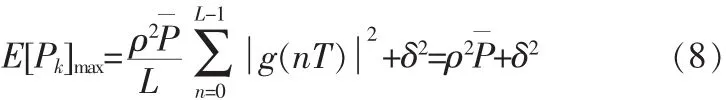

式(6)说明功率与载波相位无关。如果接收滤波器采用匹配滤波器,总的脉冲响应满足Nyquist第一准则,采样点不失真,即

所以最佳采样时刻就是 g(T)=g(nT)的时刻,有 kopt=εN,于是时延估计与最佳采样时刻估计的关系可以写为:

用不同的采样时刻k带入(6)式计算对应不同采样序列的平均功率,从所有的N种采样时刻的平均功率中,选择最大的平均功率对应的采样时刻作为最佳采样时刻,这就是文中所讨论的最大平均功率定时同步算法[4-5]。

2 系统硬件设计

系统硬件设计主要用到两个芯片,一个是DSP芯片TMS320C5409,该芯片采用改进的哈佛结构,具有高度并行性的算术逻辑单元ALU、专用硬件逻辑、片内存储器、片内外设和高度专业化的指令集,使芯片速度更高,操作更灵活,该芯片有功耗小、成本低等特点,被广泛应用于移动通信、软件无线电等领域。另一个是A/D D/A芯片TLC320AD50C芯片,该芯片使用过采样的Σ-Δ技术,提供从数字至模拟(D/A)和模拟至数字(A/D)的高分辨率低速信号转换。AD50是TI公司生产的一个16位、音频范围(采样频率为2~22.05 kHz)、内含抗混叠滤波器和重构滤波器的模拟接口芯片,它有一个能与许多DSP芯片相连的同步串行通信接口。

系统的硬件原理图如图1所示,本方案中,调制解调器硬件以TMS320C5409DSP为核心,包括A/D转换、D/A转换,存储器模块等[6-7]。

图1 系统硬件原理图Fig.1 System hardware diagram

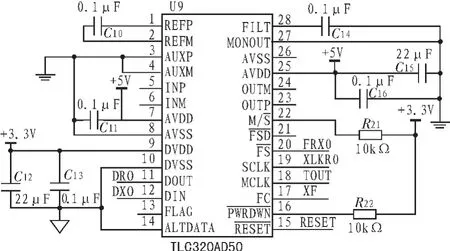

TMS320C5409与TLC320AD50C的硬件连接电路图如图2所示,图中AD50的时钟信号由C5409的定时器0的输出提供,时钟频率可以通过修改定时器0的设置而改变。AD50的FC引脚连接到C5409的XF(通用I/O引脚),用于控制第二次串行通信。AD50的DIN(数据输入引脚)和DOUT(数据输出引脚)分别接C5409缓冲串口的DX0和DR0引脚。AD50的SCLK(移位时钟输出)连接C5409的CLKR0(缓冲串口0的接收时钟引脚),帧同步信号FS连接C5409缓冲串口0的 FRX0。

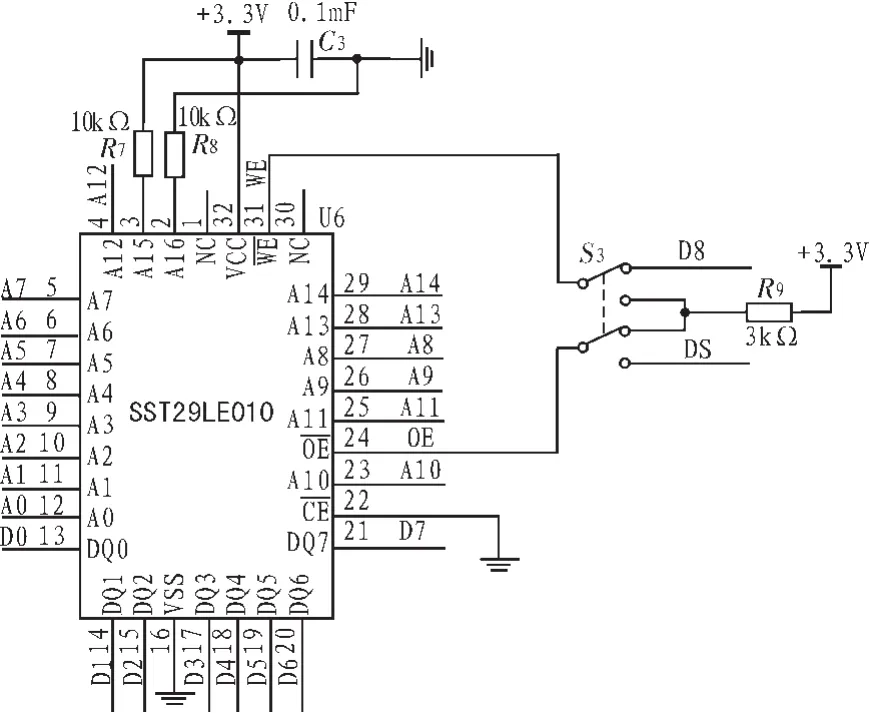

C5409与FLASH的硬件连接电路图如图3所示,闪速存储器SST29LE010连接到C5409作为其外部程序存储器,供DSP上电时在BOOTLOAD中使用。其地址和数据总线连接到C5409外部总线,CE直接接地,使FLASH一直处于选通状态。C5409的引脚D8用于控制FLASH的写使能,当引脚D8为低电平时,可对FLASH编程和擦除;为防止误写,WE一般被设置为高电平。而与C5409的DS相连的OE,只有设置为低电平时才有效,但一般被设置为高电平,以保护FLASH的芯片。

图2 C5409与AD50C的硬件连接电路图Fig.2 C5409 hardware connection diagram with AD50C

电路采用了双刀双置开关,当开关置下方时(实线表示的地方),FLASH的OE与DSP的DS相连,WE置高,可上电读FLASH;当开关置上方时(虚线表示),OE置高,WE与DSP的D8相连,为写操作。

图3 C5409与FLASH的硬件连接电路图Fig.3 C5409 hardware connection diagram with FLASH

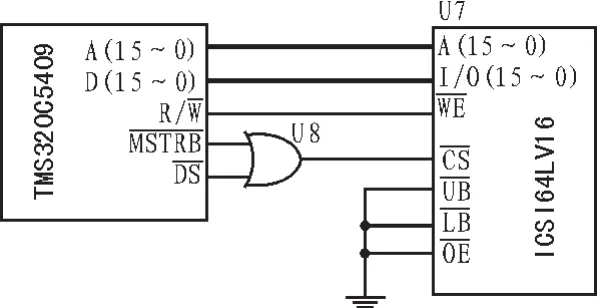

C5409与SRAM的硬件连接电路图如图4所示,ICSI64LV16连接到C5409作为其外部数据存储器,ICSI64LV16分别有16条地址和数据线,控制线包括片选CE、读选通OE、写允许WE、高位字节选通UB和低字节选通LB。因为ICSI64LV16的写允许有一个单独的控制端WE,低电平有效,与C5409的读/写控制端R/W时序逻辑对应,所以R/W与WE直接相连。读允许OE直接接地,LB是低字节(bit7~0)R/W 控制,UB 是高字节(bit15~8)R/W 控制。 字读/写(bit15~0)时,这两个引脚均为低电平。

图4 C5409与SRAM的硬件连接电路图Fig.4 C5409 hardware connection with the SRAM

3 系统软件设计

QPSK是一种调相技术,它规定了4种载波相位。QPSK中每次调制可传输2个信息比特,这4个相位通常相隔π/2 rad,可以是 0,π/2,π 和 3π/2,或者是 π/4,3π/4,5π/4 和 7π/4,它们分别代表对应的数字信息00,10,11和01,由于π/4QPSK调制系统输出信号相位不会出现180°跳变,所以本设计采用π/4相位方式。解调器根据星座图及接收到的载波信号的相位来判断发送端发送的信息比特。

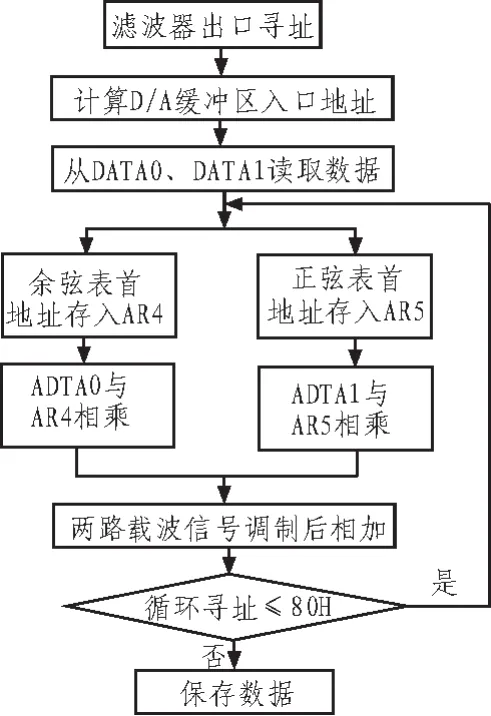

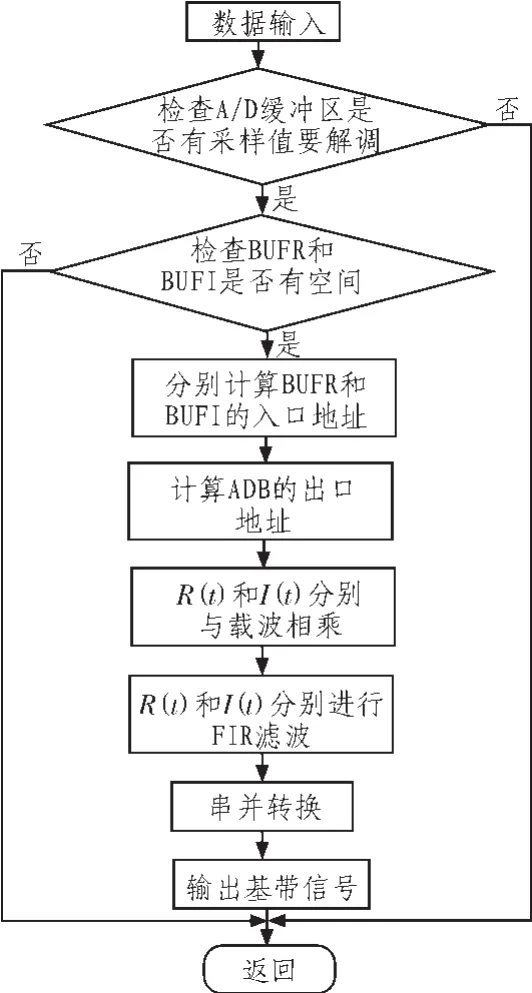

图5和图6分别为π/4QPSK调制和π/4QPSK解调的软件流程图。

图5 调制子程序流程图Fig.5 Flow chart of modulation subroutine

图6 解调子程序流程图Fig.6 Flow chart of demodulation subroutine

QPSK调制的主程序应该包括数据输入、低通滤波和调制3个部分。由于数据输入和低通滤波子程序相对简单,这里重点设计了调制子程序部分。设载波速率为48 kHz,对滤波器送来的数据进调制,经过处理后的数据放入D/A缓冲区,缓冲区满程序终止。解调子程序前先采用最大平均功率定时同步算法找出最佳采样时刻,解调子程序从A/D缓冲区读入16b数据,经过处理后,数据输出至BUFR和BUFI缓冲区,形式为16b数据。

4 结 论

文中论述了一种4/πQPSK调制解调器的DSP实现方案,该方案在DSP的仿真软件CCS中已经进行了仿真验证,证明能够实现数字信号的QPSK调制解调。其中,最大平均功率定时同步算法满足了人们对定时同步的运算速度和准确度方面的要求。该系统具有抗干扰能力强、功耗低、集成度高、软件可移植性强等特点,可广泛应用于软件无线电、卫星通信等多种领域。

[1]刘敏.基于软件无线电的π/4-QPSK与GMSK调制系统实现[J].南京航空航天大学学报,2003(11):33-36.LIU Min.Π/4-QPSK and GMSK modulation based on software radio system [J].Journal of Nanjing University of Aeronautics&Astronautics,2003(11):33-36

[2]乔瑞萍,崔涛,张芳娟.TMS320C54xDSP原理及应用[M].西安:西安电子科技大学出版社,2005.

[3]周得锁.星上多载波QPSK数字化解调关键技术研究[D].西安:西安电子科技大学,2000:24-69.

[4]郭志勇.π/4QPSK调制原理分析[J].信息工程大学学报,2006,7(3):255-256.GUO Zhi-yong.Theπ/4QPSK modulation principle analysis[J].Journal of Information EngineeringUniversity,2006,7 (3):255-256.

[5]万云芳,冯祝.数字卫星电视信号的QPSK调制[J].中国有线电视,2004(16):60-62.WAN Yun-fang,FENG Zhu.The QPSK modulation of digital satellite TV signals[J].China Cable TV,2004(16):60-62.

[6]Hogenauer B.An economical class of digital filters for decimation and interpolation[J].IEEE Trans.on Acoust.Speech, Signal Processing,1981,29(2):155-162.

[7]HU Xiao-bo,Harber R G,Bass SC.Expanding the range of convergence of the CORDIC algorithm[J].IEEE Trans.on Computers,1991,40(1):13-20.