基于衬底驱动技术的模拟电路设计*

2011-01-22张长青

张长青,朱 猛

(信阳农业高等专科学校,河南 信阳 464000)

基于衬底驱动技术的模拟电路设计*

张长青,朱 猛

(信阳农业高等专科学校,河南 信阳 464000)

在进行低电压低功耗模拟电路设计的众多技术中,衬底驱动(BD)技术由于设计简单和使用传统MOS工艺实现的特点,而被很多的设计所采用。本文利用这一原理,在标准CMOS工艺和±0.7 V电源电压前提下设计低电压低功耗标准模块,最后在TSMC0.25 μm CMOS工艺模型下,用Spice模拟器验证了模拟仿真结果。

衬底驱动MOS;电流镜;跨导运算放大器;电流差分跨导放大器

随着亚微米、深亚微米技术和系统芯片(SOC)技术的日益成熟,功耗已经成为模拟电路设计中首要考虑的问题,低电压低功耗集成电路设计渐渐成为主流。因为MOS晶体管的衬底或者与源极相连,或者连接到VDD或VSS,所以经常被用作一个三端设备。由于未来CMOS技术的阈值电压并不会远低于现有标准,于是采用衬底驱动技术进行模拟电路设计就成为较好的解决方案[1]。衬底驱动技术的原理是:在栅极和源极之间加上足够大的固定电压,以形成反型层,输入信号加在衬底和源极之间,这样阈值电压就可以减小或从信号通路上得以避开。衬底驱动MOS晶体管的原理类似于结型场效应晶体管,也就是一个耗尽型器件,它可以工作在负、零、甚至略微正偏压条件下[2]。由于衬底电压影响与反型层(即导电沟道)相连的耗尽层厚度,通过MOS晶体管的体效应改变衬底电压就能调制漏极电流。

应用衬底驱动技术建立一些基本的模拟电路标准模块,通过举例来说明衬底驱动技术在模拟电路设计中的使用。

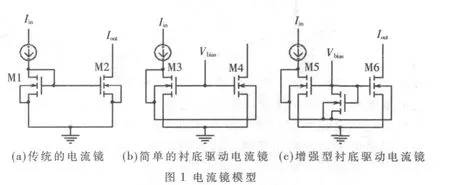

1 简单和增强型衬底驱动电流镜

简单的衬底驱动电流镜结构即本文提出的低电压电流镜如图1(b)所示,这种电流镜用衬底-漏极连接代替传统简单电流镜结构里的栅极-漏极连接[3]。当然,M3和M4通过衬底连接而不是栅极,而N型MOS管M3和M4的栅极应施加一个合适的正向偏置电压。

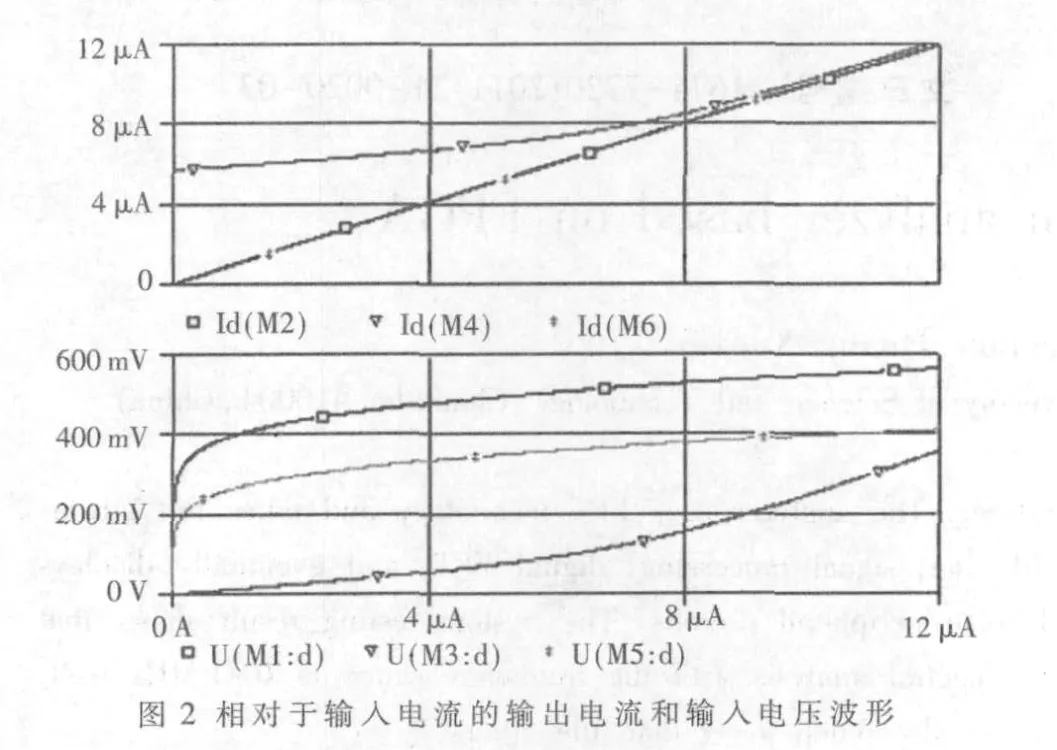

这种简单衬底驱动电流镜的缺陷是输入输出电流呈非线性,这是由于在栅极驱动电流镜中输出晶体管M4工作在饱和状态[4]。为了解决这个问题,使用了一种替代配置,如图 1(c)。晶体管 M7被作为一个二极管,连接在M5和M6这两个晶体管的栅极和衬底之间。M7被当做简单的电压源使用,当输入电流Iin为零时晶体管M6工作在饱和状态而M5则不会。一旦输入电流开始增大时,增强型衬底驱动电流镜中晶体管M5就会比简单衬底驱动电流镜中的M3早进入饱和状态,因此具有更好的线性度。由于这样连接可以同时驱动栅极和衬底端,流过M7的偏置电流Ibias被计入输入Iin。为了避免在输入电流和输出电流之间产生额外的偏移,偏置电流Ibias必须远远小于输入电流Iin。图2是图1中电流镜模型的仿真结果,它表明衬底驱动增强型电流镜的输入输出传输特性比简单的衬底驱动电流镜具有更好的线性度,其线性度几乎和栅极驱动电流镜一样。从图2中同样可以看出简单的衬底驱动电流镜和增强型电流镜的输入电压远低于传统的栅极驱动电流镜。

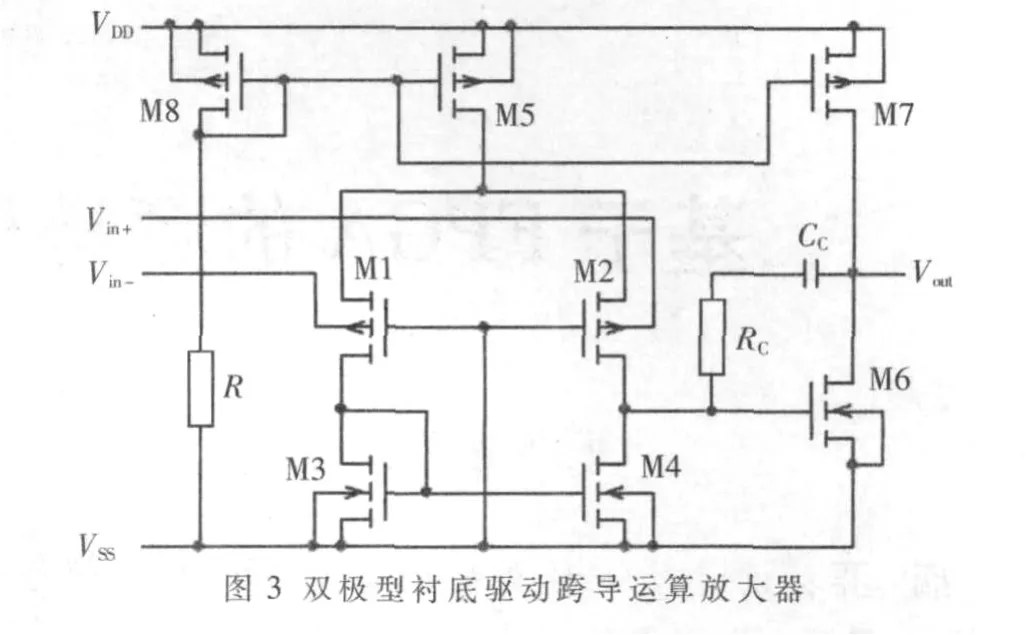

2 衬底驱动跨导运算放大器

基于衬底驱动技术的跨导运算放大器的结构如图3所示,由两级构成[5-6],第一极由衬底驱动差分级构成,此差分级以PMOS设备 M1、M2作为输入,电流镜M3、M4作为主动负载;第二极是一个简单的CMOS到相级,它以M6作为驱动管M7作为主动负载。依靠补偿电容Cc和电阻Rc差分级的输出端和输入端连接在一起,在第二级中补偿电容实际作为密勒电容使用。

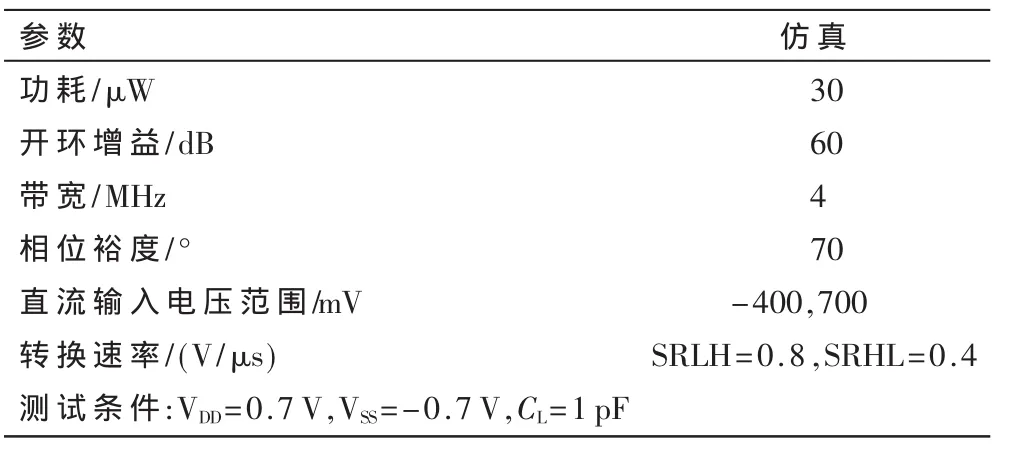

通过提供足够的栅源电压值使场效应管导通,衬底驱动MOS晶体管即以耗尽型器件的原理工作,通过施加在衬底端的输入电压调制流经晶体管的电流,完成采用衬底驱动输入晶体管的跨导运算放大器设计,电路结构如图3所示,仿真结果如表1所示。

3 衬底驱动电流差分跨导放大器

表1 低电压低功耗衬底驱动跨导运算放大器的仿真结果

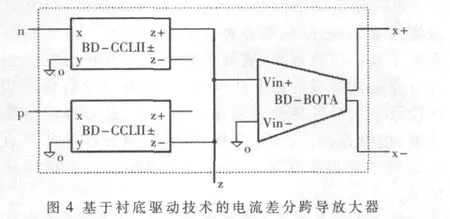

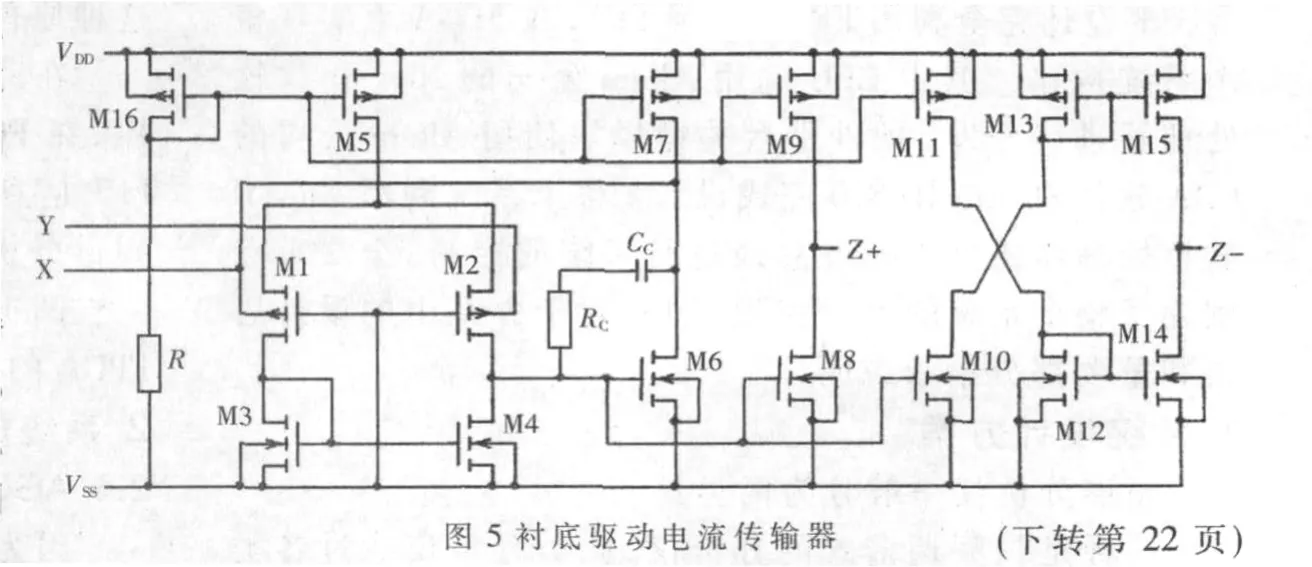

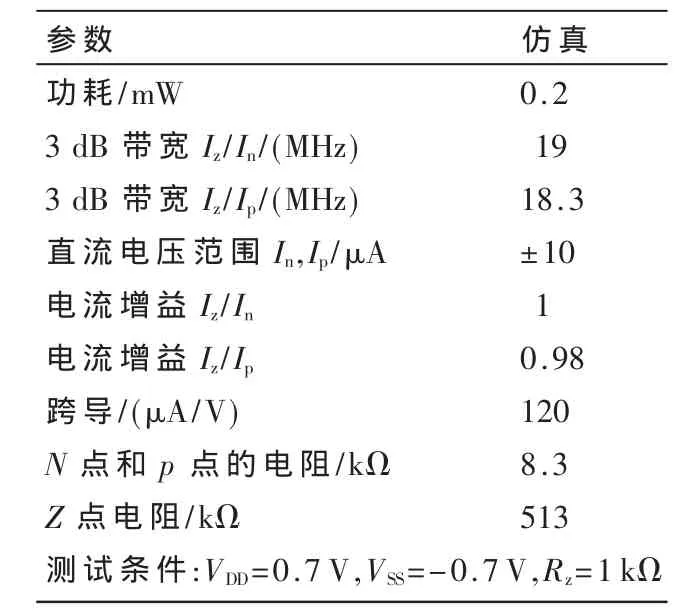

电流差分跨导放大器是一种新型主动型器件,是基于衬底驱动的电流差分跨导放大器[7]。如图4所示,它适合设计大规模集成电路模块。由两个图5所示衬底驱动电流传输器和一个图3所示衬底驱动跨导运算放大器(双输出DO-跨导运算放大器)构成实现。电流传输器连接作为电流差分单元,电流流入上面电流传输器的Z+端,电流Ip流入下面电流传输器的Z-端但与Z+端电流方向相反。这就解释了电流差分跨导放大器流进Z端的电流是由差分电流Ip和In提供的。电路及其仿真结果如图4和表2所示。

表2 基于衬底驱动技术的低电压低功耗电流差分跨导放大器仿真

本文研究了衬底驱动MOS管技术和运用这一技术进行低电压低功耗模拟电路设计的方法,并且运用这种技术设计低电压低功耗衬底驱动跨导运算放大器和电流差分跨导放大器。这些模型要么是新型器件,例如衬底驱动电流差分跨导放大器,要么就是仿真结果非常理想,例如衬底驱动跨导运算放大器。经过仿真分析,得出衬底驱动晶体管的优点是:电路的功率消耗比较低;设计简单和可接受的电路特性;能够避开阈值电压要求的耗尽特性;传统的前端门可用于调制衬底驱动MOS晶体管。衬底驱动晶体管的缺点是:(1)其跨导远小于传统的栅极驱动MOS管,这可能会导致跨导运算放大器的增益带宽乘积偏低;(2)其电极与工艺相关,一个CMOS工艺的 P(N)阱,只有 N(P)的沟道的衬底驱动 MOS管是有效的,这可能限制了其应用。例如一个轨对轨衬底驱动运算放大器需要双阱CMOS工艺去实现,这个过程比较昂贵,需要更大的芯片面积而且它的性能匹配比单阱CMOS工艺更差;易于开启的衬底沟道PN结,将可能导致闩锁问题。

[1]杨银堂,李娅妮,朱樟明.一种 0.8 V衬底驱动轨对轨运算放大器设计[J].固体电子学研究与进展,2009(03):439-443.

[2]窦建华,郭铭铭,潘敏.一种基于衬底偏置技术的低压低功耗运算放大器设计[J].仪表技术,2008(5):10-12.

[3]ZHU Z,MO J,YANG Y.A low voltage Bulk-driving PMOS cascode current mirror[J].in Solid-State and Integrated-Circuit Technology,2008:2008-2011.

[4]朱冬勇,基于衬底驱动技术的超低压、超低功耗CMOS模拟集成电路设计[D].西安,西安电子科技大学,2008.

[5]李亮,陈珍海.基于弱反型的宽工作电压OTA研究设计[J].中国电子科学研究院学报,2010,5(1):32-35.

[6]RAIKOS G,VLASSIS S.0.8 V bulk-driven operational amplifier.Analog Integrated Circuits and Signal Processing,2009.

[7]BIOLEK D.CDTA——building block for current-mode analog signal processing[C].in proceedings of the ECCTD’03,Krakow,Poland,2003:397-400.

Analog circuit design based on the bulk-driven technique

Zhang Changqing,Zhu Meng

(Xinyang Agriculcural College,Xinyang 464000,China)

Among many techniques used for the design of LV-LP analog circuits,the Bulk-driven principle offers a promising route towards this design for many aspects mainly the simplicity and using the conventional MOS technology to implement these designs.This paper is devoted to the Bulk-driven(BD)principle and utilizing this principle to design LV LP building blocks in standard CMOS processes and supply voltage±0.7 V.The simulation results have been carried out by the Spice simulator using the 0.25 μm CMOS technology from TSMC.

Bulk-driven MOS;CM;OTA;CDTA

TN402

A

1674-7720(2011)24-0018-02

国家自然科学基金项目(60801042)

2011-10-11)

张长青,男,1972年生,讲师,硕士,主要研究方向:高速电路分析,集成电路技术,信号处理研究。